# AN-228 APPLICATION NOTE

ONE TECHNOLOGY WAY . P.O. BOX 9106 . NORWOOD, MASSACHUSETTS 02062-9106 . 617/329-4700

# **Evaluation Board for the AD7884 16-Bit A/D Converter**

by Mike Curtin

#### INTRODUCTION

This application note describes the evaluation board for the AD7884 16-bit A/D converter. This is a 16-bit monolithic analog-to-digital converter with internal sample-and-hold and a conversion time of 5.3  $\mu s$ . The throughput rate is 166 kSPS. It uses a 2-pass flash architecture to achieve this speed and throughput. It has both ac and dc specifications. Integral Linearity Error is  $\pm 0.006\%$  FSR and the Signal to (Noise + Distortion) Ratio is 84 dB. Its fast 16-bit parallel output interface is compatible with both DSPs (TMS320C25, ADSP-2101, DSP56000) and general purpose processors (MC68000,

80286, etc.). Full data on the converter is in the AD7884/AD7885 data sheet from Analog Devices. This should be consulted in conjunction with the application note when using the evaluation board.

The board operates from +15 and -15 volt power supplies. On-board components include the reference and op amp circuitry necessary for the analog front-end and output latches for interfacing to a 16-bit processor bus.

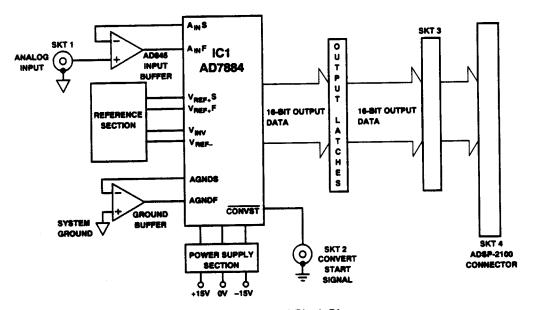

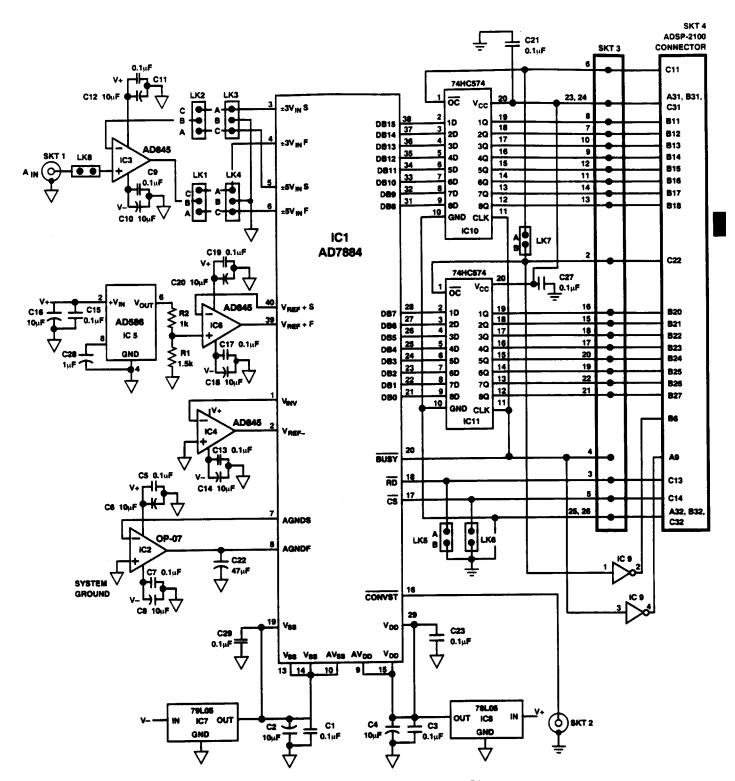

A full circuit diagram for the AD7884 board is shown in Figure 3.

Figure 1. Evaluation Board Block Diagram

#### LINK OPTIONS

The evaluation board has several link options available and these are summarized in Table I below.

Table I. Link Options

| Link No. | Function                                                                                                                                                                                                                           |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| LK1-LK4  | Links 1-4 enable the user to select either the ±3 volt input range or the ±5 volt input range.                                                                                                                                     |  |  |  |

| LK5      | This allows RD to be tied permanently low.                                                                                                                                                                                         |  |  |  |

| LK6      | This allows CS to be tied permanently low.                                                                                                                                                                                         |  |  |  |

| LK7      | This link allows the two output latches to be enabled together (LK7 inserted) or separately (LK7 removed).                                                                                                                         |  |  |  |

| LK8      | LK8 breaks the A <sub>IN</sub> line so that the user can easily route it to extra signal conditioning such as antialias filtering or an extra gain stage. The board has a grid section where this external circuitry can be built. |  |  |  |

# **POWER SUPPLIES, GROUNDING AND DECOUPLING**

The board is powered from a  $\pm 5$  V supply. These supplies drive two 5 V regulators (IC7 and IC8) which produce the  $\pm 5$  V required for the AD7884. The AD7884 has one AV<sub>DD</sub> pin and two V<sub>DD</sub> pins. These are all driven from the same  $\pm 5$  V supply. The AV<sub>DD</sub> pin is decoupled to signal ground with a 10  $\mu$ F tantalum and a 0.1  $\mu$ F ceramic capacitor. Both V<sub>DD</sub> pins are decoupled with 0.1  $\mu$ F capacitors only. The same decoupling arrangement is used for the negative supply pins. AV<sub>SS</sub> is decoupled to signal ground with 10  $\mu$ F and 0.1  $\mu$ F while each of the V<sub>SS</sub> pins is decoupled with 0.1  $\mu$ F only.

The  $\pm 15$  V supplies also drive the analog front-end circuitry which includes the AD586 reference and the op amps A1–A4. They are decoupled to signal ground with 10  $\mu$ F tantalum and 0.1  $\mu$ F ceramic disc capacitors. Power for the digital section of the board (IC9, IC10 and IC11) should be applied at either A31, B31 or C31 of the Eurocard connector, SKT 4, or at Pin 23 of SKT 3. The digital supply is routed separately from the analog section, and they are not joined anywhere on the board.

The evaluation board uses extensive ground planing to minimize any high frequency noise interference. The ground planing for the analog section is kept separate from that for the digital section, and they are joined only at Pin 30 (DGND) of the AD7884.

#### **ANALOG INPUT SECTION**

The analog input to the board is applied to the miniature BNC connector SKT 1, labelled A<sub>IN</sub>. The input then goes to the link, LK8, and from there on to the input buffer, IC3. LK8 allows the user to divert the input to signal conditioning circuitry, which may be built on the grid section of the board. With LK8 inserted, A<sub>IN</sub> goes directly to IC3, an AD845. This is a very fast JFET amplifier which combines very low input offset voltage and offset drift with fast settling and high slew rate. Consult the AD845 data sheet for full details.

The AD845 drives the AD7884 inputs through a series of links. These links allow the user to configure the ADC for either a  $\pm 3$  volt input or a  $\pm 5$  volt input. Table II below shows the necessary link settings for each range.

Table II. LK1-LK4 Settings

| Input Range | LK1 | LK2 | LK3 | LK4 |

|-------------|-----|-----|-----|-----|

| ±5 Volts    | AB  | AB  | AB  | AB  |

| ±3 Volts    | ВС  | ВС  | BC  | ВС  |

#### **AGND BUFFER**

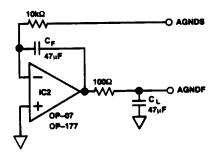

IC2 is the force, sense amplifier for AGND. The AGNDS pin should be at zero potential. The board uses an OP-07 for IC2. The output of IC2 is decoupled with a 47  $\mu F$  solid tantalum capacitor to AGND to deal with the fast current transients on the AGNDS pin. The stability of this arrangement is marginal, and if the user wishes to improve the phase margin, the circuit given in Figure 2 may be used. A feedback capacitor (C<sub>F</sub>) of 47  $\mu F$  should be used. This circuit compensates for the load capacitor by adding a low frequency zero and ensures an adequate phase margin.

# **MULTIPLEXER APPLICATIONS**

When the AD7884 is used in multiplexer applications, it is possible for the analog input to see a full-scale step input. In these applications, it is better to use a very fast amplifier as the AGND buffer. Suitable op amps are the AD845 or AD847. With these, there is no need for the 47  $\mu\text{F}$  capacitor to AGND at the output, and the step response time allows a throughput of 150 kHz to be achieved.

Figure 2. Compensation Circuit for AGND Buffer

#### REFERENCE SECTION

The required +3 V reference is derived from the AD586. The +5 V output is divided down to +3 V by R1 and R2 before being buffered by IC6. IC4 is a unity gain inverter which provides the -3 V negative reference. The gain setting resistors are on-chip and are factory trimmed to ensure precise tracking of  $V_{\rm REF+}$ . Figure 3 shows IC4 and IC6 as AD845s. The very high slew rate of these amplifiers means that they can respond to the rapidly changing reference input impedance and input currents and hold the  $V_{\rm REF+}$  and  $V_{\rm REF-}$  inputs at the required dc levels.

Figure 3. AD7884 Evaluation Board Circuit Diagram

## **EVALUATION BOARD INTERFACING**

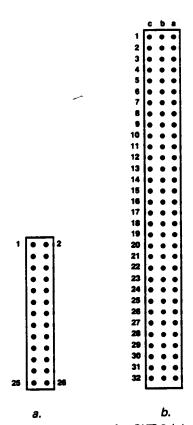

The board has a straight parallel 16-bit interface. The Parallel Port is available at two sockets on the board, SKT 3 and SKT 4. The Eurocard Connector, SKT 4 allows the board to be connected directly to the evaluation board for the ADSP-2100 Digital Signal Processor, which is available from Analog Devices. SKT 3 provides a general purpose socket for interfacing to any other parallel processor systems. The pinout for SKT 3 and SKT 4 is given in Figure 4 below.

Conversion is initiated by applying a CONVST signal at SKT 2. BUSY is low during conversion and goes high to indicate the end of conversion. In the simplest interface mode, CS and RD are tied permanently low through links LK5 and LK6. This means that the data bus drivers are permanently turned on. Each new conversion result is automatically put on the bus at the end of conversion.

Figure 4. Pin Configurations for SKT 3 (a) and SKT 4 (b)

The AD7884 design guarantees that the data is valid on the BUSY rising edge. This means that the BUSY signal can be used to latch the conversion result into the external latches, IC 10 and IC 11. These may then be read by the processor before the next conversion result is latched. For standard 16-bit interfacing, LK7 is inserted. However, if the user wishes to interface to an 8-bit system, LK7 can be omitted so that each 8-bit latch can be read separately.

It is also possible to evaluate the AD7884 performance when connected directly to the processor data bus and not isolated by latches. Take out the latches, IC10 and IC11 and short the D inputs to the Q outputs. Then use the  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  inputs in the standard fashion. Omit LK5 and LK6. This means that the  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  inputs are now controlled by Pins 5 and 3 (SKT 3) or Pins C14 and C13 (SKT 4). In this configuration,  $\overline{\text{BUSY}}$  generates a processor interrupt at the end of conversion. The interrupt subroutine is a standard Read operation.

### **BOARD LAYOUT AND COMPONENT OVERLAY**

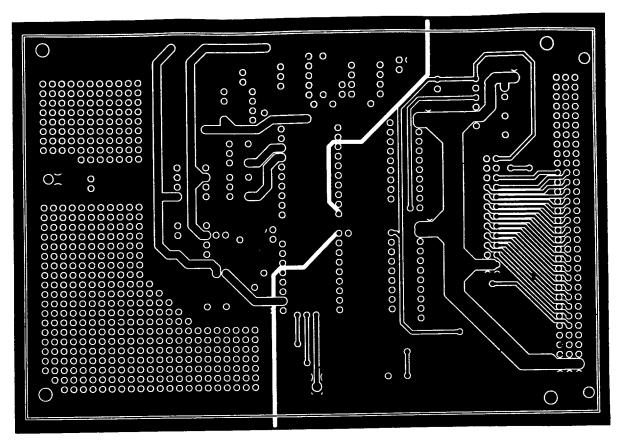

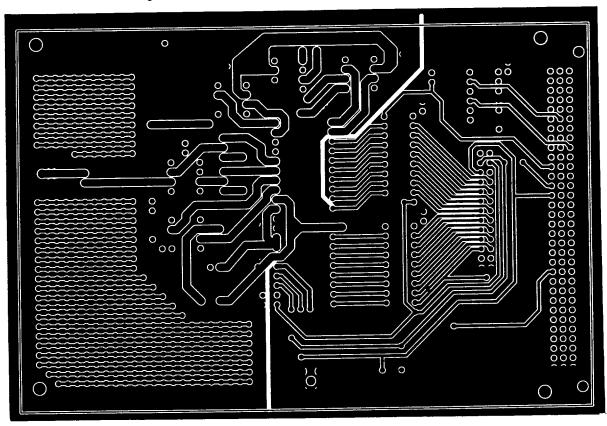

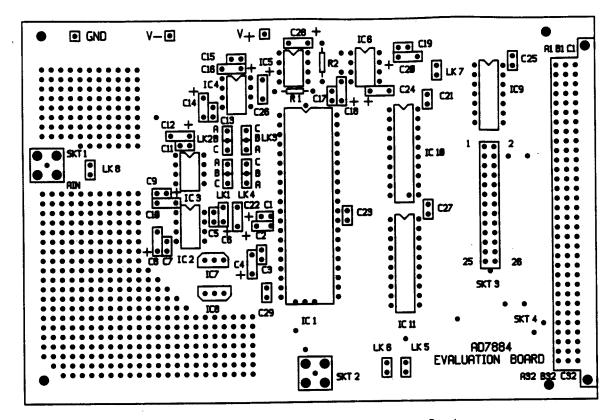

Figures 5, 6 and 7 show the evaluation board layout and component overlay. These may be used to study the grounding and decoupling techniques for the various components. There is a separate analog and digital ground plane which is joined only at Pin 30 (DGND) of the AD7884.

Figure 5. AD7884 Evaluation Board Component Side Layout

Figure 6. AD7884 Evaluation Board Solder Side Layout

Figure 7. AD7884 Evaluation Board Component Overlay