#### AD7606B: Advanced Features Enabled in Software Mode and System Level Benefits by Lluis Beltran Gil

### **INTRODUCTION**

The AD7606B is an enhanced version of the AD7606 analog-to-digital, data acquisition systems (DAS). The AD7606B can be used as a direct pin for pin replacement for the AD7606, which is called hardware mode, with the benefits stated in Table 1. However, the AD7606B in software mode includes the following advanced features:

- Independent, per channel basis, range selection, including a ±2.5 V range option

- ► System gain/phase/offset on-chip calibration

- Analog input open-circuit detection

- Additional oversampling ratios (OSR = 128 and 256)

- Optional 1, 2, or 4 serial data output configurations

- Diagnostics and monitoring

Software or register mode is enabled by tying the three oversampling digital inputs high (OS2, OS1, and OS0), allowing access to configure the register map to take advantages of the previously stated features. See the AN-1559 Application Note for full details on

backwards compatibility and how to migrate from the AD7606 to the AD7606B in both hardware mode and software mode, as well as how to write the register map in both serial (SDI pin) and parallel interface ( $\overline{WR}$  pin).

This application note describes each of the advanced features the AD7606B has available in software mode and their system level impact. For full details on the AD7606B, see the AD7606B data sheet. Consult this data sheet in conjunction with this application note.

### NOTICE

The software snippets contained in this application note is Copyright ©2021 by Analog Devices, Inc. All rights reserved. This software is proprietary to Analog Devices, Inc. and its licensors. This software is provided on an "as is" basis without any representations, warranties, guarantees, or liability of any kind. Use of the software is subject to the terms and conditions of the Clear BSD License. For further information on the firmware example code, visit the AD7606 Mbed IIO Application wiki page.

| Parameter                                          | AD7606                           | AD7606B (Hardware Mode)    | AD7606B (Software Mode)             |

|----------------------------------------------------|----------------------------------|----------------------------|-------------------------------------|

| Typical Input Impedance                            | 1 ΜΩ                             | 5 ΜΩ                       | 5 MΩ                                |

| Maximum Throughput Rate                            | 200 kSPS                         | 800 kSPS                   | 800 kSPS                            |

| Temperature Range                                  | -40°C to +85°C                   | -40°C to +125°C            | -40°C to +125°C                     |

| V <sub>DRIVE</sub> Range                           | 2.3 V to 5.25 V                  | 1.71 V to 3.6 V            | 1.71 V to 3.6 V                     |

| Absolute Maximum Input Voltage                     | ±16.5 V                          | ±21 V                      | ±21 V                               |

| Analog Input Range                                 | ±10 V or ±5 V <sup>1</sup>       | ±10 V or ±5 V <sup>1</sup> | ±10 V, ±5 V, or ±2.5 V <sup>2</sup> |

| System Gain, Phase, and Offset On-Chip Calibration | Not applicable                   | Not accessible             | Available <sup>2</sup>              |

| Oversampling Ratio (OSR)                           | From no oversampling to OSR = 64 | From no OS to OSR = 64     | From no OS to OSR = 256             |

| Open Circuit Detection                             | Not applicable                   | Not accessible             | Available <sup>2</sup>              |

| Serial Data Output lines                           | 2                                | 2                          | Selectable: 1, 2, or 4              |

| Diagnostics                                        | Not applicable                   | Not accessible             | Available                           |

<sup>1</sup> Not on a per channel basis.

<sup>2</sup> On a per channel basis.

# **TABLE OF CONTENTS**

| Introduction                    | 1 |

|---------------------------------|---|

| Notice                          | 1 |

| Initialize the AD7606B          | 3 |

| Enter Software Mode at Power-Up | 3 |

| AD7606B Check by Register Read  | 3 |

| Register Configuration          | 4 |

| Calibration Features            | 5 |

| Analog Input Range              | 5 |

| System Offset Error Calibration | 5 |

| System Gain Error Calibration   | 6 |

| System Phase Error Calibration  | 7 |

# **REVISION HISTORY**

5/2023—Revision 0: Initial Version

| Open-Circuit Detection              | 8  |

|-------------------------------------|----|

| Manual Mode                         |    |

| Automatic Mode                      | 11 |

| Monitoring and Diagnostics Features | 13 |

| Overvoltage (OV)/Undervoltage (UV)  | 13 |

| Interface Check                     | 13 |

| SPI Invalid Read/Write              | 13 |

| BUSY Stuck High                     | 13 |

| Diagnostics Multiplexer             | 13 |

| Temperature Sensor                  | 13 |

|                                     |    |

## **INITIALIZE THE AD7606B**

## ENTER SOFTWARE MODE AT POWER-UP

To initialize the AD7606B in software mode, ensure that the following is true:

- All three oversampling pins (OS2, OS1, and OS0) must be tied to logic high.

- PAR/SER pin tied low or high depending on the data interface used, parallel or serial, respectively.

- RANGE pin can be tied either low or high because it is ignored in software mode. The range is selected through the corresponding register on a per channel basis.

After the initialization process mentioned in the previous list, the AD7606B is configured in software mode with registers in default status. In this application note, and in the Notice section, the AD7606B is used in software serial mode as an example.

After the initialization, the voltage pins are typically as follows:

```

▶ AVCC = 5.0 V

```

- ▶ V<sub>DRIVE</sub> = 3.3 V, 2.5 V, or 1.8 V

- REGCAP = 1.9 V

- ▶ REFIN/REFOUT = 2.5 V

- ▶ REFCAPA, REFCAPB = 4.4 V

When the voltage on the previously mentioned pins is verified, issuing a reset ensures that the default parameters are properly loaded on the AD7606B. To issue a reset, use the following code:

```

int32_t ad7606_reset(struct ad7606_dev *dev)

{

int32_t ret;

ret = gpio_set_value(dev->gpio_reset, 1);

udelay(3);

ret = gpio_set_value(dev->gpio_reset, 0);

ad7606_reset_settings(dev);

return ret;

}

```

## AD7606B CHECK BY REGISTER READ

After the AD7606B initialization, register values are all in default, as shown in the AD7606B data sheet. Users may check the DEVICE\_ID, SILICON\_REVISION, or RESET\_DETECT bits in the memory map, for example, to confirm that a valid full or partial reset is received. A single AD7606B register read function is shown in the following code as a reference. Replace the register address with those registers where the DEVICE\_ID, SILICON\_REVISION, or RESET\_DETECT bits are contained. Serial Peripheral Interface (SPI) Mode 2 can be used with direct connection between the microcontroller (MCU) or digital signal processor (DSP) and the AD7606B.

```

int32 t ad7606 spi reg read(struct ad7606 dev

*dev,

uint8 t reg addr,

uint8 t *reg data)

{

uint8 t buf[3];

uint3\overline{2} t sz = 2;

int32 t ret;

buf[0] = AD7606 RD FLAG MSK(reg_addr);

buf[1] = 0x00;

ret = spi write and read(dev->spi desc,

buf, sz);

if (ret < 0)

return ret;

dev->reg mode = true;

buf[0] = AD7606 RD FLAG MSK(reg addr);

buf[1] = 0x00;

ret = spi write and read(dev->spi desc,

buf, sz);

if (ret < 0)

return ret;

if (reg data)

*reg data = buf[1];

return ret;

```

## **REGISTER CONFIGURATION**

After the voltages are correct and the SPI is functional, registers must be written, depending on the required application, to load the working configuration, for example, parameters such as the range, the oversampling, or the diagnostics. Some functions includ-

```

int32_t ad7606_spi_reg_write(struct ad7606_dev *dev,

uint8 t reg addr,

uint8 t reg data)

{

uint8 t buf[3];

int32 t ret;

uint3\overline{2} t sz = 2;

/* Dummy read to place the chip in register mode. */

if (!dev->reg mode) {

ret = ad7606_spi_reg_read(dev, reg_addr, NULL);

}

buf[0] = AD7606 WR FLAG MSK(reg addr);

buf[1] = reg data;

ret = spi write and read(dev->spi desc, buf, sz);

return ret;

}

```

ed on the no OS drivers, like ad7606\_set\_oversampling() or ad7606\_set\_ch\_range(), help to write registers like the oversampling or range configuration. These functions, in turn, use the ad7606\_spi\_reg\_write() function, which is used in general for writing any device register. To write registers, use the following code:

## **CALIBRATION FEATURES**

While hardware mode is selected on the AD7606B, this device is fully compatible regarding pins and function with the AD7606. The benefits the AD7606B brings are higher input impedance, higher throughput rate, wider temperature range, and lower digital supply voltage operating range, as described in the AN-1559 Application Note. However, entering software mode by tying the three oversampling pins high (Pin 3, Pin 4, and Pin 5), enables many advanced features that bring system level benefits, as described in the following sections.

## ANALOG INPUT RANGE

On the AD7606, the polarity on the digital input RANGE pin (Pin 8) determines the input range on the eight analog input channels. If this pin is tied to a logic high, the analog input range is  $\pm 10$  V for all channels. If this pin is tied to a logic low, the analog input range is  $\pm 5$  V for all channels. A logic change on this pin has an immediate effect on the analog input range.

Likewise, on the AD7606B in hardware mode, the analog input range for all channels is selected through the RANGE pin. However, in software mode, the analog input range is selected on a per channel basis. To do so, Register 0x03 through Register 0x06 are used to individually set the range on each channel.

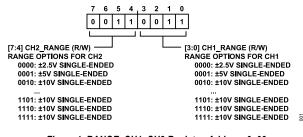

For example, in the RANGE\_CH1\_CH2 register (Address 0x03) shown in Figure 1, the four MSBs determine the analog input range on Channel 2 and the four LSBs determine the analog input range on Channel 1. The analog input voltage can be chosen to be either  $\pm 2.5$  V,  $\pm 5$  V, or  $\pm 10$  V single-ended.

This per channel analog input range selection allows a different range on each channel to be set, which may be beneficial if, for example, the voltage and current channels needed a different range in an energy monitoring application. The per channel analog input range selection can also serve for setting different ranges on measurement and protection channels, for example, in energy protection applications.

### SYSTEM OFFSET ERROR CALIBRATION

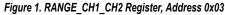

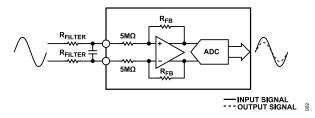

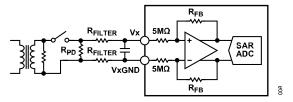

The AD7606B in software mode has registers to compensate for offset errors present in the system, whether these are due to the inherent offset error of the sensor or a mismatch between the front-end resistors on each analog input (Vx and VxGND), for example, the filter resistors ( $R_{FILTER}$ ) shown in Figure 2.

Figure 2. Gain/Offset On-Chip Calibration

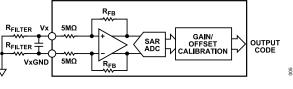

An 8-bit long register per each channel, Address 0x11 through Address 0x18, allows the AD7606B to digitally add an offset from -128 LSBs (writing 0x00 to the register) to +127 LSBs (writing 0xFF to the register) to the analog-to-digital converter (ADC) conversion data, to compensate for such a system offset error.

In other words, the offset added to the ADC code is, in LSBs, equal to the CHx\_OFFSET registers minus 128. Some examples for CHx\_OFFSET register data written and the corresponding offset added/subtracted from the ADC code are shown in Table 2.

| Output Code (I | LSBs) = ADC Code + | CHx OFFSET - 128 | (1) |

|----------------|--------------------|------------------|-----|

|                |                    |                  |     |

Table 2. CH1\_OFFSET Register Bit Decoding

| CH1_OFFSET Register | Offset Calibration |

|---------------------|--------------------|

| 0x00                | -128 LSBs          |

| 0x45                | -59 LSBs           |

| 0x80 (Default)      | 0 LSBs             |

| 0x83                | +3 LSBs            |

| 0xFF                | +127 LSBs          |

By connecting the two inputs together and tying them to analog ground (AGND), as shown in Figure 2, the system offset can be obtained by reading the ADC code. This system offset can then be calibrated by writing the corresponding register.

For example, if the sensor connected on Channel 1 has an offset equivalent to 10 LSBs (average value out of multiple ADC data reads to remove distribution caused by noise) or the mismatch on the front-end resistors causes an ADC code of 10 LSBs when the inputs are tied to ground, 10 LSBs then must be subtracted from the ADC code on each conversion to remove that offset. Because 128 is the default value on the offset registers, writing the CH1\_OFFSET register (Address 0x11) with 0x76 (118d (decimal)), the AD7606B effectively subtracts 10 LSBs from each ADC converted code. Therefore, this system offset error can be internally compensated through on-chip registers, eliminating the burden of having to compensate at the back end through software. To learn more on how to program the CHx\_OFFSET register, refer to the AD7606x software model from the AD7606B product page.

Figure 3. CH1\_OFFSET Register, Address 0x11, Default Value 0x80

#### To perform offset error calibration, use the following code:

```

int32_t ad7606_set_ch_offset(struct ad7606_dev

*dev, uint8_t ch, int8_t offset)

{

int ret;

uint8_t value = (uint8_t) (offset - 0x80);

if (ch >= dev->num_channels)

return -EINVAL;

ret = ad7606_spi_reg_write(dev,

AD7606_REG_OFFSET_CH(ch), value);

dev->offset_ch[ch] = offset;

return ret;

}

```

#### SYSTEM GAIN ERROR CALIBRATION

Depending on the analog input range selected on each channel, the programmable gain amplifier (PGA) is configured so that the proper gain (feedback resistor ( $R_{FB}$ )/input resistor ( $R_{IN}$ )) is selected to scale the analog input signal to meet the input range of the ADC.

Figure 4. Analog Input Circuitry,  $\rm R_{IN}$  of AD7606 Is 1 M $\Omega$  While  $\rm R_{IN}$  of AD7606B Is 5 M $\Omega$

Internally, the AD7606B has tight control over  $R_{FB}$  and  $R_{IN}$ , such that this ideal gain is accurately set by factory trimming, assuming no resistance on the front end. However, if an external resistor is placed in the front end, for example, for protection or for extra filtering, the actual gain is no longer the ideal  $R_{FB}/R_{IN}$ .

$$IdealGain = \frac{R_{FB}}{R_{IN}} \tag{2}$$

$$ActualGain = \frac{R_{FB}}{R_{FILTER} + R_{IN}}$$

(3)

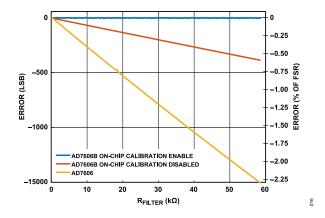

The addition of an  $R_{FILTER}$  in series to  $R_{IN}$  modifies the divisor, which changes the actual system gain by adding an extra gain error. The bigger the  $R_{FILTER}$  used, the bigger the gain error introduced becomes, as shown in Figure 5. For a given  $R_{FILTER}$ , because the  $R_{IN}$  of the AD7606B is much bigger (5 MΩ) than that of the AD7606 (1 MΩ), the gain error introduced by  $R_{FILTER}$  is much smaller on the AD7606B compared to the AD7606. Therefore, the AD7606B is less sensitive to the gain error introduced by placing an external  $R_{FILTER}$  to the device.

Figure 5. System Gain Error Introduced by R<sub>FILTER</sub> for Either the AD7606 or the AD7606B (Calibration Enabled or Disabled) Through On-Chip Calibration

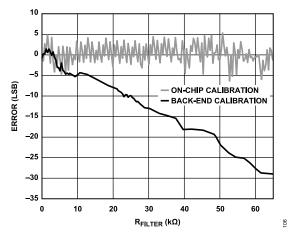

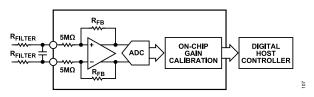

Knowing the typical input resistance, provided in both the AD7606 data sheet and the AD7606B data sheet, a back-end calibration on the controller side (field programmable gate array (FPGA), DSP) can be programmed if there are resources available. However, if using the AD7606B in software mode, this system gain error can be automatically compensated by an on-chip register, on a per channel basis. Because the input impedance of the AD7606B is internally known accurately on each device, its automatic gain calibration is always more precise than any back-end calibration programmed based on the input impedance typical numbers, reducing the burden of doing all calibration computation on the controller side. See Figure 6 for an example of the calibration performed on the AD7606B for a certain range of  $R_{FILTER}$  values.

Figure 6. Total Error After Applying Back-End Calibration (Assuming R<sub>IN</sub> Equal to Typical Input Impedance Value) Compared to Applying the On-Chip Calibration

Figure 7. Analog Signal Chain with per Channel Gain Calibration, to Remove Burden on Back-End Digital Controller

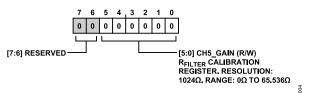

To use the gain calibration feature, Register 0x09 through Register 0x10 are allocated to program the R<sub>FILTER</sub> used on each channel, up to 65 kΩ with a resolution of 1024 Ω. Using this feature, the system gain error can be kept lower than 0.02% independently of what R<sub>FILTER</sub> is used, as seen in Figure 5. If back-end calibration was used instead, take extra error margin into account due to input impedance uncertainty.

For example, the system gain error introduced by a 27 k $\Omega$  R<sub>FILTER</sub> used in the front end of Channel 5 is automatically compensated by writing 0x1B (27d) into the CH5\_GAIN register (Address 0x0D), shown in Figure 8. To learn more on how to program the CHx\_GAIN register, refer to the AD7606x software model from AD7606B product page.

Figure 8. CH5\_GAIN Register, Address 0x0D

To configure the gain of the channel, the following code performs the previously mentioned functions:

# SYSTEM PHASE ERROR CALIBRATION

When measuring voltages and currents on the same power line, through a current transformer, there is a phase mismatch between the two channels. Something similar may happen if there is a mismatch between  $R_{FILTER}$  and the filter capacitor ( $C_{FILTER}$ ) between two channels that must be sampled simultaneously.

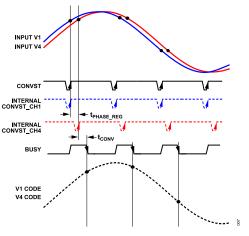

This system phase error can be internally compensated on the AD7606B by delaying the internal sampling instant. In the example shown in Figure 9, there is a slight delay ( $t_{PHASE\_REG}$ ) between Channel 1 and Channel 4. If this time delay is known, by programming it back to the CH4\_PHASE register (Address 0x1C), Channel 4 is effectively a sampled  $t_{PHASE\_REG}$  time after V1, compensating for the phase mismatch between the two channels and providing an in-phase output.

Note that delaying any channel implies lengthening the BUSY pin high time, that is, the conversion time ( $t_{CONV}$ ) extends by as much as the most delayed channel is programmed at and, therefore, the maximum throughput rate may be compromised.

Figure 9. System Phase Calibration Functionality

There is one phase register per channel, Address 0x19 through Address 0x20, allowing for compensating the phase error on each channel individually with a resolution of 1.25  $\mu$ s, and up to a 318.75  $\mu$ s time delay in each channel with regards to the CONVST pin signal.

To check this feature, perform the following steps:

- 1. Apply one ac source (or multichannel calibrator with accurate phase control), like 50 Hz or 60 Hz, to all the signal chain inputs.

- 2. Capture enough channel codes to calculate the channel to channel group delay matching by fast Fourier transform (FFT), discrete Fourier transform (DFT), or some other method.

- Calculate the CHx\_PHASE\_OFFSET register values in steps of 1.25 µs.

- 4. Write the phase matching error registers into AD7606B.

#### To write the phase matching error registers, use the following code:

```

int32_t ad7606_set_ch_phase(struct ad7606_dev

*dev, uint8_t ch, uint8_t phase)

{

int ret;

if (ch >= dev->num_channels)

return -EINVAL;

ret = ad7606_spi_reg_write(dev,

AD7606_REG_PHASE_CH(ch), phase);

dev->phase_ch[ch] = phase;

return ret;

}

```

### **OPEN-CIRCUIT DETECTION**

As explained in the AN-1559 Application Note, because the AD7606B has a larger  $R_{\rm IN}$  than the AD7606 (5 M $\Omega$  compared to 1 M $\Omega$ ), an easier detection of when the sensor has disconnected by using a given pull-down resistor ( $R_{PD}$ ) in parallel with the sensor is allowed. The increase of  $R_{\rm IN}$  results in a lower ADC output code when the sensor disconnects.

Figure 10. Analog Front End with R<sub>PD</sub>

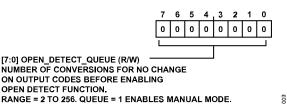

When entering software mode of the AD7606B, there is an opencircuit detection feature, disabled by default, with two possible modes, manual and automatic open-circuit detection.

#### MANUAL MODE

The open-circuit detection feature is disabled by default, but writing 0x01 into the OPEN\_DETECT\_QUEUE register (Address 0x2C) enables the manual open-circuit detection mode.

#### Figure 11. OPEN\_DETECT\_QUEUE Register, Address 0x2C

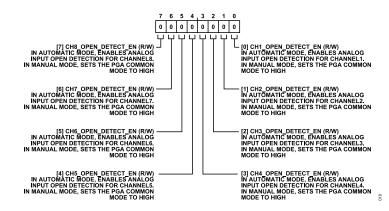

In manual mode, if the ADC code repeats for a number of conversions, before assuming the sensor has been disconnected, the disconnection can be verified through changing the PGA common mode. The common-mode voltage of PGA is controlled by the corresponding CHx\_OPEN\_DETECT\_EN bit in the OPEN\_DE-TECT\_ENABLE register (Address 0x23), on a per channel basis, as shown in Figure 12. If changing the PGA common mode on a given channel changes the ADC output code, this indicates that the sensor is disconnected. Otherwise, the sensor is still connected to the analog input.

This method still requires some back-end effort. Detect N repeated samples (below a threshold), change the PGA common mode, and then verify if the ADC output code changes with the common-mode change or not. This burden can be eliminated by enabling the automatic mode, which lets the AD7606B automatically detect when an open circuit occurs. To implement the open-circuit detection algorithm in manual mode, use the following code:

```

/* Enter into manual open circuit detection mode */

do {

if (ad7606 spi reg write(device, AD7606 REG OPEN DETECT QUEUE, 1) == SUCCESS) {

/* Read the ADC on selected chnnel (first reading post open circuit detection start) */

prev adc code = single data read(device,

channel->ch num - 1,

attr polarity val[channel->ch num - 1]);

/* Perform N conversions and monitor the code delta */

for (cnt = 0; cnt < MANUAL OPEN DETECT CONV CNTS; cnt++) {</pre>

/* Check if code is within 350LSB (nearest ZS code) */

if (prev adc code>= 0 && prev adc code < MANUAL OPEN DETECT ENTRY TRHLD)

{

/* Perform next conversion and read the result */

curr adc code = single data read(device,

channel->ch num - 1,

attr polarity val[channel->ch num - 1]);

/* Check if delta b/w current and previus reading is within 10 LSB code */

if (abs(curr_adc_code - prev_adc_code) > MANUAL_OPEN_DETECT_CONV_TRSHLD) {

open detect done = true;

```

```

break;

}

/* Get the previous code */

prev adc code = curr adc code;

} else {

open detect done = true;

break;

}

}

/* Break if open circuit detection aborted (in case above conditions not met) */

if (open detect done)

break;

/* Set common mode high (enabling open circuit detect on selected channel) */

if (ad7606 spi reg write(device,

AD7606 REG OPEN DETECT ENABLE,

(1 << ((channel->ch num) - 1))) == SUCCESS) {

/* Perform next conversions (~2-3) and read the result (with common mode set high) */

for (cnt = 0; cnt < MANUAL OPEN DETECT CM CNV CNT; cnt++) {</pre>

udelay(100);

curr adc code = single data read(device,

channel->ch num - 1,

attr polarity val[channel->ch num - 1]);

}

/* Check if delta b/w common mode high code and previous N conversion code is >

threshold */

if ((curr adc code - prev adc code) < MANUAL OPEN DETECT THRESHOLD RPD50K) {

open detect done = true;

break;

}

} else {

return -EINVAL;

/* Break if open circuit detection aborted (in case above conditions not met) */

if (open detect done)

break;

/* Set common mode low (disabling open circuit detect on channel) */

if (ad7606 spi reg write(device,

AD7606 REG OPEN DETECT ENABLE,

0) == SUCCESS) {

/* Perform next conversion and read the result (with common mode set low) */

curr adc code = single data read(device,

channel->ch num - 1,

attr polarity val[channel->ch num - 1]);

/* Check if delta b/w common mode low code and previous N conversion code is <

threshold */

if (abs(curr adc code - prev adc code) < MANUAL OPEN DETECT THRESHOLD RPD50K) {

```

```

open_detect_flag = true;

open_detect_done = true;

}

} else {

return -EINVAL;

}

} else {

return -EINVAL;

}

} while (0);

```

Figure 12. OPEN\_DETECT\_ENABLE Register, Address 0x23

# AUTOMATIC MODE

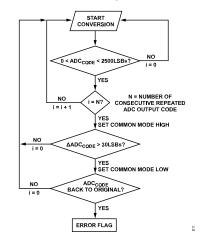

In automatic mode, the previous method is implemented on chip, eliminating the burden on the back-end software that detects the sensor disconnection. The automatic mode is enabled through writing the number of conversions (N) before the flag triggers, as shown in Figure 11. Then, each channel checker can be enabled or disabled individually through the OPEN\_DETECT\_ENABLE register (Figure 12).

The algorithm, simplified in the diagram in Figure 13, runs in the background, and if in a particular channel the error flag triggers, the algorithm can be checked in the OPEN\_DETECTED register (Address 0x24) or in the STATUS header if appended to the ADC data, or in the STATUS register.

The following code implements the open-circuit detection algorithm in automatic mode. The time it takes for an open circuit to be automatically detected depends on the other elements like the external RC components and the oversampling ratio. To calculate this time, it is recommended to visit the AD7606B product page and

download the design tool available on the **Tools & Simulations** section. This tool allows the user to learn more about the other calibration features described throughout this application note.

Figure 13. Automatic Open-Circuit Detection Algorithm

```

/* Enter into open circuit auto open detect mode */

if (ad7606 spi reg write(device,

AD7606 REG OPEN DETECT QUEUE,

open detect queue cnts[channel->ch num - 1]) == SUCCESS) {

/* Enable open circuit detection on selected channel */

if (ad7606 spi reg write(device,

AD7606 REG OPEN DETECT ENABLE,

(1 \ll ((channel->ch num) - 1))) == SUCCESS) {

/* Monitor the open detect flag for max N+15 (open detect queue count) conversions.

* Note: In ideal scenario, the open detect flash should be monitored continuously

while

* background N conversions are in progress */

for (conv cnts = 0;

conv cnts < (open detect queue cnts[channel->ch num - 1] +

AUTO OPEN DETECT QUEUE EXTRA CONV CNT);

conv cnts++) {

if (ad7606 convst(device) == SUCCESS) {

udelay(100);

/* Monitor the open detect flag */

if (ad7606 spi reg read(device,

AD7606 REG OPEN DETECTED,

&open detect flag) == SUCCESS) {

open detect flag >>= (channel->ch num - 1);

open detect flag &= 0x1;

rw status = SUCCESS;

if (open detect flag) {

break;

}

} else {

rw status = FAILURE;

break;

} else {

rw status = FAILURE;

```

| break; |  |

|--------|--|

| }      |  |

| }      |  |

| }      |  |

## MONITORING AND DIAGNOSTICS FEATURES

## OVERVOLTAGE (OV)/UNDERVOLTAGE (UV)

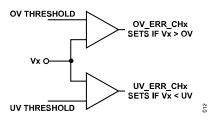

Each analog input on the AD7606B, V1 to V8 and V1GND to V8GND, has built-in comparator circuitry to monitor for overvoltage and undervoltage events. This circuitry is disabled by default. Any of these comparators can be individually enabled through the AIN\_OV\_UV\_DIAG\_ENABLE register (Address 0x25) so that the analog input voltage is monitored and triggers an alert if either the OV threshold or UV threshold is surpassed.

Figure 14. Overvoltage and Undervoltage Circuitry on Each Analog Input

When the circuitry is enabled, when the voltage on any analog input pin goes above the OV threshold shown in the AD7606B data sheet, the AIN\_OV\_DIAG\_ERROR register (Address 0x26) shows which channel or channels have an overvoltage event.

When the voltage on any analog input pin goes below the UV threshold shown in the AD7606B data sheet, the AIN\_UV\_DI-AG\_ERROR register (Address 0x27) shows which channel or channels have an undervoltage event.

These monitoring flags allow the user or the controller to rapidly know when an analog input, on a circuit protection application, for example, has gone beyond the full-scale voltage and beyond a voltage level that may represent a potential risk for the rest of the circuitry, allowing the controller to take any measure to help protect the system.

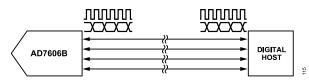

## INTERFACE CHECK

Use the interface check to ensure that the data is properly transmitted from the AD7606B to the digital controller. Enable the interface check through Bit 7 on the DIGITAL\_DIAG\_ENABLE register (Address 0x21), either periodically or when there is an event that may potentially cause errors on the data transmission, to make the AD7606B clock out fixed data values instead of conversion results. That way, if the data received matches the fixed data sent from the AD7606B, this verifies that the communication is performed without data corruption.

Figure 15. Data Transmission Lines Between AD7606B (Target) and Host Controller

For more information on the digital interface check, see the AD7606B data sheet.

### SPI INVALID READ/WRITE

When attempting to read back an invalid register address, the SPI\_READ\_ERR bit (Address 0x22, Bit 4) is set. The invalid readback address detection can be enabled by setting the SPI\_READ\_ERR\_EN bit (Address 0x21, Bit 4). If an SPI read error is triggered, it is cleared by overwriting that bit or disabling the checker.

When attempting to write to an invalid register address or a read only register, the SPI\_WRITE\_ERR bit (Address 0x22, Bit 3) is set. The invalid write address detection can be enabled by setting the SPI\_WRITE\_ERR\_EN bit (Address 0x21, Bit 3). If an SPI write error is triggered, it is cleared by overwriting that bit or disabling the checker.

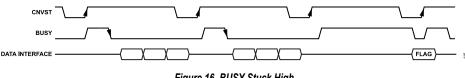

## **BUSY STUCK HIGH**

When enabled through the DIGITAL\_DIAG\_ENABLE register (Address 0x21, Bit 5), the BUSY\_STUCK\_HIGH\_ERR\_EN monitoring bit allows the AD7606B to alert the controller if, by any unlikely reason, the AD7606 stopped performing conversions (BUSY line is stuck) by asserting the BUSY\_STUCK\_HIGH\_ERR bit (Address 0x22, Bit 5). If this happens, the assertion of this bit indicates that a partial reset was automatically issued to recover normal operation.

For more information on the BUSY stuck high monitoring feature, see the AD7606B data sheet.

# DIAGNOSTICS MULTIPLEXER

All eight input channels contain a diagnostics multiplexer in front of the PGA that allows monitoring of the internal nodes described in Table 3 to ensure the correct operation of the AD7606B. Table 3 shows the bit decoding for the diagnostic mux register on Channel 1, as an example. When an internal node is selected, the input voltage at the input pins is deselected from the PGA.

| Address 0x28 |       |       |                      |

|--------------|-------|-------|----------------------|

| Bit 2        | Bit 1 | Bit 0 | Signal on Channel 1  |

| 0            | 0     | 0     | V1                   |

| 0            | 0     | 1     | Temperature sensor   |

| 0            | 1     | 0     | 4 × V <sub>REF</sub> |

| 0            | 1     | 1     | 4 × ALDO             |

| 1            | 0     | 0     | 4 × DLDO             |

| 1            | 0     | 1     | V <sub>DRIVE</sub>   |

| 1            | 1     | 0     | AGND                 |

| 1            | 1     | 1     | AV <sub>CC</sub>     |

## **TEMPERATURE SENSOR**

The temperature sensor can be selected through the diagnostic multiplexer and converted with the ADC, as shown in the AD7606B data sheet. The temperature sensor voltage is measured and is proportional to the die temperature, as per the following equation.

$$Temperature(°C) = \frac{ADCOUT(V) - 0.69068(V)}{0.019328(V/°C)} + 25(°C)$$

(4)

Typically, the sampled voltage of the temperature sensor is about 0.69 V in room ambient temperature.

Use the following code to read the temperature sensor.

The reference, analog low dropout (ALDO), digital low dropout (DLDO), the V<sub>DRIVE</sub> logic supply voltage, AGND, and the AV<sub>CC</sub> analog supply voltage can be self detected in the same way.

```

ssize t get chn temperature(void *device,

char *buf,

size t len,

const struct iio ch info *channel)

int32 t adc chn data = 0;

float temperature;

float voltage;

/* Configure the channel multiplexer to select temperature read */

if (ad7606 spi write mask(device,

AD7606 REG DIAGNOSTIC MUX CH(channel->ch num - 1),

AD7606 DIAGN MUX CH MSK (channel->ch num - 1),

AD7606 DIAGN MUX CH VAL((channel->ch num - 1),

TEMPERATURE MUX)) == SUCCESS) {

/* Allow to settle Mux channel */

udelay(100);

/* Sample the channel and read conversion result */

adc chn data = single data read(device, channel->ch num - 1,

attr polarity val[channel->ch num - 1]);

/* Convert ADC data into equivalent voltage */

voltage = convert adc raw to voltage(adc chn data,

attr scale val[channel->ch num - 1]);

/* Obtain the temperature using equation specified in device datasheet */

temperature = ((voltage - 0.69068) / 0.019328) + 25.0;

return (ssize t)sprintf(buf, "%f", temperature);

}

return -EINVAL;

```

Figure 16. BUSY Stuck High