## ADSP-BF539 Blackfin Processor Hardware Reference

Revision 1.1, February 2013

Part Number 82-000003-01

Analog Devices, Inc. One Technology Way Norwood, Mass. 02062-9106

## **Copyright Information**

© 2013 Analog Devices, Inc., ALL RIGHTS RESERVED. This document may not be reproduced in any form without prior, express written consent from Analog Devices, Inc.

Printed in the USA.

#### Disclaimer

Analog Devices, Inc. reserves the right to change this product without prior notice. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices, Inc.

## **Trademark and Service Mark Notice**

The Analog Devices logo, Blackfin, CrossCore, EngineerZone, EZ-KIT Lite, and VisualDSP++ are registered trademarks of Analog Devices, Inc.

All other brand and product names are trademarks or service marks of their respective owners.

# CONTENTS

## PREFACE

| Purpose of This Manual       | xlvii  |

|------------------------------|--------|

| Intended Audience            | xlvii  |

| Manual Contents              | xlviii |

| What's New in This Manual    | lii    |

| Technical Support            | liii   |

| Supported Processors         | liv    |

| Product Information          | liv    |

| Analog Devices Web Site      | lv     |

| EngineerZone                 | lv     |

| Notation Conventions         | lvi    |

| Register Diagram Conventions | lvii   |

|                              |        |

## **INTRODUCTION**

| Purpose of this Manual | 1-1 |

|------------------------|-----|

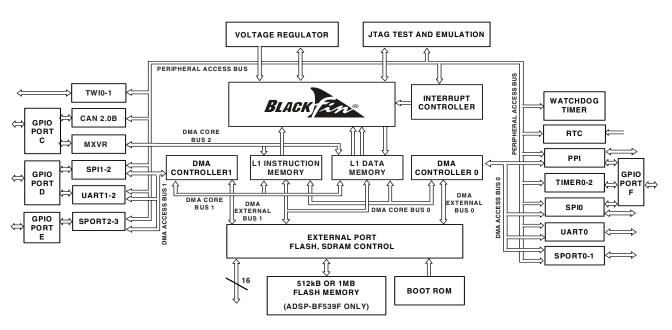

| Peripherals            | 1-4 |

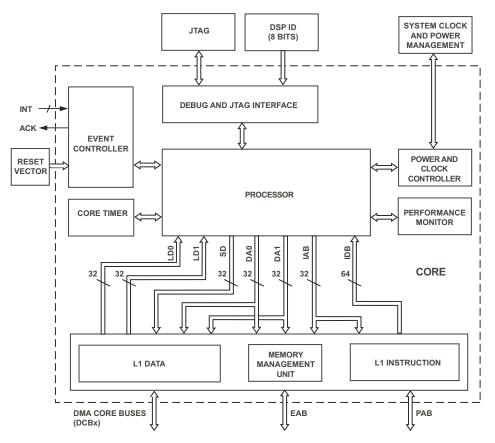

| Core Architecture      | 1-6 |

| Memory Architecture 1-9                      |

|----------------------------------------------|

| Internal Memory 1-10                         |

| External Memory 1-10                         |

| I/O Memory Space 1-11                        |

| Event Handling 1-11                          |

| Core Event Controller (CEC) 1-12             |

| System Interrupt Controller (SIC) 1-13       |

| DMA Support 1-13                             |

| External Bus Interface Unit 1-14             |

| PC133 SDRAM Controller 1-14                  |

| Asynchronous Controller 1-15                 |

| Parallel Peripheral Interface 1-15           |

| General Purpose Mode Descriptions 1-16       |

| Input Mode 1-16                              |

| Frame Capture Mode 1-16                      |

| Output Mode 1-17                             |

| ITU-R 656 Mode Descriptions 1-17             |

| Active Video Only Mode 1-17                  |

| Vertical Blanking Interval Mode 1-18         |

| Entire Field Mode 1-18                       |

| Serial Ports (SPORTs) 1-18                   |

| Serial Peripheral Interface (SPI) Ports 1-20 |

| Timers 1-20                                  |

| UART Ports 1-21                              |

| Media Transceiver MAC Layer (MXVR) 1-22              |

|------------------------------------------------------|

| Controller Area Network Port 1-23                    |

| Two-Wire Interface Port 1-24                         |

| Real-Time Clock 1-24                                 |

| Watchdog Timer 1-25                                  |

| Programmable Flags 1-25                              |

| General Purpose I/O 1-26                             |

| Clock Signals 1-27                                   |

| Dynamic Power Management 1-28                        |

| Full On Mode (Maximum Performance) 1-28              |

| Active Mode (Moderate Dynamic Power Savings) 1-28    |

| Sleep Mode (High Dynamic Power Savings) 1-28         |

| Deep Sleep Mode (Maximum Dynamic Power Savings) 1-29 |

| Hibernate State                                      |

| Voltage Regulation 1-30                              |

| Boot Modes 1-30                                      |

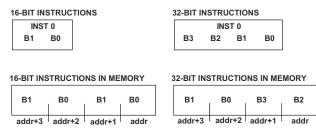

| Instruction Set Description 1-31                     |

| Development Tools                                    |

|                                                      |

## **COMPUTATIONAL UNITS**

| Using Data Formats               | 2-3 |

|----------------------------------|-----|

| Binary String                    |     |

| Unsigned                         |     |

| Signed Numbers: Two's-Complement | 2-4 |

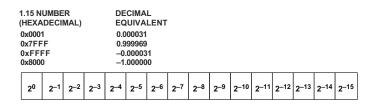

| Fractional Representation: 1.15  | 2-4 |

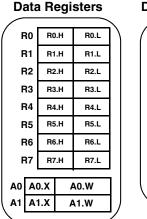

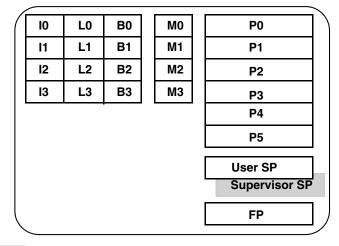

| Register Files 2-5                                   |

|------------------------------------------------------|

| Data Register File                                   |

| Accumulator Registers 2-6                            |

| Pointer Register File                                |

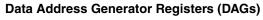

| DAG Register Set                                     |

| Register File Instruction Summary 2-8                |

| Data Types 2-10                                      |

| Endian Byte Order 2-12                               |

| ALU Data Types                                       |

| Multiplier Data Types 2-14                           |

| Shifter Data Types 2-14                              |

| Arithmetic Formats Summary 2-15                      |

| Using Multiplier Integer and Fractional Formats 2-16 |

| Rounding Multiplier Results 2-18                     |

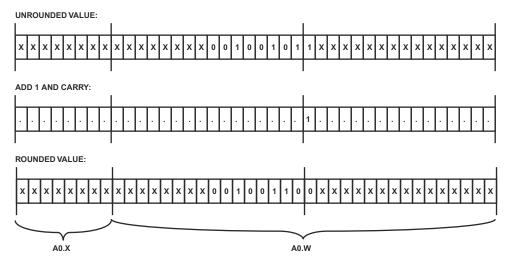

| Unbiased Rounding 2-19                               |

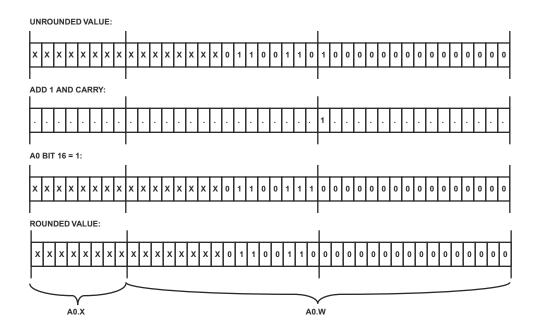

| Biased Rounding 2-21                                 |

| Truncation                                           |

| Special Rounding Instructions                        |

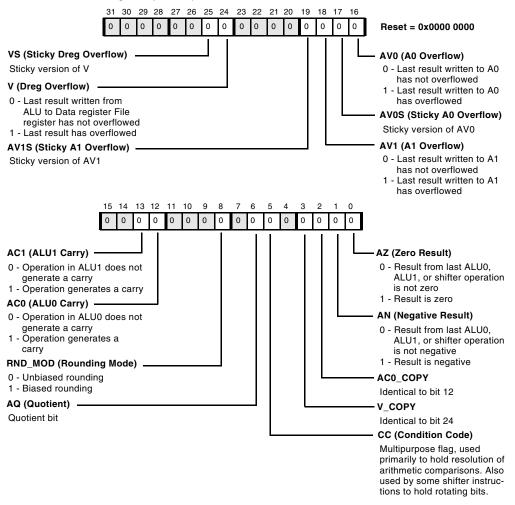

| Using Computational Status 2-23                      |

| ASTAT Register                                       |

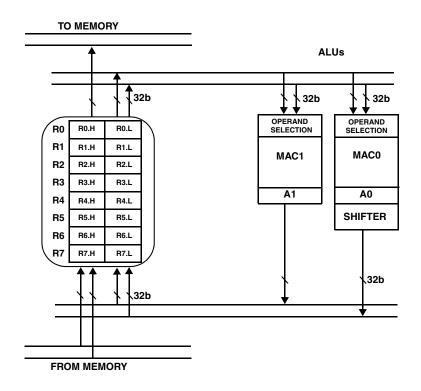

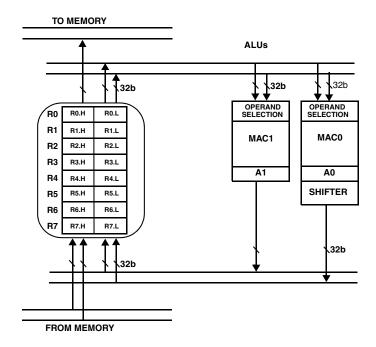

| Arithmetic Logic Unit (ALU) 2-24                     |

| ALU Operations                                       |

| Single 16-Bit Operations 2-26                        |

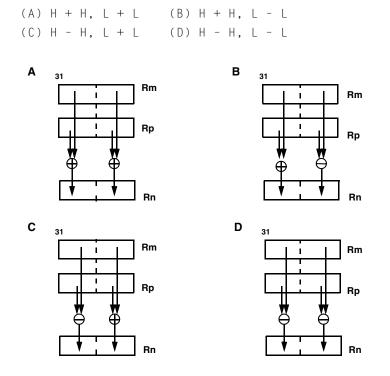

| Dual 16-Bit Operations 2-26                          |

| Quad 16-Bit Operations                                            | 2-27 |

|-------------------------------------------------------------------|------|

| Single 32-Bit Operations                                          | 2-28 |

| Dual 32-Bit Operations                                            | 2-29 |

| ALU Instruction Summary                                           | 2-29 |

| ALU Data Flow Details                                             | 2-34 |

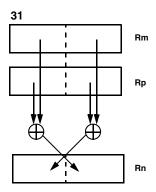

| Dual 16-Bit Cross Options                                         | 2-36 |

| ALU Status Signals                                                | 2-36 |

| ALU Division Support Features                                     | 2-37 |

| Special SIMD Video ALU Operations                                 | 2-37 |

| Multiply Accumulators (Multipliers)                               | 2-38 |

| Multiplier Operation                                              | 2-38 |

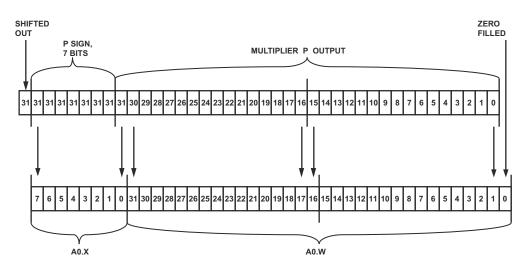

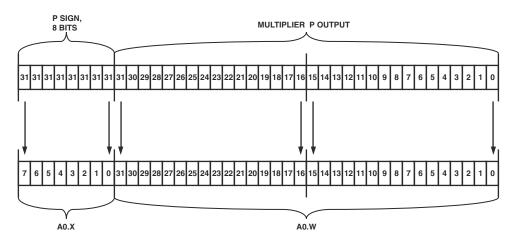

| Placing Multiplier Results in Multiplier Accumulator<br>Registers | 2-39 |

| Rounding or Saturating Multiplier Results                         | 2-39 |

| Saturating Multiplier Results on Overflow                         | 2-40 |

| Multiplier Instruction Summary                                    | 2-40 |

| Multiplier Instruction Options                                    | 2-43 |

| Multiplier Data Flow Details                                      | 2-45 |

| Multiply Without Accumulate                                       | 2-47 |

| Special 32-Bit Integer MAC Instruction                            | 2-49 |

| Dual MAC Operations                                               | 2-50 |

| Barrel Shifter (Shifter)        | 2-51 |

|---------------------------------|------|

| Shifter Operations              | 2-51 |

| Two-Operand Shifts              | 2-52 |

| Immediate Shifts                | 2-52 |

| Register Shifts                 | 2-52 |

| Three-Operand Shifts            | 2-53 |

| Immediate Shifts                | 2-53 |

| Register Shifts                 | 2-54 |

| Bit Test, Set, Clear, Toggle    | 2-54 |

| Field Extract and Field Deposit | 2-55 |

| Shifter Instruction Summary     | 2-55 |

## **OPERATING MODES AND STATES**

| User Mode 3                                            | 3-3 |

|--------------------------------------------------------|-----|

| Protected Resources and Instructions 3                 | 3-4 |

| Protected Memory                                       | 3-5 |

| Entering User Mode 3                                   | 3-5 |

| Example Code to Enter User Mode Upon Reset 3           | 3-5 |

| Return Instructions That Invoke User Mode 3            | 3-6 |

| Supervisor Mode                                        | 3-7 |

| Non-OS Environments                                    | 3-7 |

| Example Code for Supervisor Mode Coming Out of Reset 3 | 3-8 |

| Emulation Mode                                         | 3-9 |

| Idle State 3                                           | 3-9 |

| Example Code for Transition to Idle State              | -10 |

| Reset State                           | ·11 |

|---------------------------------------|-----|

| System Reset and Power-up 3-          | 12  |

| Hardware Reset                        | 14  |

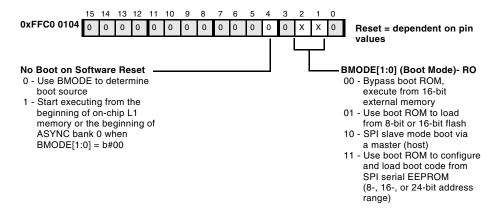

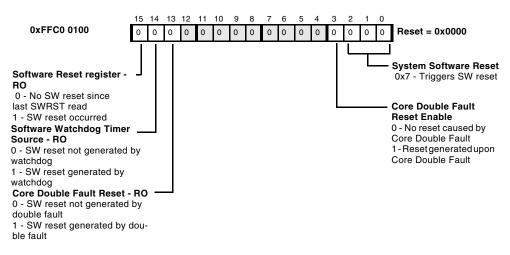

| SYSCR Register                        | 14  |

| Software Resets and Watchdog Timer 3- | 15  |

| SWRST Register                        | -16 |

| Core-Only Software Reset 3-           | ·17 |

| Core and System Reset                 | ·17 |

| Booting Methods 3-                    | 18  |

## PROGRAM SEQUENCER

| Sequencer Related Registers 4-3                  |

|--------------------------------------------------|

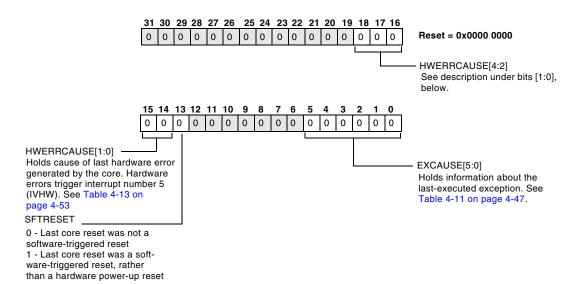

| Sequencer Status (SEQSTAT) Register 4-5          |

| Zero-Overhead Loop (LCx, LTx, LBx) Registers 4-5 |

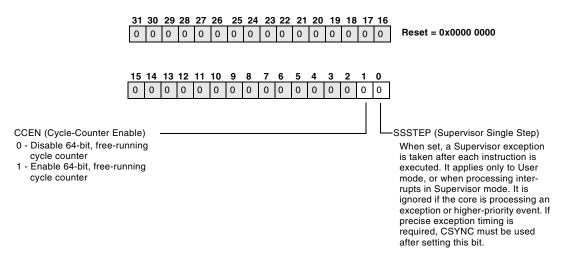

| System Configuration (SYSCFG) Register 4-6       |

| Instruction Pipeline                             |

| Branches and Sequencing 4-9                      |

| Direct Short and Long Jumps 4-11                 |

| Direct Call 4-11                                 |

| Indirect Branch and Call 4-11                    |

| PC-Relative Indirect Branch and Call 4-12        |

| Condition Code Flag 4-12                         |

| Conditional Branches 4-13                        |

| Conditional Register Move 4-14                   |

| Branch Prediction 4-14                           |

| Loops and Sequencing                                | 4-15 |

|-----------------------------------------------------|------|

| Events and Sequencing                               | 4-17 |

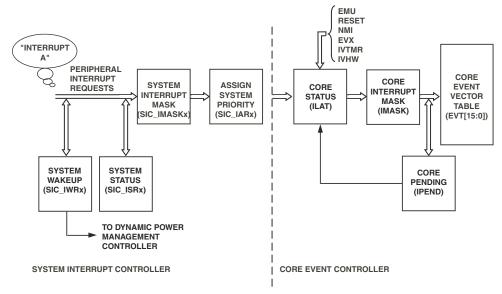

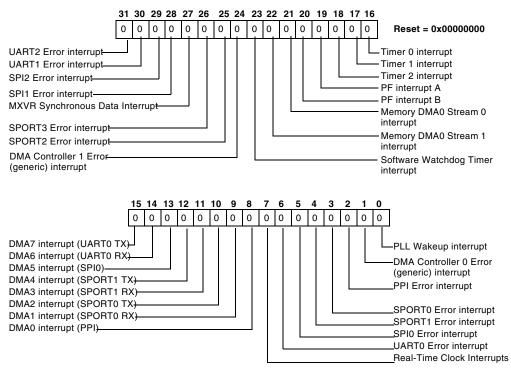

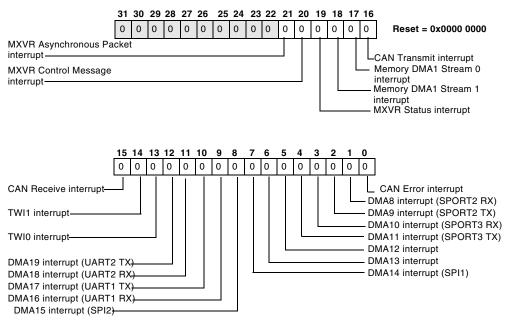

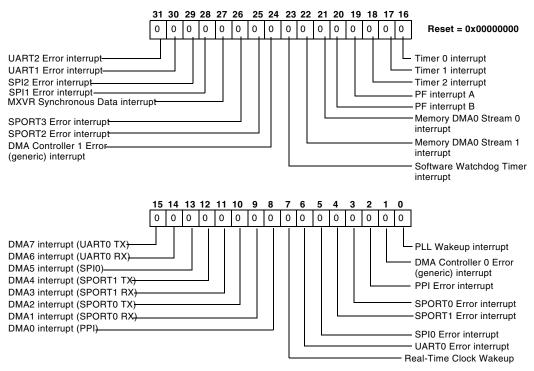

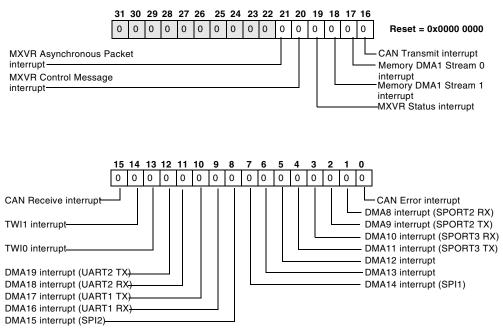

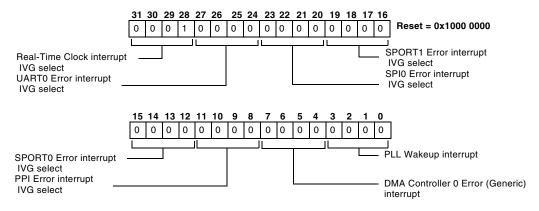

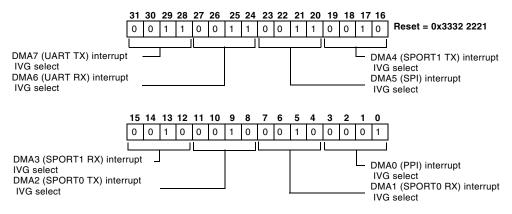

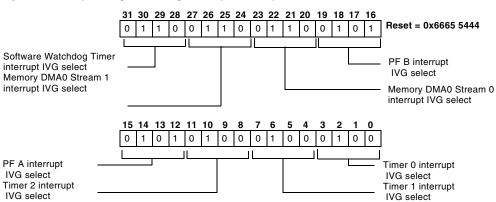

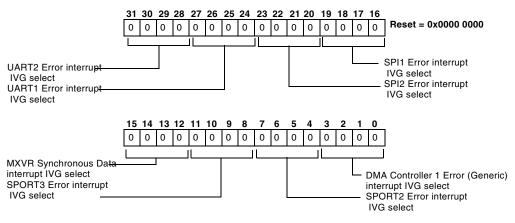

| System Interrupt Processing                         | 4-21 |

| System Peripheral Interrupts                        | 4-22 |

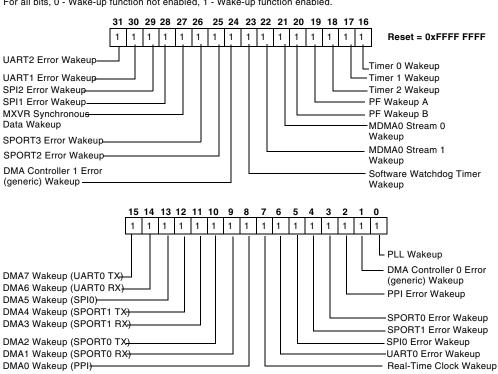

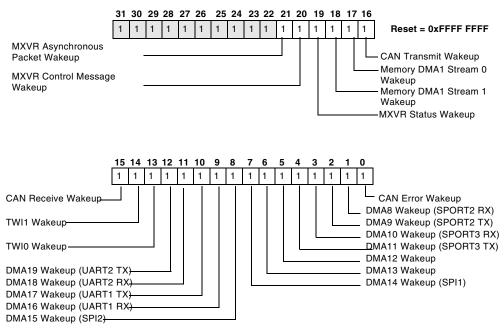

| System Interrupt Wakeup-Enable (SIC_IWRx) Registers | 4-26 |

| System Interrupt Status (SIC_ISRx) Registers        | 4-28 |

| System Interrupt Mask (SIC_IMASKx) Registers        | 4-31 |

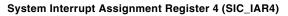

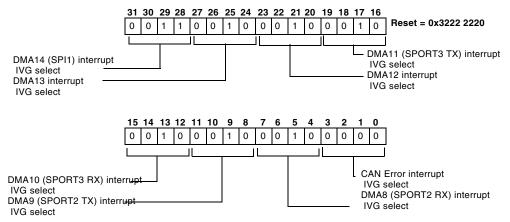

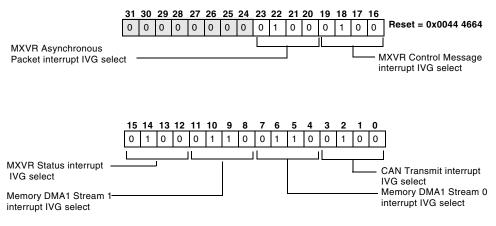

| System Interrupt Assignment (SIC_IARx) Registers    | 4-33 |

| Core Event Controller Registers                     | 4-38 |

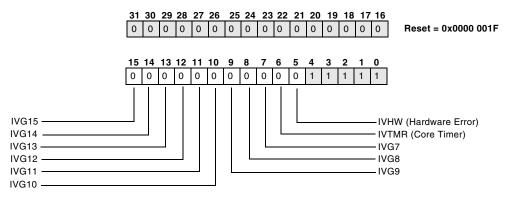

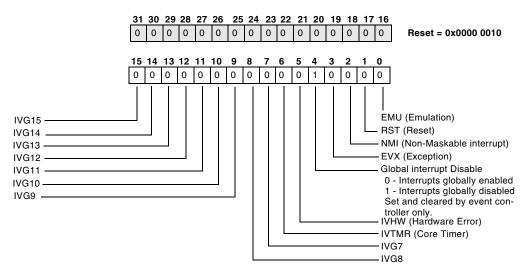

| Core Interrupt Mask (IMASK) Register                | 4-39 |

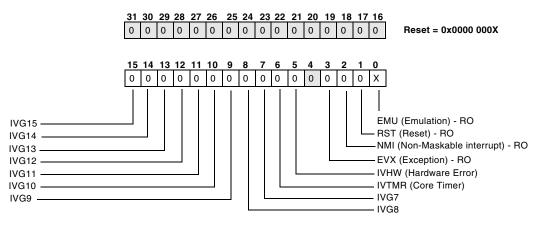

| Core Interrupt Latch (ILAT) Register                | 4-40 |

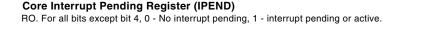

| Core Interrupts Pending (IPEND) Register            | 4-41 |

| Global Enabling/Disabling of Interrupts             | 4-42 |

| Event Vector Table                                  | 4-42 |

| Emulation                                           | 4-43 |

| Reset                                               | 4-44 |

| NMI (Non-Maskable Interrupt)                        | 4-45 |

| Exceptions                                          | 4-45 |

| Exceptions While Executing an Exception Handler     | 4-51 |

| Hardware-Error Interrupt                            | 4-52 |

| Core Timer                                          | 4-53 |

| General-Purpose Interrupts (IVG7-IVG15)             | 4-53 |

| Servicing Interrupts                                | 4-54 |

| Nesting of Interrupts 4-55                                  |

|-------------------------------------------------------------|

| Non-Nested Interrupts 4-55                                  |

| Nested Interrupts 4-57                                      |

| Example Prolog Code for Nested Interrupt Service<br>Routine |

| Example Epilog Code for Nested Interrupt Service<br>Routine |

| Logging of Nested Interrupt Requests 4-59                   |

| Exception Handling 4-60                                     |

| Deferring Exception Processing 4-61                         |

| Example Code for an Exception Handler 4-61                  |

| Example Code for an Exception Routine 4-63                  |

| Example Code for Using Hardware Loops in an ISR 4-63        |

| Other Usability Issues                                      |

| Executing RTX, RTN, or RTE in a Lower Priority Event 4-65   |

| Recommendation for Allocating the System Stack 4-65         |

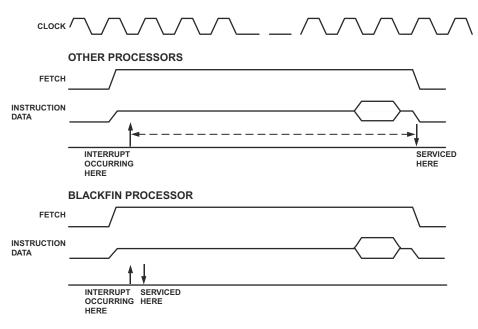

| Latency in Servicing Events 4-66                            |

## DATA ADDRESS GENERATORS

| Addressing With DAGs                                | 5-3  |

|-----------------------------------------------------|------|

| Frame and Stack Pointers                            | 5-5  |

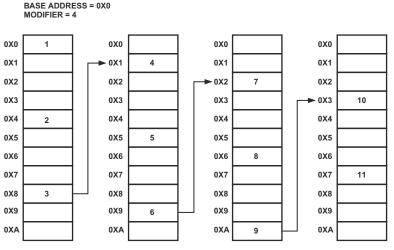

| Addressing Circular Buffers                         | 5-6  |

| Addressing With Bit-reversed Addresses              | 5-9  |

| Indexed Addressing With Index and Pointer Registers | 5-10 |

| Auto-increment and Auto-decrement Addressing        | 5-10 |

| Pre-modify Stack Pointer Addressing      | 5-11 |

|------------------------------------------|------|

| Indexed Addressing With Immediate Offset | 5-11 |

| Post-modify Addressing                   | 5-12 |

| Modifying DAG and Pointer Registers      | 5-13 |

| Memory Address Alignment                 | 5-13 |

| DAG Instruction Summary                  | 5-16 |

## MEMORY

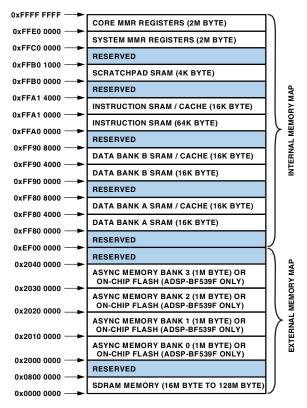

| Memory Architecture               | 6-1 |

|-----------------------------------|-----|

| Overview of Internal Memory       | 6-4 |

| Overview of Scratchpad Data SRAM  | 6-5 |

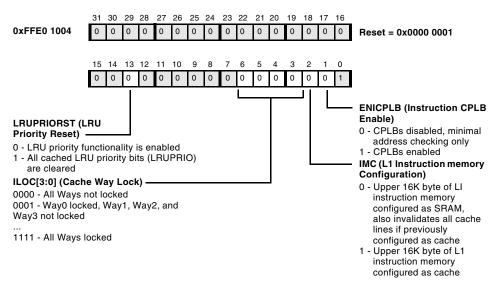

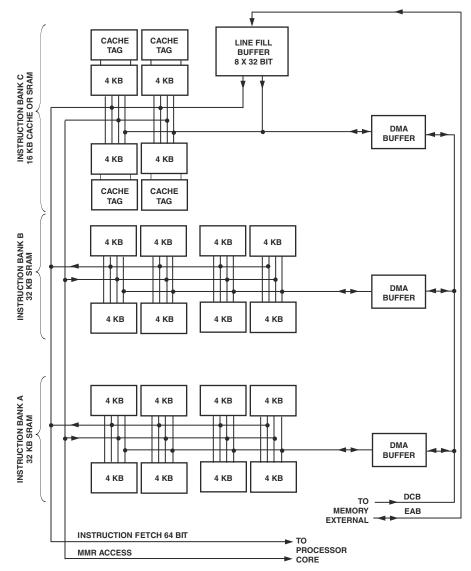

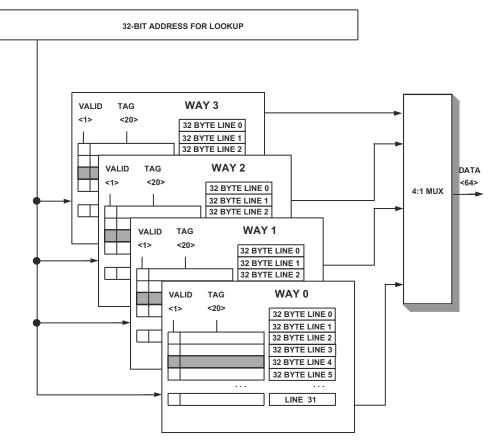

| L1 Instruction Memory             | 6-6 |

| IMEM_CONTROL Register             | 6-6 |

| L1 Instruction SRAM               | 6-8 |

| L1 Instruction Cache              | -11 |

| Cache Lines                       | -11 |

| Cache Hits and Misses 6           | -14 |

| Cache Line Fills 6                | -15 |

| Line Fill Buffer 6                | -15 |

| Cache Line Replacement 6          | -15 |

| Instruction Cache Management      | -17 |

| Instruction Cache Locking by Line | -17 |

| Instruction Cache Locking by Way  | -18 |

| Instruction Cache Invalidation    | -19 |

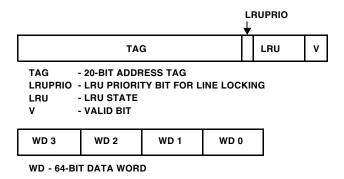

| Instruction Test Registers                            | 0 |

|-------------------------------------------------------|---|

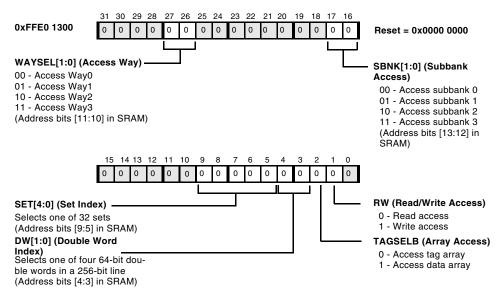

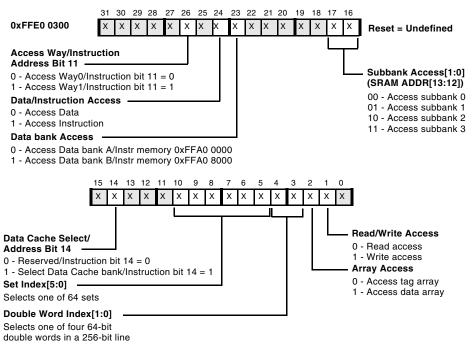

| Instruction Test Command (ITEST_COMMAND) Register 6-2 | 1 |

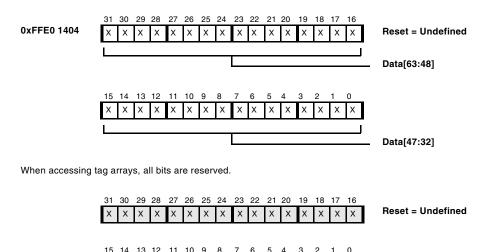

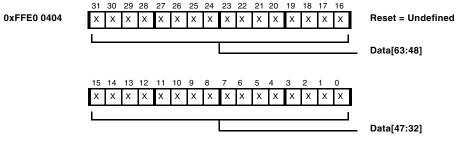

| Instruction Test Data (ITEST_DATA1) Register          | 2 |

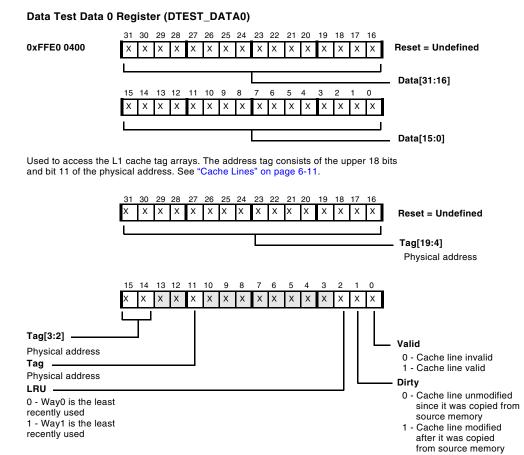

| Instruction Test Data 0 (ITEST_DATA0) Register 6-23   | 3 |

| L1 Data Memory                                        | 4 |

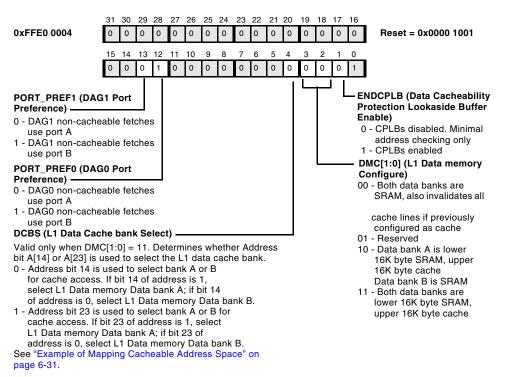

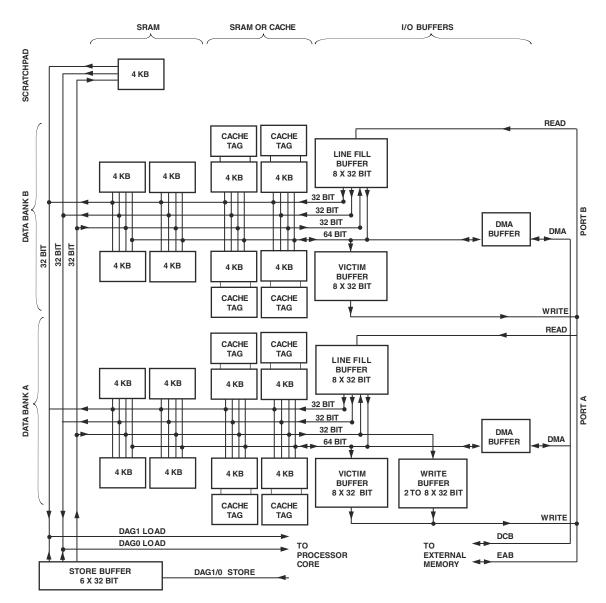

| Data Memory Control (DMEM_CONTROL) Register 6-24      | 4 |

| L1 Data SRAM                                          | 7 |

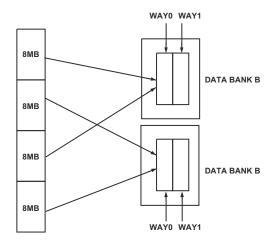

| L1 Data Cache 6-30                                    | 0 |

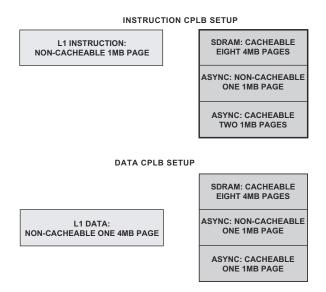

| Example of Mapping Cacheable Address Space            | 1 |

| Data Cache Access                                     | 4 |

| Cache Write Method 6-3                                | 5 |

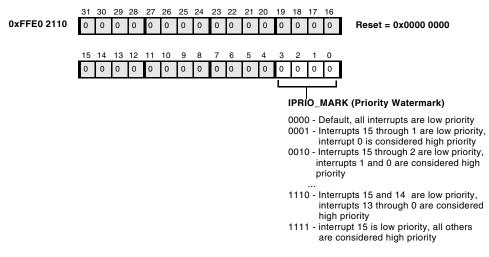

| Interrupt Priority Register and Write Buffer Depth    | 6 |

| Data Cache Control Instructions                       | 8 |

| Data Cache Invalidation                               | 8 |

| Data Test Registers                                   | 9 |

| Data Test Command (DTEST_COMMAND) Register 6-40       | 0 |

| Data Test Data (DTEST_DATA1) Register                 | 1 |

| Data Test Data (DTEST_DATA0) Register 6-42            | 2 |

| External Memory                                       | 3 |

| On-Chip Flash Memory                                  | 3 |

| Memory Protection and Properties                      | 3 |

| Memory Management Unit 6-44                           | 4 |

| Memory Pages 6-4                                      | 5 |

| Memory Page Attributes 6-40                           |   |

| Page Descriptor Table                                                      | 6-47 |

|----------------------------------------------------------------------------|------|

| CPLB Management                                                            | 6-48 |

| MMU Application                                                            | 6-49 |

| Examples of Protected Memory Regions                                       | 6-51 |

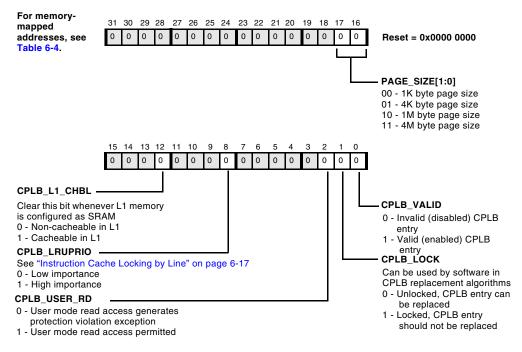

| Instruction CPLB Data (ICPLB_DATAx) Registers                              | 6-51 |

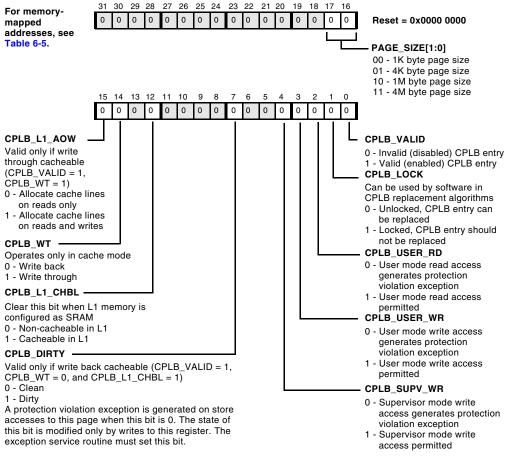

| Data CPLB Data (DCPLB_DATAx) Registers                                     | 6-53 |

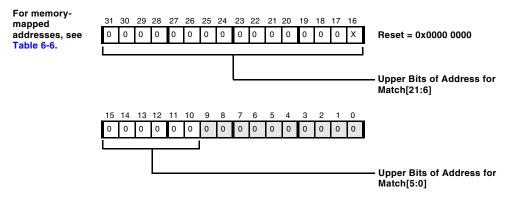

| Data CPLB Address (DCPLB_ADDRx) Registers                                  | 6-56 |

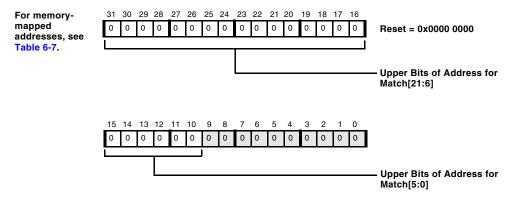

| Instruction CPLB Address (ICPLB_ADDRx) Registers                           | 6-58 |

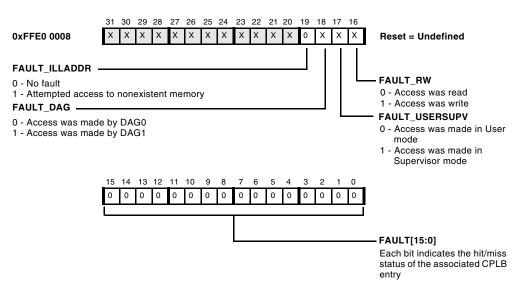

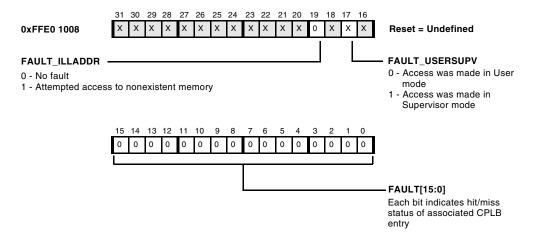

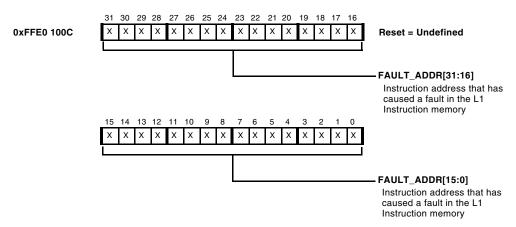

| Instruction and Data CPLB Status (ICPLB_STATUS,<br>DCPLB_STATUS) Registers | 6-59 |

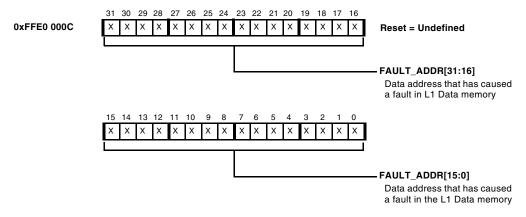

| Instruction and Data CPLB Fault Address                                    |      |

| (ICPLB_FAULT_ADDR, DCPLB_FAULT_ADDR)<br>Registers                          | 6-60 |

| Memory Transaction Model                                                   | 6-62 |

| Load/Store Operation                                                       | 6-63 |

| Interlocked Pipeline                                                       | 6-64 |

| Ordering of Loads and Stores                                               | 6-65 |

| Synchronizing Instructions                                                 | 6-66 |

| Speculative Load Execution                                                 | 6-67 |

| Conditional Load Behavior                                                  | 6-68 |

| Working With Memory                                                        | 6-69 |

| Alignment                                                                  | 6-69 |

| Cache Coherency                                                            | 6-69 |

| Atomic Operations                                                          | 6-70 |

| Memory-mapped Registers           | 6-70 |

|-----------------------------------|------|

| Core MMR Programming Code Example | 6-71 |

| Terminology                       | 6-72 |

## CHIP BUS HIERARCHY

| Internal Interfaces                                 |

|-----------------------------------------------------|

| Internal Clocks                                     |

| Core Overview                                       |

| System Overview                                     |

| System Interfaces                                   |

| Peripheral Access Bus (PAB)                         |

| PAB Arbitration                                     |

| PAB Performance                                     |

| PAB Agents (Masters, Slaves)                        |

| DMA Access Buses (DAB0/DAB1), DMA Core Buses        |

| (DCB0/DCB1/DCB2), DMA External Buses<br>(DEB0/DEB1) |

| DABx, DCBx, and DEBx Arbitration7-7                 |

| DAB, DCB, and DEB Performance                       |

| DAB Bus Agents (Masters) 7-10                       |

| External Access Bus (EAB) 7-10                      |

| EAB Arbitration                                     |

| EAB Performance                                     |

## DYNAMIC POWER MANAGEMENT

| Clocking 8-1                                    |

|-------------------------------------------------|

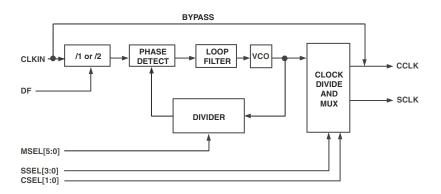

| Phase Locked Loop and Clock Control 8-2         |

| PLL Overview                                    |

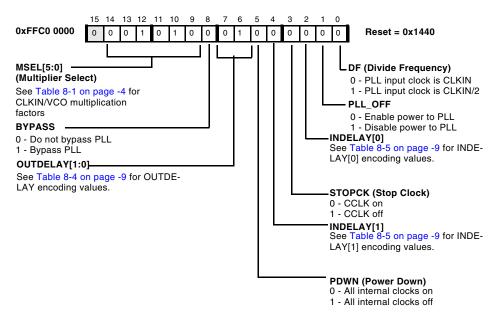

| PLL Clock Multiplier Ratios 8-3                 |

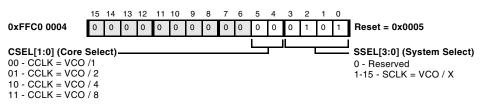

| Core Clock/System Clock Ratio Control 8-4       |

| PLL Registers                                   |

| PLL Divide (PLL_DIV) Register 8-7               |

| PLL Control (PLL_CTL) Register 8-7              |

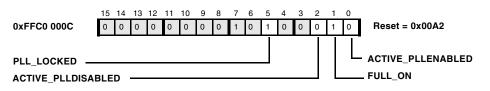

| PLL Status (PLL_STAT) Register 8-10             |

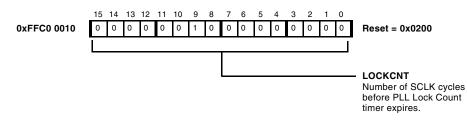

| PLL Lock Count (PLL_LOCKCNT) Register 8-11      |

| Dynamic Power Management Controller 8-12        |

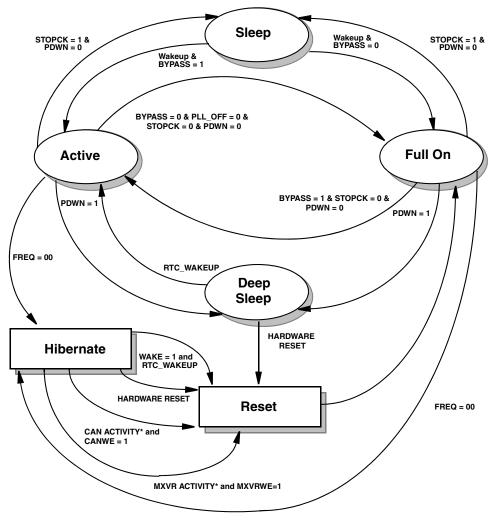

| Operating Modes 8-13                            |

| Dynamic Power Management Controller States 8-13 |

| Full On Mode 8-14                               |

| Active Mode 8-14                                |

| Sleep Mode 8-14                                 |

| Deep Sleep Mode 8-15                            |

| Hibernate State                                 |

| Operating Mode Transitions 8-16                 |

| Programming Operating Mode Transitions 8-19     |

| PLL Programming Sequence 8-19                   |

| PLL Programming Sequence Continues 8-22         |

| Examples                                        |

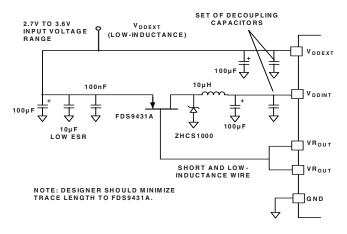

| Dynamic Supply Voltage Control              | 8-25 |

|---------------------------------------------|------|

| Power Supply Management                     | 8-25 |

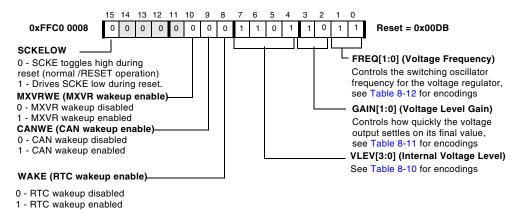

| Voltage Regulator Control (VR_CTL) Register | 8-26 |

| Changing Voltage                            | 8-30 |

| Powering Down the Core (Hibernate State)    | 8-31 |

## DIRECT MEMORY ACCESS

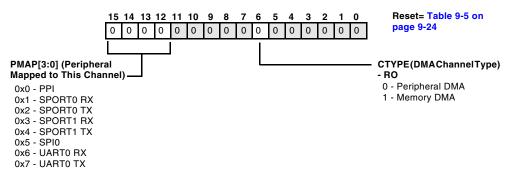

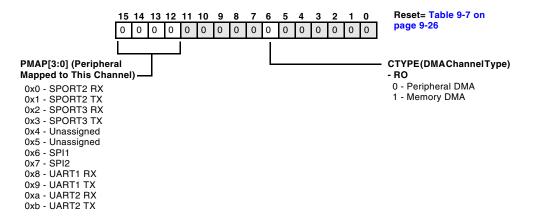

| DMA and Memory DMA MMRs 9-3                                                          |

|--------------------------------------------------------------------------------------|

| Naming Conventions for DMA MMRs                                                      |

| Naming Conventions for Memory DMA Registers 9-8                                      |

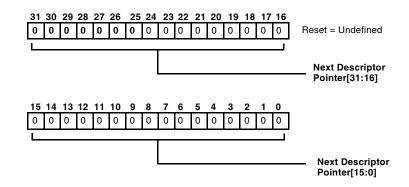

| Next Descriptor Pointer (DMAx_NEXT_DESC_PTR /<br>MDMAx_yy_NEXT_DESC_PTR) Registers   |

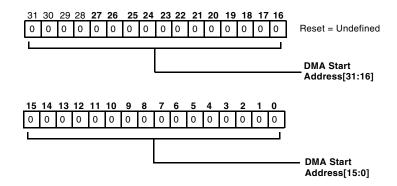

| Start Address Register<br>(DMAx_START_ADDR/MDMAx_yy_START_ADDR) 9-11                 |

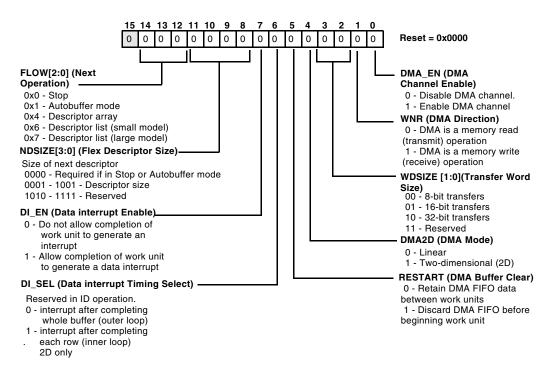

| DMA Configuration Register (DMAx_CONFIG /<br>MDMAx_yy_CONFIG)                        |

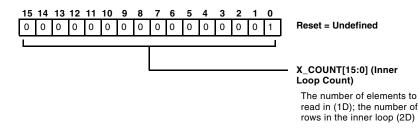

| Inner Loop Count (DMAx_X_COUNT,<br>MDMAx_yy_X_COUNT) Registers                       |

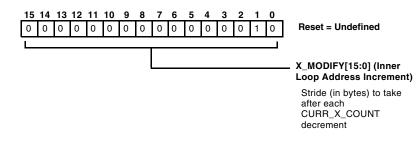

| Inner Loop Address Increment (DMAx_X_MODIFY,<br>MDMAx_yy_X_MODIFY) Registers         |

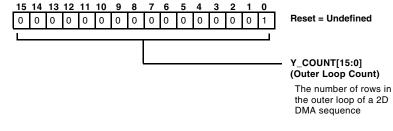

| Outer Loop Count (DMAx_Y_COUNT,<br>MDMAx_yy_Y_COUNT) Registers                       |

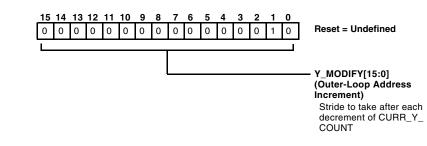

| Outer Loop Address Increment (DMAx_Y_MODIFY,<br>MDMAx_yy_Y_MODIFY) Registers         |

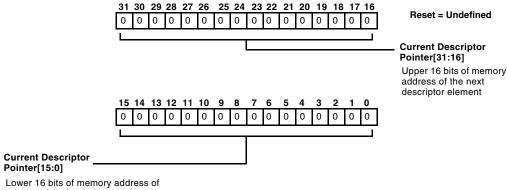

| Current Descriptor Pointer (DMAx_CURR_DESC_PTR,<br>MDMAx_yy_CURR_DESC_PTR) Registers |

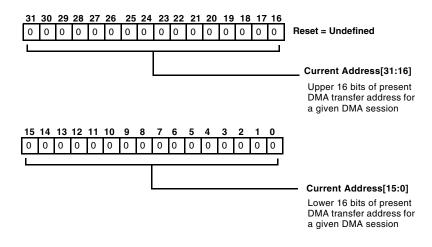

| Current Address (DMAx_CURR_ADDR,<br>MDMAx_yy_CURR_ADDR) Registers                | 9-19 |

|----------------------------------------------------------------------------------|------|

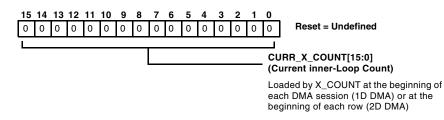

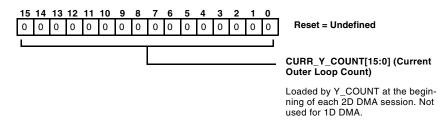

| Current Inner Loop Count (DMAx_CURR_X_COUNT,<br>MDMAx_yy_CURR_X_COUNT) Registers | 9-20 |

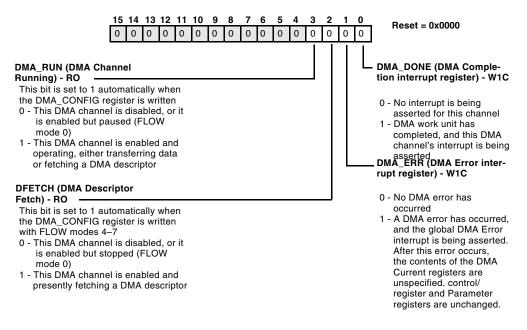

| Interrupt Status Register (DMAx_IRQ_STATUS /<br>MDMAx_yy_IRQ_STATUS)             | 9-28 |

| Flex Descriptor Structure                                                        | 9-31 |

| Two-Dimensional DMA                                                              | 9-33 |

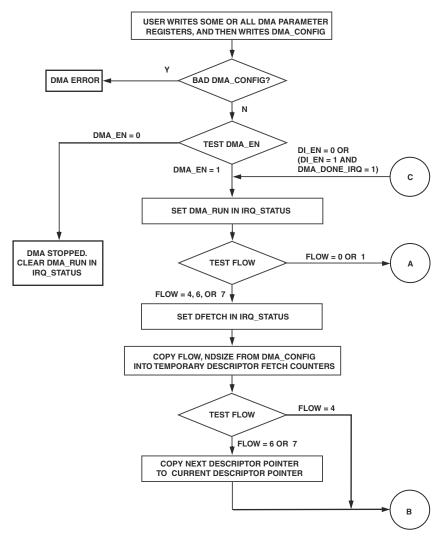

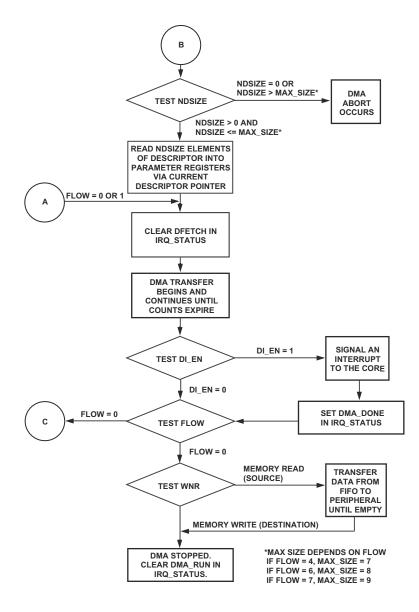

| DMA Operation Flow                                                               | 9-35 |

| DMA Startup                                                                      | 9-38 |

| DMA Refresh                                                                      | 9-40 |

| To Stop DMA Transfers                                                            | 9-41 |

| Software Management of DMA                                                       | 9-42 |

| Synchronization of Software and DMA                                              | 9-43 |

| Single-buffer DMA Transfers                                                      | 9-45 |

| Continuous Transfers Using Autobuffering                                         | 9-45 |

| Descriptor Structures                                                            | 9-47 |

| Descriptor Queue Management                                                      | 9-48 |

| Descriptor Queue Using Interrupts on Every Descriptor                            | 9-49 |

| Descriptor Queue Using Minimal Interrupts                                        | 9-50 |

| More 2D DMA Examples                                                             | 9-52 |

| Memory DMA                                                                       | 9-53 |

| MDMA Bandwidth                                                                   | 9-55 |

| MDMA Priority and Scheduling                                                     | 9-56 |

| DMA Controller Errors (Aborts)                                                   |      |

| DMA Performance: Prioritization and Optimization                                                                         | 9-60 |

|--------------------------------------------------------------------------------------------------------------------------|------|

| Prioritization and Traffic Control                                                                                       | 9-62 |

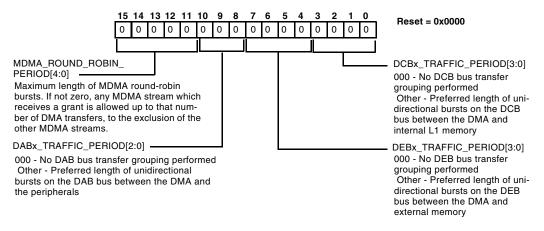

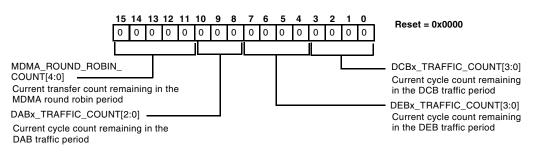

| DMA Traffic Control Counter Period (DMACx_TC_PER)<br>Register and DMA Traffic Control Counter<br>(DMACx_TC_CNT) Register | 9-65 |

| Urgent DMA Transfers                                                                                                     | 9-67 |

| SPI COMPATIBLE PORT CONTROLLERS                                                                                          |      |

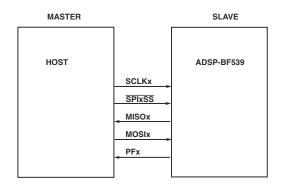

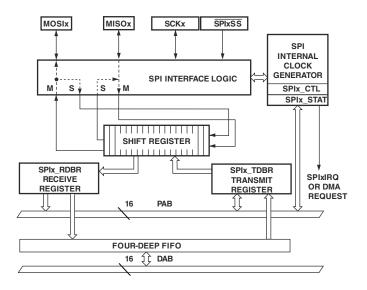

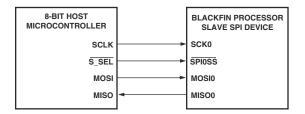

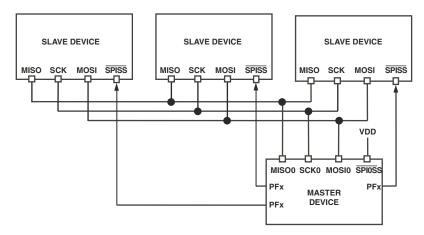

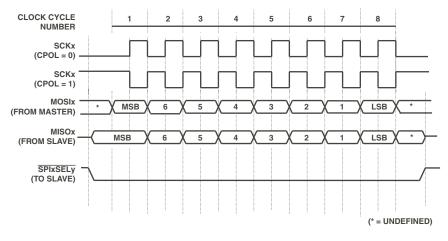

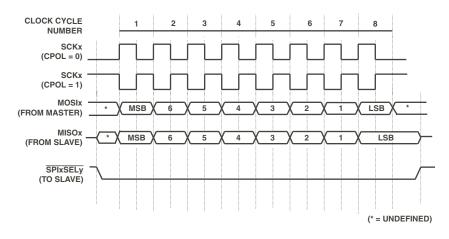

| Interface Signals 1                                                                                                      | 10-4 |

| Serial Peripheral Interface Clock Signals (SCKx) 1                                                                       | 10-4 |

| Serial Peripheral Interface Slave Select Input Signals<br>(SPIxSS)                                                       | 10-5 |

| Master Out Slave In (MOSIx)                                                                                              | 10-5 |

| Master In Slave Out (MISOx)                                                                                              | 10-6 |

| Interrupt Output 1                                                                                                       | 10-7 |

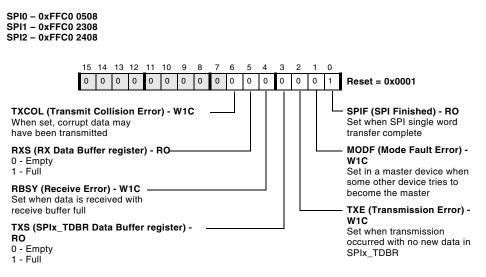

| SPI Registers                                                                                                            | 10-8 |

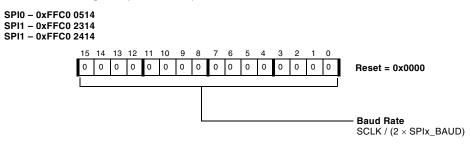

| SPI BAUD Rate (SPIx_BAUD) Register 1                                                                                     | 10-8 |

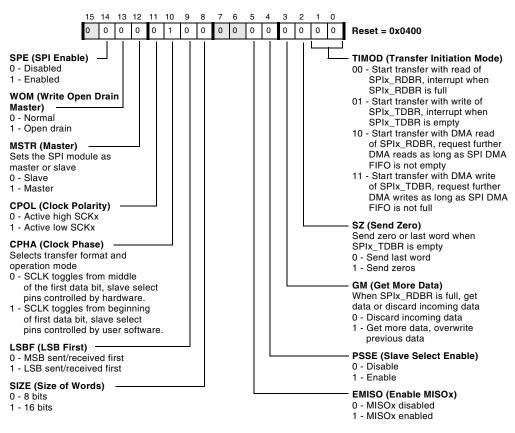

| SPI Control (SPIx_CTL) Register 1                                                                                        | 10-9 |

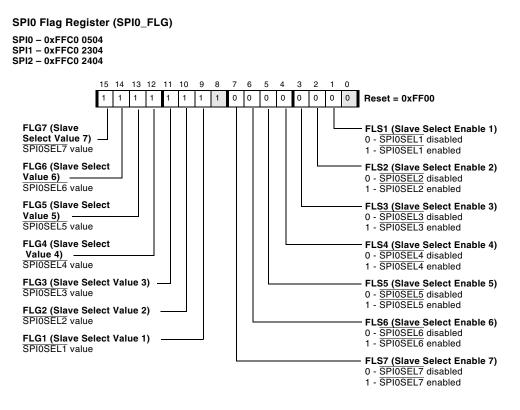

| SPI Flag (SPIx_FLG) Register 10                                                                                          | 0-10 |

| Slave Select Inputs 10                                                                                                   | 0-14 |

| Use of FLS Bits in SPI0_FLG for Multiple Slave SPI<br>Systems                                                            | 0-14 |

| Special Considerations for SPI1 and SPI2 Slave Control 10                                                                | 0-16 |

| SPI Status (SPIx_STAT) Register 10                                                                                       | 0-17 |

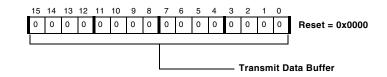

| SPI Transmit Data Buffer (SPIx_TDBR) Register 10                                                                         | 0-18 |

SPI Receive Data Buffer (SPIx\_RDBR) Register ..... 10-19

| SPI Receive Data Buffer Shadow (SPIx_SHADOW)     |       |

|--------------------------------------------------|-------|

| Register                                         | 10-20 |

| Register Functions                               | 10-21 |

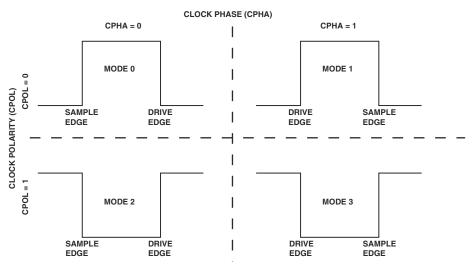

| SPI Transfer Formats                             | 10-22 |

| SPI General Operation                            | 10-25 |

| Clock Signals                                    | 10-26 |

| Master Mode Operation                            | 10-26 |

| Transfer Initiation From Master (Transfer Modes) | 10-27 |

| Slave Mode Operation                             | 10-28 |

| Slave Ready for a Transfer                       | 10-30 |

| Error Signals and Flags                          | 10-30 |

| Mode Fault Error (MODF)                          | 10-30 |

| Transmission Error (TXE)                         | 10-32 |

| Reception Error (RBSY)                           | 10-32 |

| Transmit Collision Error (TXCOL)                 | 10-32 |

| Beginning and Ending an SPI Transfer             | 10-32 |

| DMA                                              | 10-34 |

| DMA Functionality                                | 10-34 |

| Master Mode DMA Operation                        | 10-35 |

| Slave Mode DMA Operation                         | 10-38 |

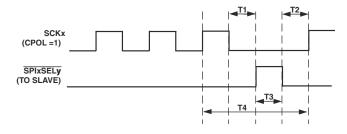

| Timing                                           | 10-40 |

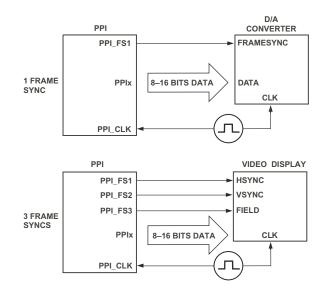

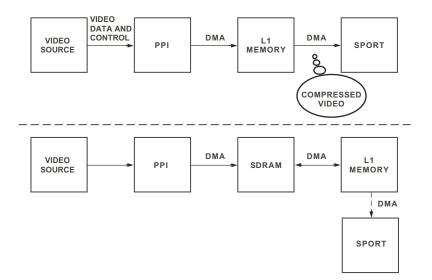

## PARALLEL PERIPHERAL INTERFACE

| PPI Registers 11-2                             |

|------------------------------------------------|

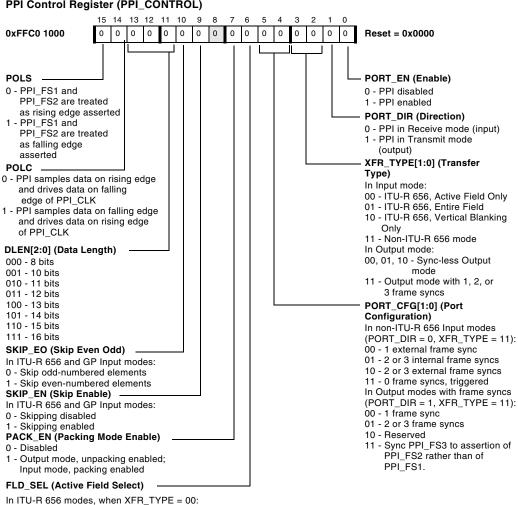

| PPI_CONTROL Register 11-3                      |

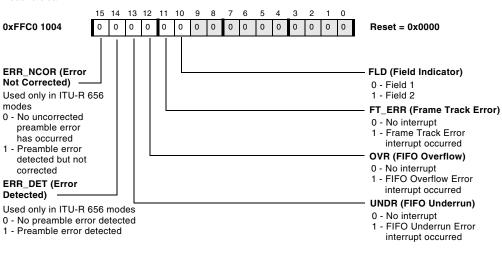

| PPI_STATUS Register 11-8                       |

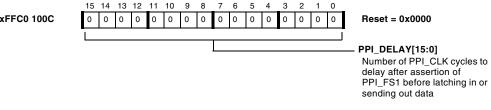

| PPI_DELAY Register 11-10                       |

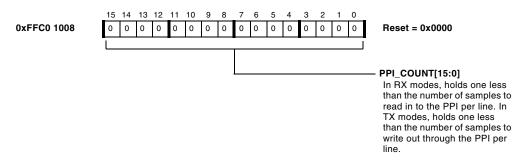

| PPI_COUNT Register 11-10                       |

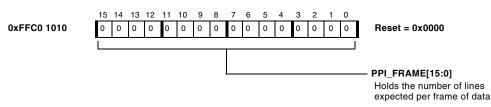

| PPI_FRAME Register 11-11                       |

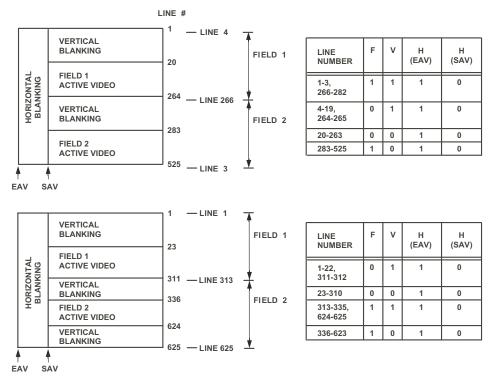

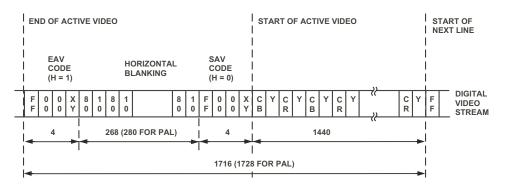

| ITU-R 656 Modes 11-13                          |

| ITU-R 656 Background 11-13                     |

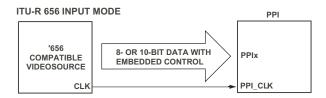

| ITU-R 656 Input Modes 11-16                    |

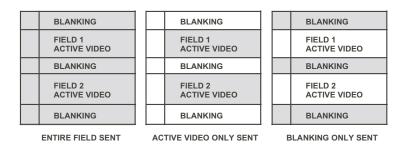

| Entire Field 11-17                             |

| Active Video Only 11-18                        |

| Vertical Blanking Interval (VBI) only 11-18    |

| ITU-R 656 Output Mode 11-18                    |

| Frame Synchronization in ITU-R 656 Modes 11-19 |

| General-Purpose PPI Modes 11-20                |

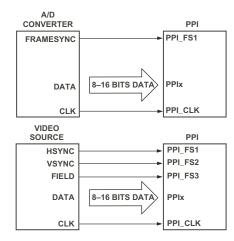

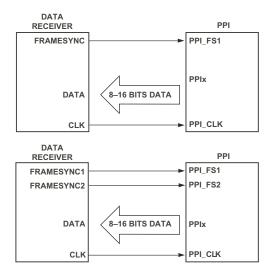

| Data Input (RX) Modes 11-22                    |

| No Frame Syncs 11-23                           |

| 1, 2, or 3 External Frame Syncs 11-24          |

| 2 or 3 Internal Frame Syncs 11-25              |

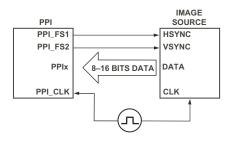

| Data Output (TX) Modes 11-25                   |

| No Frame Syncs 11-25                           |

| 1 or 2 External Frame Syncs 11-26              |

| 1, 2, or 3 Internal Frame Syncs 11-27          |

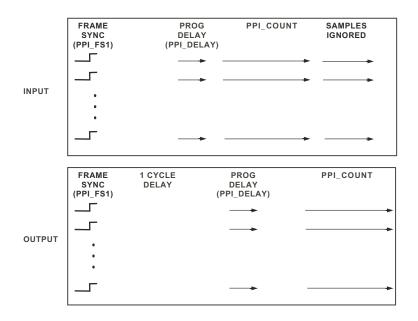

| Frame Synchronization in GP Modes | 11-28 |

|-----------------------------------|-------|

| Modes with Internal Frame Syncs   | 11-28 |

| Modes with External Frame Syncs   | 11-30 |

| DMA Operation                     | 11-31 |

| Data Transfer Scenarios           | 11-32 |

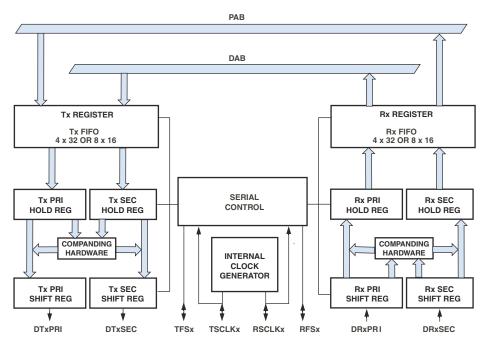

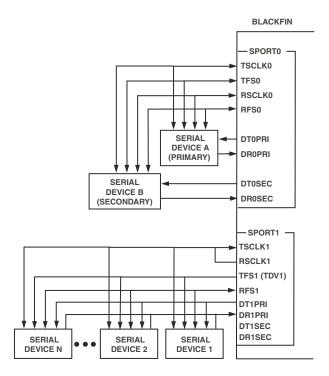

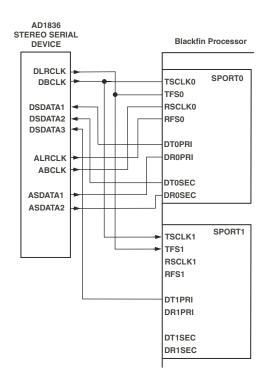

## SERIAL PORT CONTROLLERS

| SPORT Operation                                                                   | . 12-8 |

|-----------------------------------------------------------------------------------|--------|

| SPORT Disable                                                                     | . 12-9 |

| Setting SPORT Modes                                                               | 12-10  |

| Register Writes and Effective Latency                                             | 12-10  |

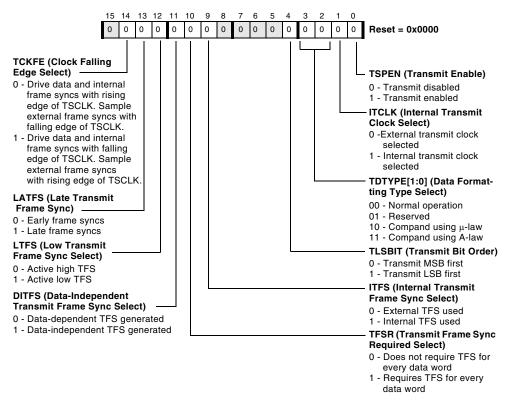

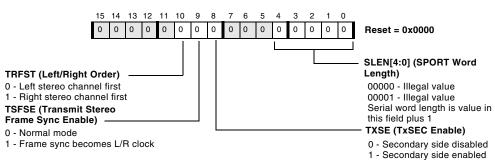

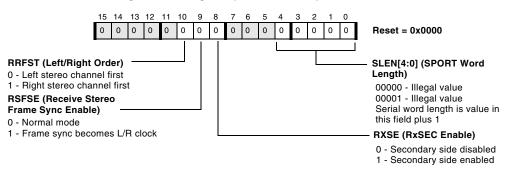

| SPORT Transmit Configuration (SPORTx_TCR1,<br>SPORTx_TCR2) Registers              | 12-11  |

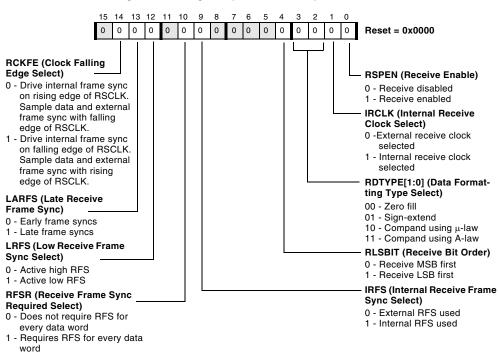

| SPORT Receive Configuration (SPORTx_RCR1,<br>SPORTx_RCR2) Registers               | 12-16  |

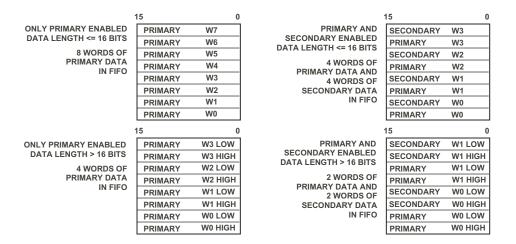

| Data Word Formats                                                                 | 12-21  |

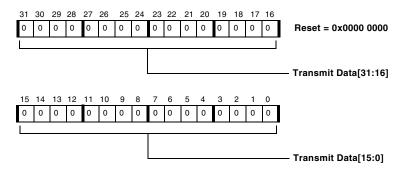

| SPORT Transmit Data (SPORTx_TX) Register                                          | 12-22  |

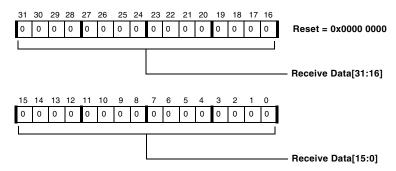

| SPORT Receive Data (SPORTx_RX) Register                                           | 12-24  |

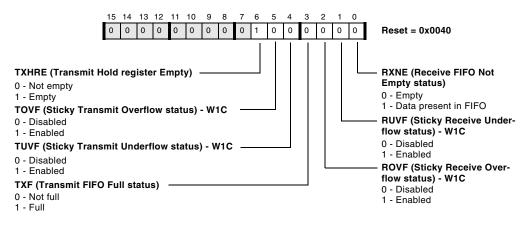

| SPORT Status (SPORTx_STAT) Register                                               | 12-26  |

| SPORT RX, TX, and Error Interrupts                                                | 12-28  |

| PAB Errors                                                                        | 12-29  |

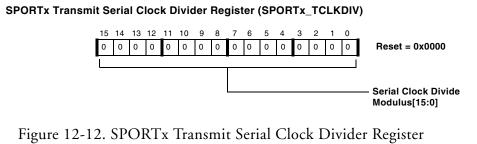

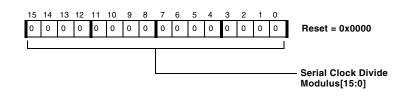

| SPORT Transmit Serial Clock Divider (SPORTx_TCLKDIV,<br>SPORTx_RCLKDIV) Registers | 12-29  |

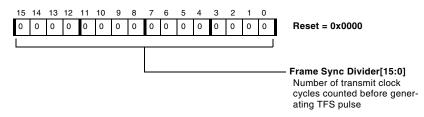

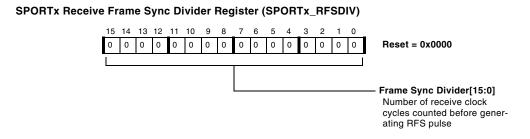

| SPORT Transmit Frame Sync Divider (SPORTx_TFSDIV,<br>SPORTx_RFSDIV) Register      | 12-30  |

| Clock and Frame Sync Frequencies                                  | 12-32 |

|-------------------------------------------------------------------|-------|

| Maximum Clock Rate Restrictions                                   | 12-33 |

| Frame Sync & Clock Example                                        | 12-33 |

| Word Length                                                       | 12-34 |

| Bit Order                                                         | 12-34 |

| Data Type                                                         | 12-35 |

| Companding                                                        | 12-35 |

| Clock Signal Options                                              | 12-36 |

| Frame Sync Options                                                | 12-37 |

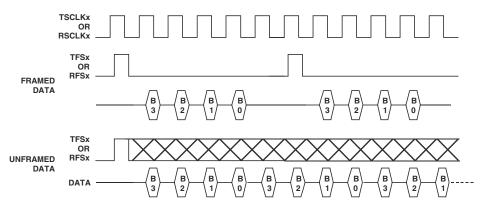

| Framed Versus Unframed                                            | 12-37 |

| Internal Versus External Frame Syncs                              | 12-38 |

| Active Low Versus Active High Frame Syncs                         | 12-39 |

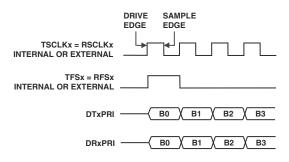

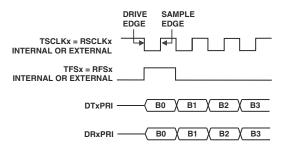

| Sampling Edge for Data and Frame Syncs                            | 12-40 |

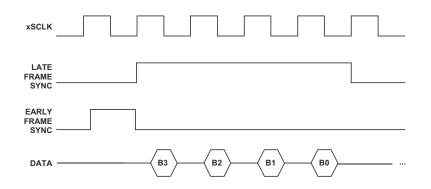

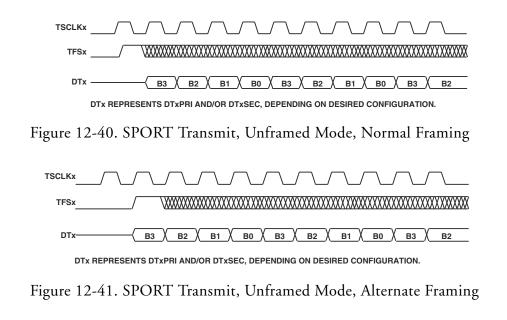

| Early Versus Late Frame Syncs<br>(Normal Versus Alternate Timing) | 12-42 |

| Data Independent Transmit Frame Sync                              |       |

| Moving Data Between SPORTs and Memory                             | 12-44 |

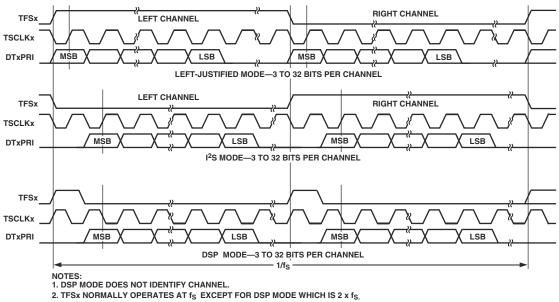

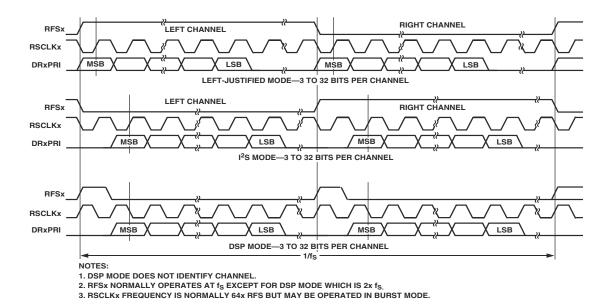

| Stereo Serial Operation                                           | 12-45 |

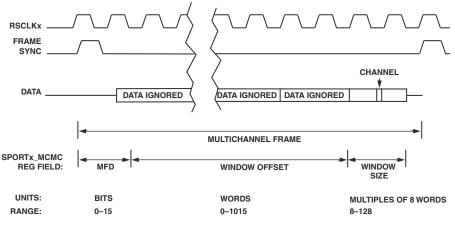

| Multichannel Operation                                            | 12-49 |

| SPORT Multichannel Configuration (SPORTx_MCMCn)<br>Registers      | 12-51 |

| Multichannel Enable                                               |       |

| Frame Syncs in Multichannel Mode                                  | 12-54 |

| The Multichannel Frame                                            |       |

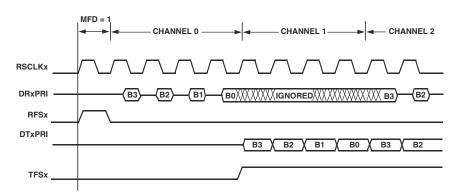

| Multichannel Frame Delay                                          | 12-56 |

| Window Size                                                       | 12-58 |

|-------------------------------------------------------------------|-------|

| Window Offset                                                     | 12-58 |

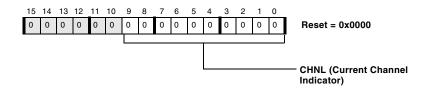

| SPORT Current Channel (SPORTx_CHNL) Register                      | 12-59 |

| Other Multichannel Fields in SPORTx_MCMC2                         | 12-60 |

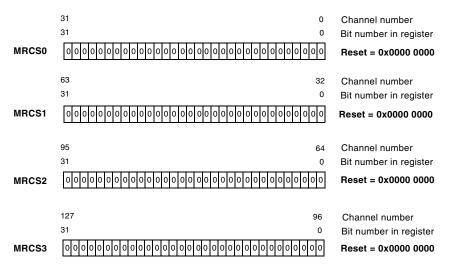

| Channel Selection Register                                        | 12-60 |

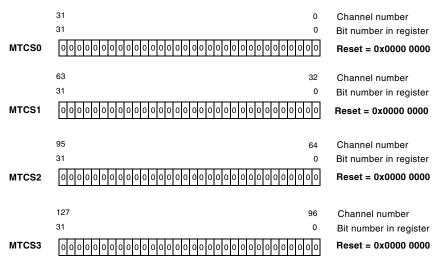

| SPORT Multichannel Receive Selection<br>(SPORTx_MRCSn) Registers  | 12-62 |

| SPORT Multichannel Transmit Selection<br>(SPORTx_MTCSn) Registers | 12-64 |

| Multichannel DMA Data Packing                                     | 12-66 |

| Support for H.100 Standard Protocol                               | 12-67 |

| 2X Clock Recovery Control                                         | 12-67 |

| SPORT Pin/Line Terminations                                       | 12-68 |

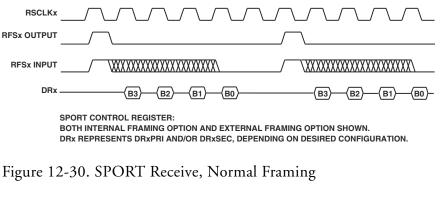

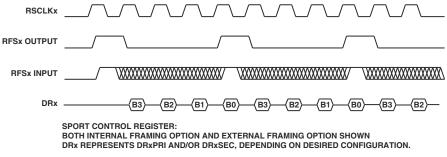

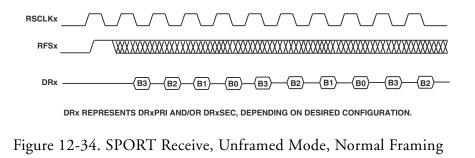

| Timing Examples                                                   | 12-68 |

|                                                                   |       |

## UART PORT CONTROLLERS

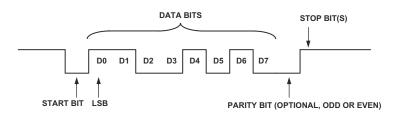

| Serial Communications                                | 13-2 |

|------------------------------------------------------|------|

| UART Control and Status Registers                    | 13-3 |

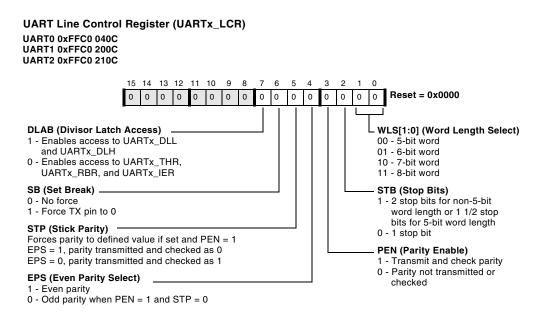

| UART Line Control (UARTx_LCR) Register               | 13-4 |

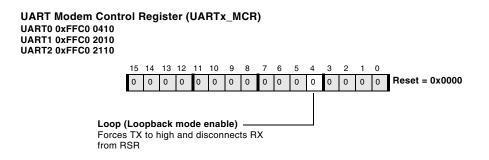

| UART Modem Control (UARTx_MCR) Register              | 13-4 |

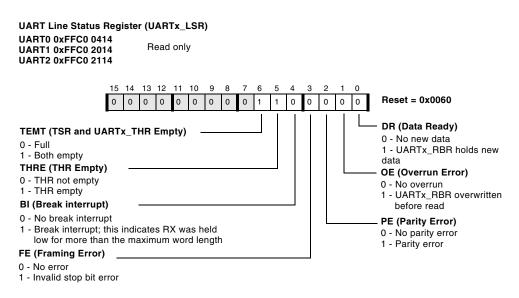

| UART Line Status (UARTx_LSR) Register                | 13-5 |

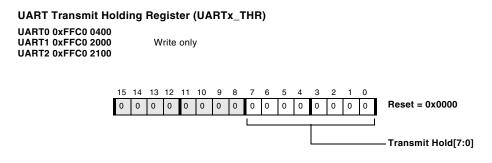

| UART Transmit Holding (UARTx_THR) Register           | 13-6 |

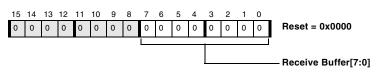

| UART Receive Buffer (UARTx_RBR) Register             | 13-7 |

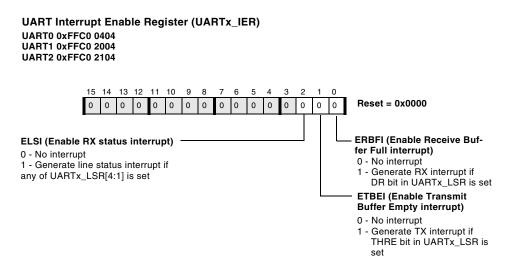

| UART Interrupt Enable (UARTx_IER) Register           | 13-8 |

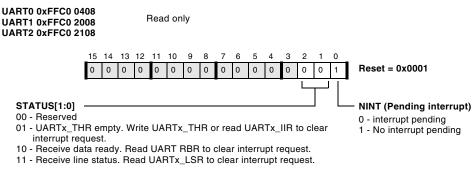

| UART Interrupt Identification (UARTx_IIR) Register 1 | 3-10 |

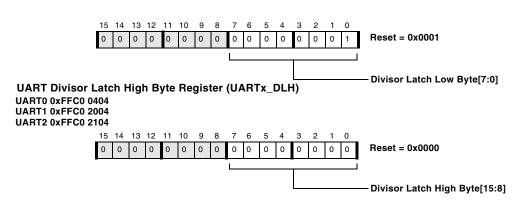

| UARTx_DLL and UARTx_DLH Registers         | 13-12 |

|-------------------------------------------|-------|

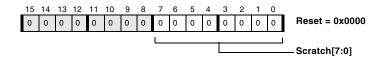

| UART Scratch (UARTx_SCR) Register         | 13-14 |

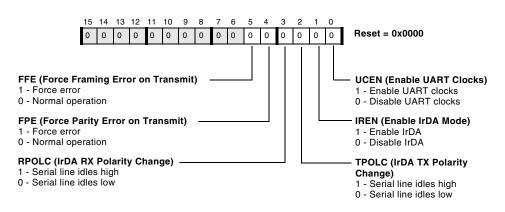

| UART Global Control (UARTx_GCTL) Register | 13-14 |

| Non-DMA Mode                              | 13-15 |

| DMA Mode                                  | 13-16 |

| Mixing Modes                              | 13-17 |

| IrDA Support                              | 13-18 |

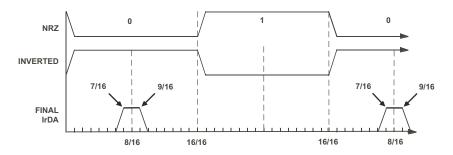

| IrDA Transmitter Description              | 13-19 |

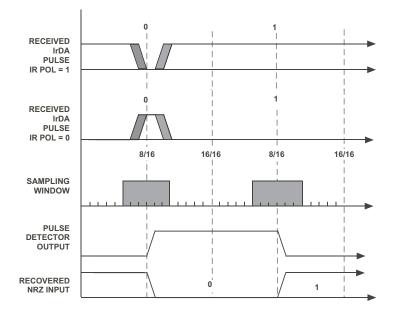

| IrDA Receiver Description                 | 13-20 |

|                                           |       |

## **PROGRAMMABLE FLAGS**

| Programmable Flag Registers (MMRs)                                                        | 14-5 |

|-------------------------------------------------------------------------------------------|------|

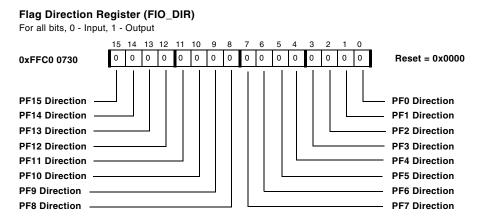

| Flag Direction (FIO_DIR) Register                                                         | 14-5 |

| Flag Value Registers Overview                                                             | 14-6 |

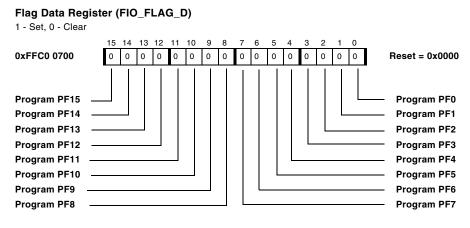

| Flag Data (FIO_FLAG_D) Register                                                           | 14-8 |

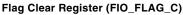

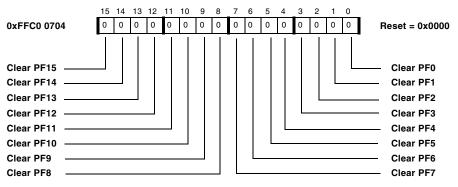

| Flag Set (FIO_FLAG_S), Flag Clear (FIO_FLAG_C), and<br>Flag Toggle (FIO_FLAG_T) Registers | 14-8 |

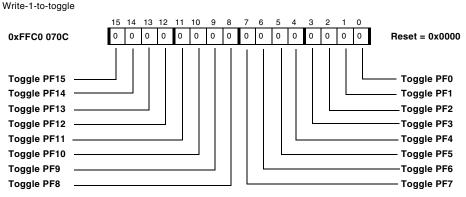

| Flag Mask Interrupt Registers Overview 1                                                  | 4-11 |

| Flag Interrupt Generation Flow 1                                                          | 4-12 |

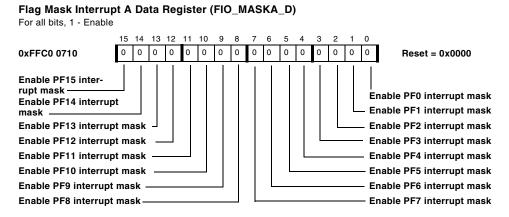

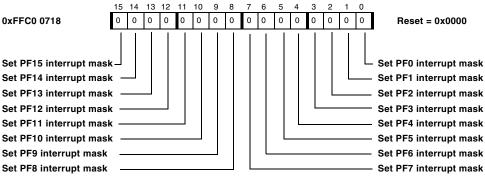

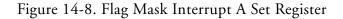

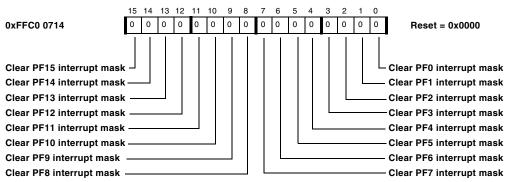

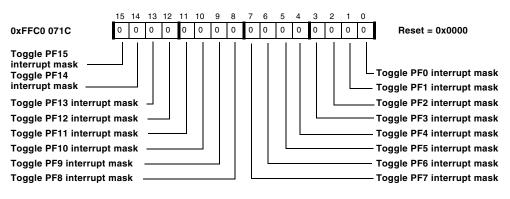

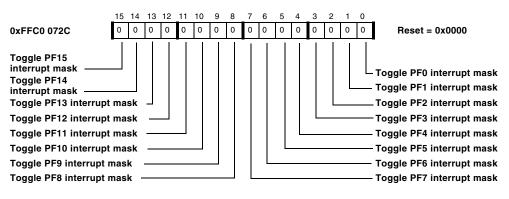

| Flag Interrupt A (FIO_MASKA_D, FIO_MASKA_C,<br>FIO_MASKA_S, FIO_MASKA_T) Registers 1      | 4-14 |

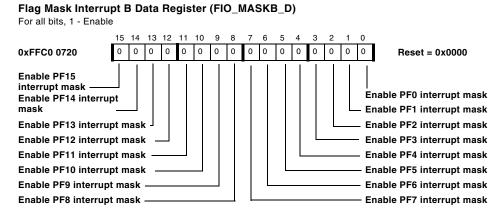

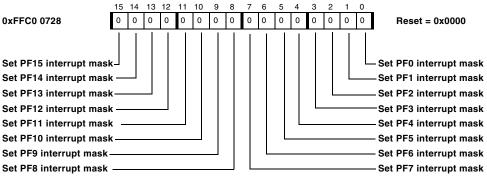

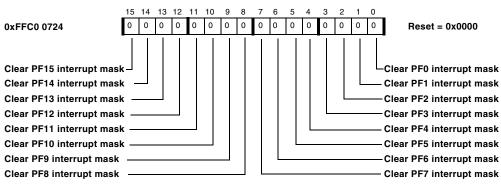

| Flag Interrupt B (FIO_MASKB_D, FIO_MASKB_C,<br>FIO_MASKB_S, FIO_MASKB_T) Registers 1      | 4-16 |

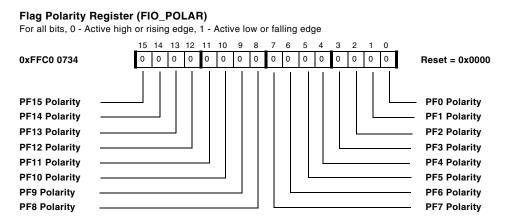

| Flag Polarity (FIO_POLAR) Register 1                                                      | 4-18 |

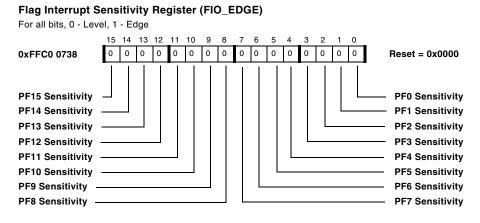

| Flag Interrupt Sensitivity (FIO_EDGE) Register 1                                          | 4-18 |

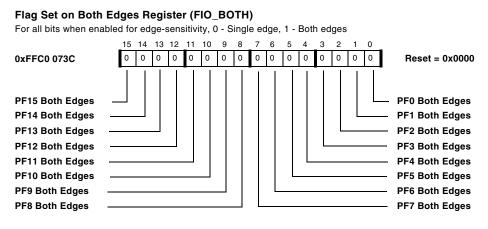

| Flag Set on Both Edges (FIO_BOTH) Register | 14-19 |

|--------------------------------------------|-------|

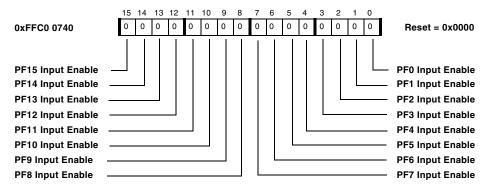

| Flag Input Enable (FIO_INEN) Register      | 14-20 |

| Performance/Throughput                     | 14-21 |

## GENERAL PURPOSE INPUT/OUTPUT PORTS

| GPIO Memory-Mapped Registers (MMRs) 15-                                             | 5 |

|-------------------------------------------------------------------------------------|---|

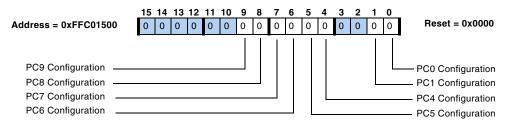

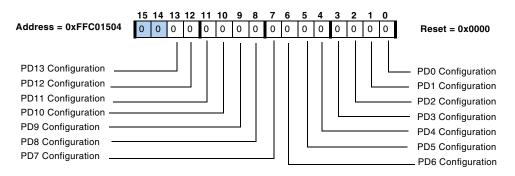

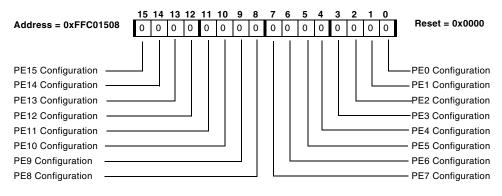

| GPIO Configuration (GPIO_x_CNFG) Register 15-                                       | 5 |

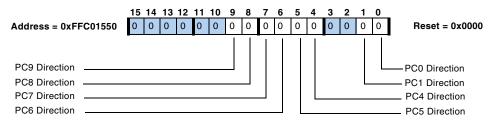

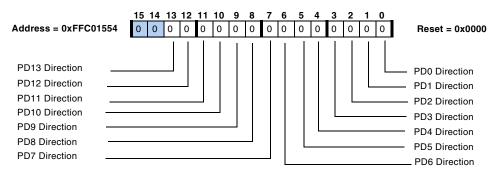

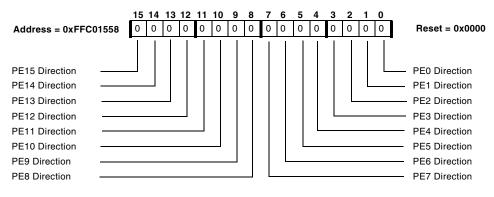

| GPIO Direction (GPIO_x_DIR) Register 15-                                            | 7 |

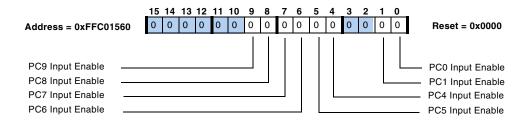

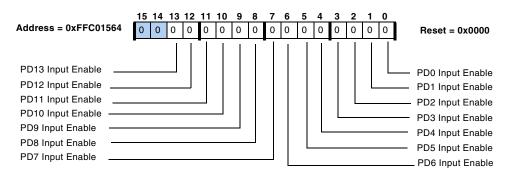

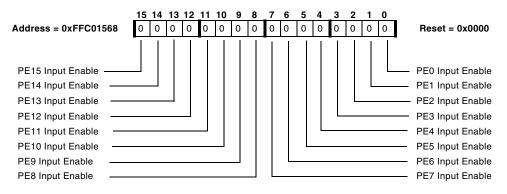

| GPIO Input Enable (GPIO_x_INEN) Register 15-                                        | 9 |

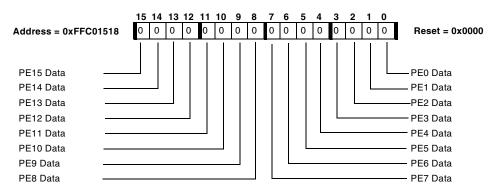

| GPIO Value Registers 15-1                                                           | 1 |

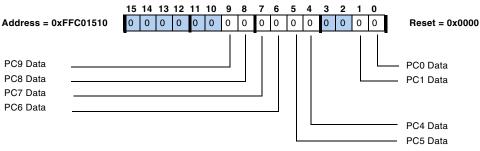

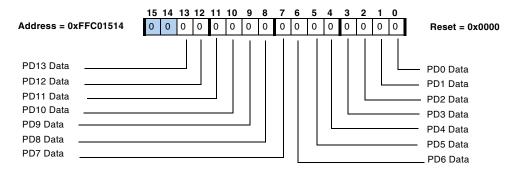

| GPIO Data (GPIO_x_D) Register 15-1                                                  | 2 |

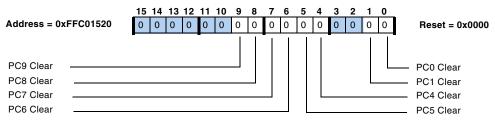

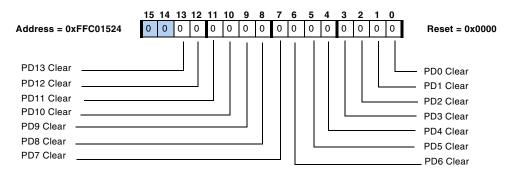

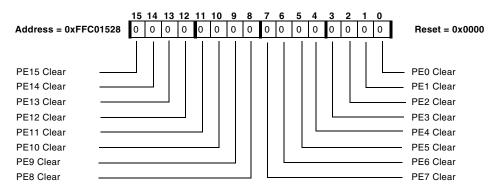

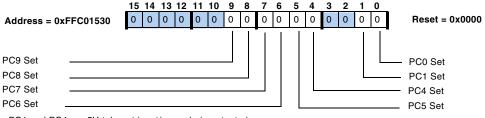

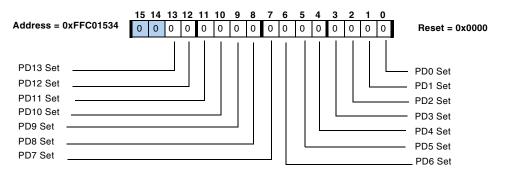

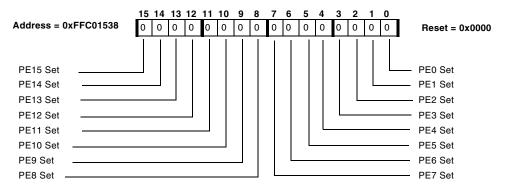

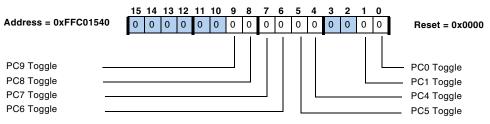

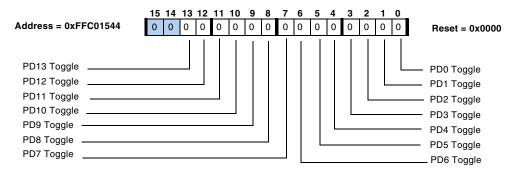

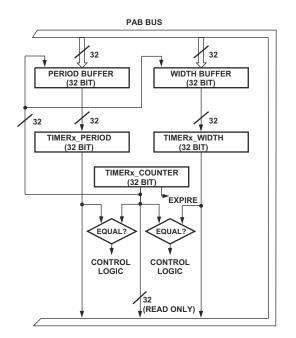

| GPIO Clear (GPIO_x_C), GPIO Set (GPIO_x_S), and<br>GPIO Toggle (GPIO_x_T) Registers | 4 |

| Performance/Throughput 15-1                                                         |   |

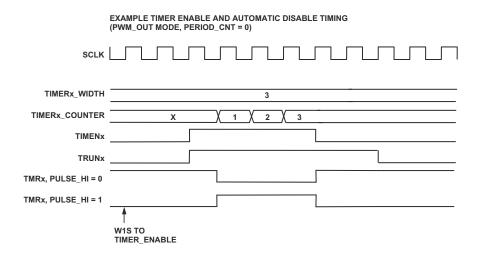

## TIMERS

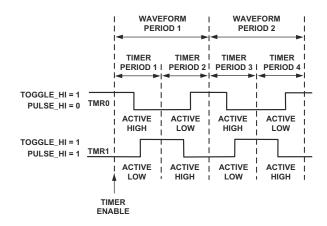

| General-purpose Timers                     | 16-1 |

|--------------------------------------------|------|

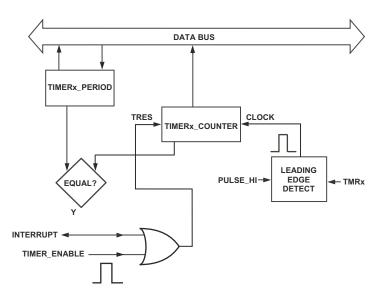

| Timer Registers                            | 16-4 |

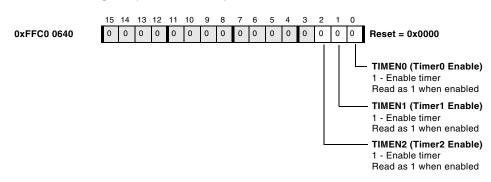

| TIMER_ENABLE Register                      | 16-4 |

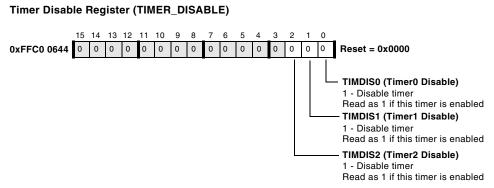

| TIMER_DISABLE Register                     | 16-5 |

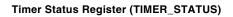

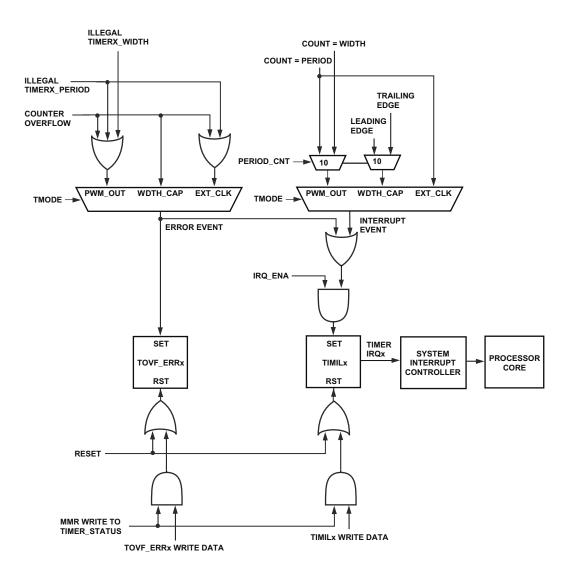

| TIMER_STATUS Register                      | 16-6 |

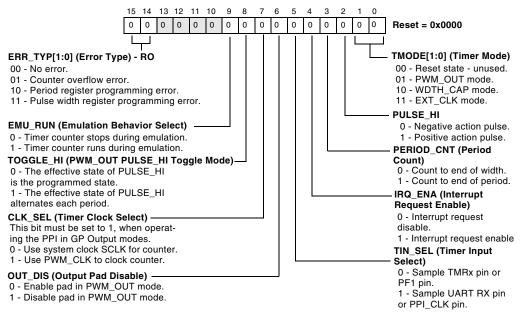

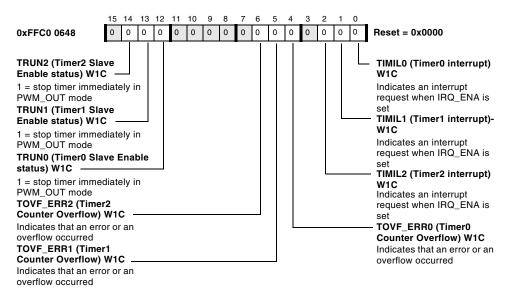

| TIMERx_CONFIG Registers                    | 16-8 |

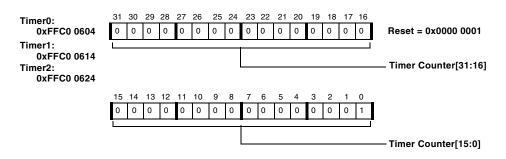

| TIMERx_COUNTER Registers                   | 16-9 |

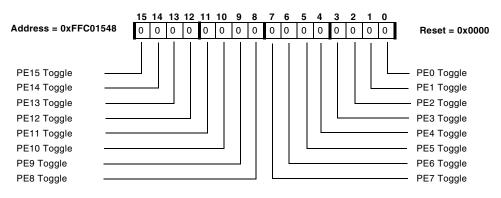

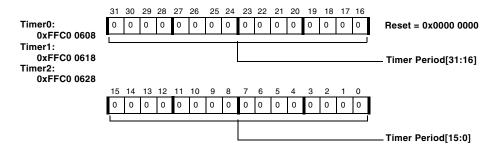

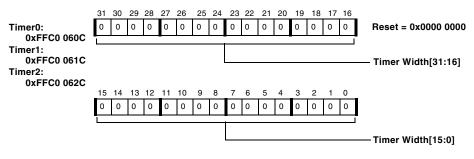

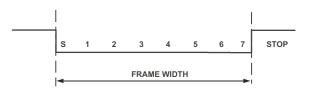

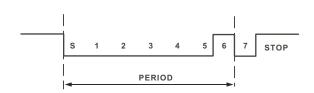

| TIMERx_PERIOD and TIMERx_WIDTH Registers 1 | 6-10 |

| Using the Timer                               | 16-14 |

|-----------------------------------------------|-------|

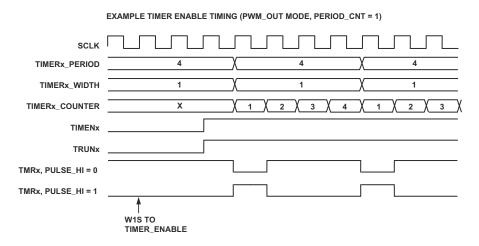

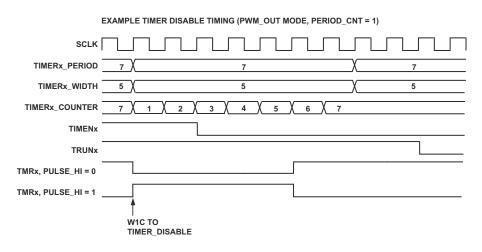

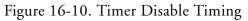

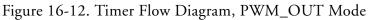

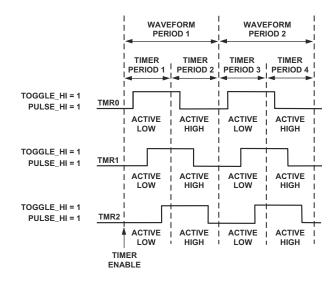

| Pulse Width Modulation (PWM_OUT) Mode         | 16-16 |

| Output Pad Disable                            | 16-18 |

| Single Pulse Generation                       | 16-18 |

| Pulse Width Modulation Waveform Generation    | 16-18 |

| Stopping the Timer in PWM_OUT Mode            | 16-20 |

| Externally Clocked PWM_OUT                    | 16-21 |

| PULSE_HI Toggle Mode                          | 16-22 |

| Pulse Width Count and Capture (WDTH_CAP) Mode | 16-26 |

| Autobaud Mode                                 | 16-36 |

| External Event (EXT_CLK) Mode                 | 16-38 |

| Using the Timers With the PPI                 | 16-39 |

| Interrupts                                    | 16-40 |

| Illegal States                                | 16-42 |

| Summary                                       | 16-45 |

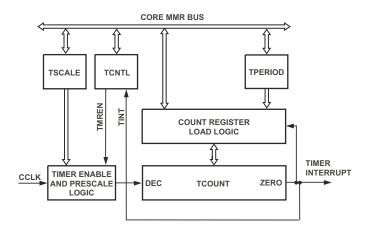

| Core Timer                                    | 16-47 |

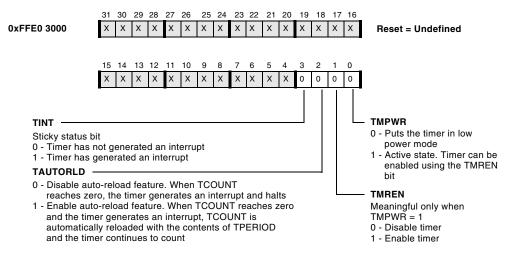

| TCNTL Register                                | 16-48 |

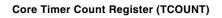

| TCOUNT Register                               | 16-50 |

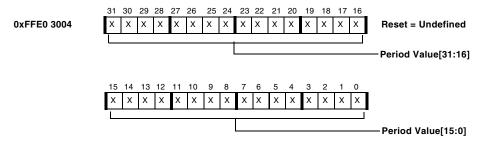

| TPERIOD Register                              | 16-50 |

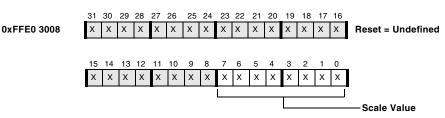

| TSCALE Register                               | 16-51 |

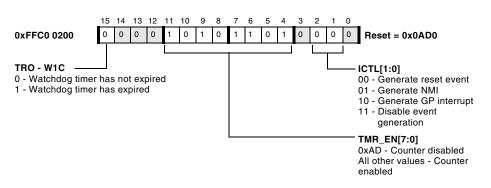

| Watchdog Timer                                | 16-52 |

| Watchdog Timer Operation                      | 16-52 |

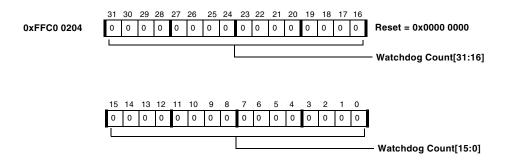

| WDOG_CNT Register                             | 16-52 |

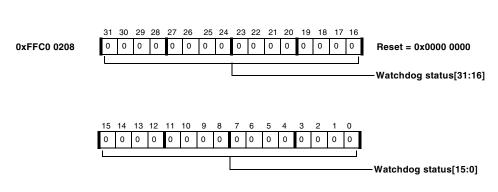

| WDOG_STAT Register     | 16-53  |

|------------------------|--------|

| WDOG_CTL Register      | 16-55  |

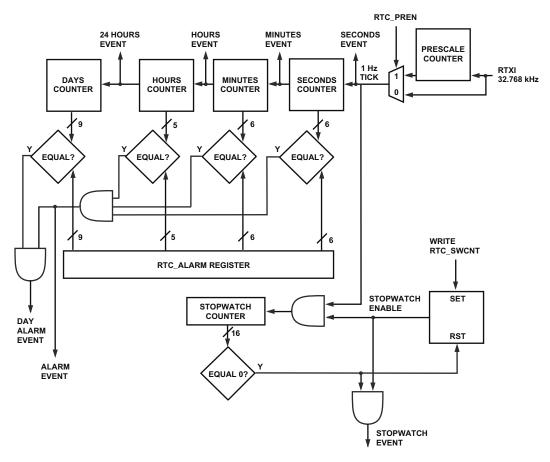

| REAL-TIME CLOCK        |        |

| Interfaces             | . 17-2 |

| RTC Clock Requirements | . 17-2 |

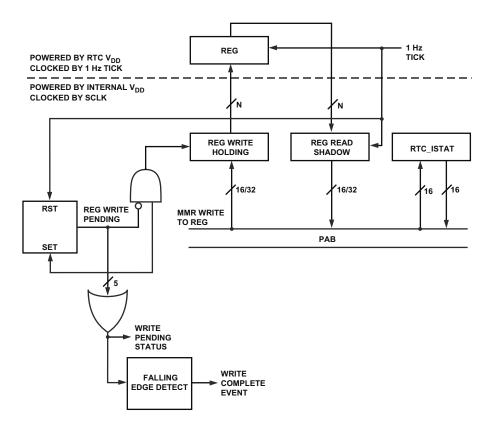

| RTC Programming Model  | . 17-4 |

| Register Writes        | . 17-5 |

| Write Latency          | . 17-6 |

| Register Reads         | . 17-7 |

| Deep Sleep             | . 17-7 |

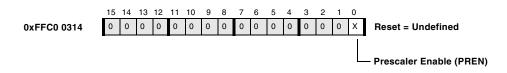

| Prescaler Enable       | . 17-8 |

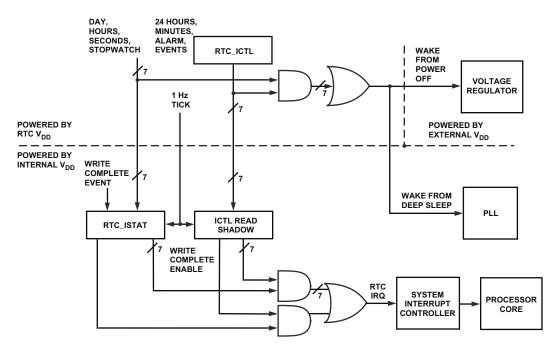

| Event Flags            | . 17-9 |

| Interrupts             | 17-11  |

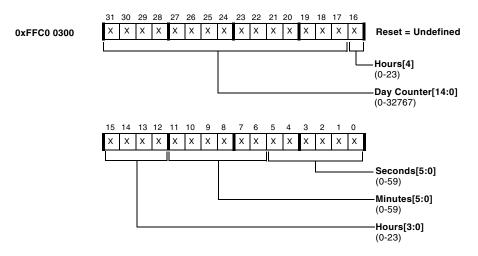

RTC\_STAT Register

17-13

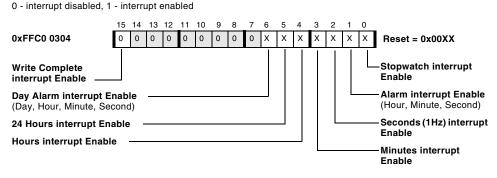

RTC\_ICTL Register

17-15

RTC\_ISTAT Register

17-16

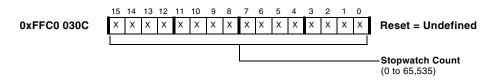

RTC\_SWCNT Register

17-17

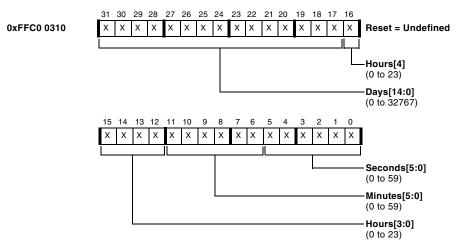

RTC\_ALARM Register17-18RTC\_PREN Register17-19State Transitions Summary17-21

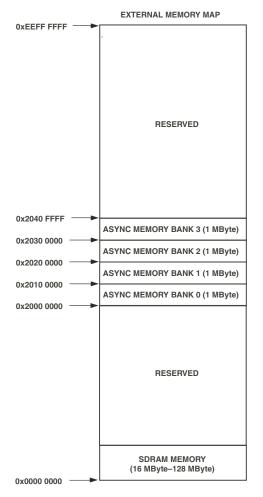

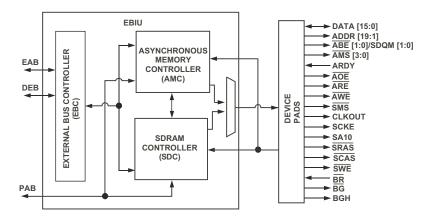

## EXTERNAL BUS INTERFACE UNIT

| Overview                                         |

|--------------------------------------------------|

| Block Diagram                                    |

| Internal Memory Interfaces 18-4                  |

| External Memory Interfaces                       |

| EBIU Programming Model 18-8                      |

| Error Detection                                  |

| Asynchronous Memory Interface                    |

| Asynchronous Memory Address Decode 18-9          |

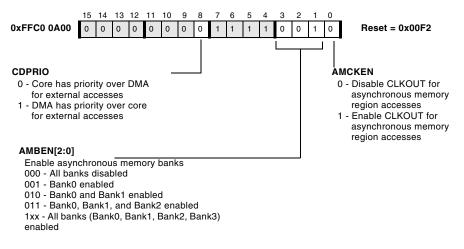

| EBIU_AMGCTL Register 18-11                       |

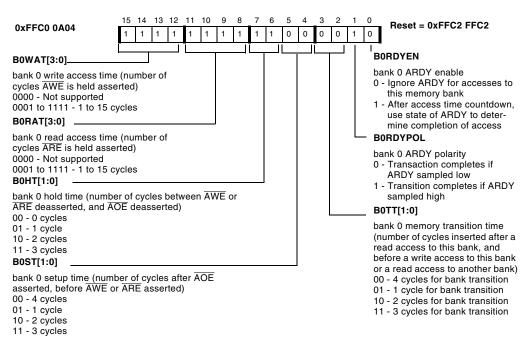

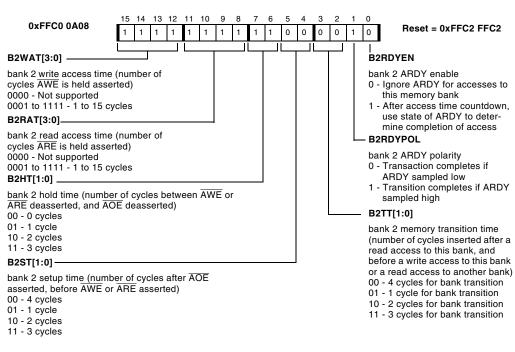

| EBIU_AMBCTL0 and EBIU_AMBCTL1 Registers 18-13    |

| Avoiding Bus Contention                          |

| ARDY Input Control 18-19                         |

| Programmable Timing Characteristics              |

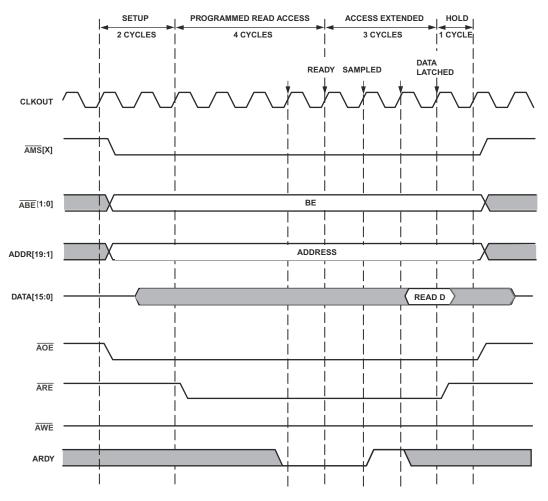

| Asynchronous Accesses by Core Instructions 18-20 |

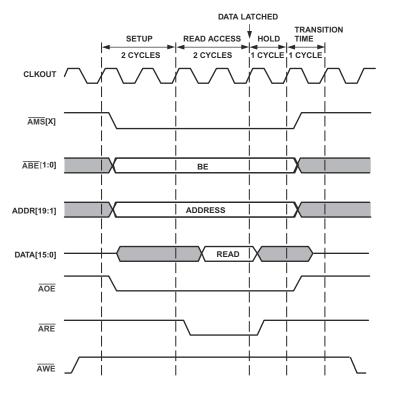

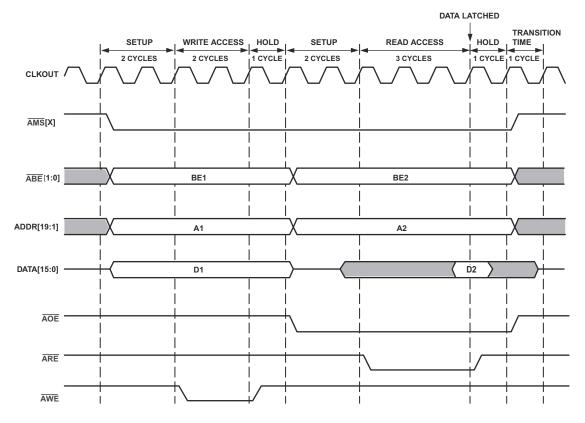

| Asynchronous Reads 18-20                         |

| Asynchronous Writes 18-22                        |

| Adding Additional Wait States 18-23              |

| Byte Enables 18-25                               |

| On-Chip Flash Memory 18-25                       |

| SDRAM Controller (SDC) 18-25                     |

| Definition of Terms 18-26                        |

| Bank Activate command 18-27                      |

| Burst Length 18-27                               |

| Bu   | irst Stop Command                           | 18-27 |

|------|---------------------------------------------|-------|

| Bu   | ırst Type                                   | 18-27 |

| CA   | AS Latency (CL)                             | 18-28 |

| CI   | 3R (CAS before RAS) Refresh or Auto-Refresh | 18-28 |

| D    | QM Pin Mask Function                        | 18-29 |

| In   | ternal Bank                                 | 18-29 |

| M    | ode Register                                | 18-29 |

| Pa   | ge Size                                     | 18-30 |

| Pro  | echarge Command                             | 18-30 |

| SE   | DRAM Bank                                   | 18-30 |

| Se   | lf-Refresh                                  | 18-31 |

| tR   | AS                                          | 18-31 |

| tR   | С                                           | 18-31 |

| tR   | CD                                          | 18-31 |

| tR   | FC                                          | 18-32 |

| tR   | Р                                           | 18-32 |

| tR   | RD                                          | 18-32 |

| tW   | /R                                          | 18-32 |

| tΧ   | SR                                          | 18-33 |

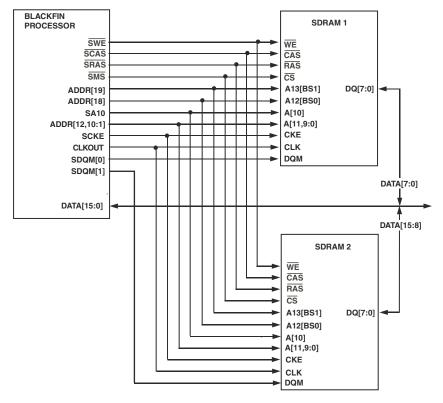

| SDRA | AM Configurations Supported                 | 18-33 |

| Exam | ple SDRAM System Block Diagrams             | 18-34 |

| Ex   | ecuting a Parallel Refresh Command          | 18-36 |

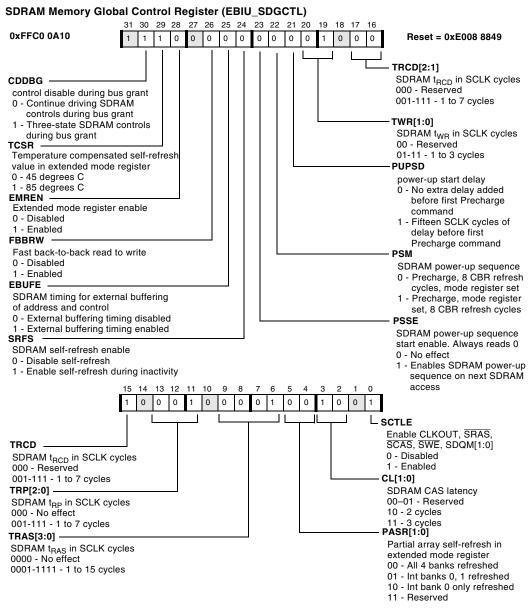

| EBIU_SDGCTL Register 18                              | -36 |

|------------------------------------------------------|-----|

| Setting the SDRAM Clock Enable (SCTLE) 18            | -40 |

| Entering and Exiting Self-Refresh Mode (SRFS) 18     | -41 |

| Setting the SDRAM Buffering Timing Option<br>(EBUFE) | -42 |

| Selecting the CAS Latency Value (CL)                 |     |

| Selecting the Bank Activate Command Delay (TRAS) 18  |     |

| Selecting the RAS to CAS Delay (TRCD) 18             |     |

| Selecting the Precharge Delay (TRP) 18               |     |

| Selecting the Write to Precharge Delay (TWR) 18      |     |

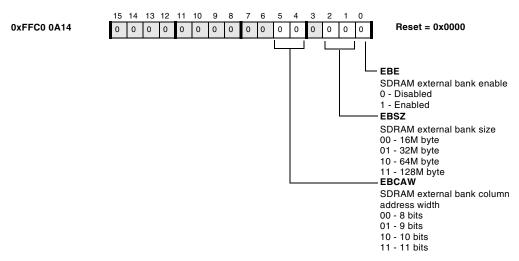

| EBIU_SDBCTL Register                                 |     |

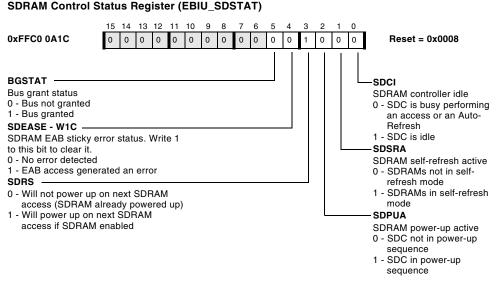

| EBIU_SDSTAT Register                                 | -51 |

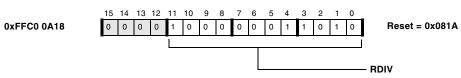

| EBIU_SDRRC Register 18                               | -52 |

| SDRAM External Memory Size                           | -54 |

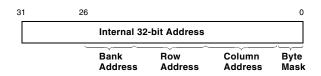

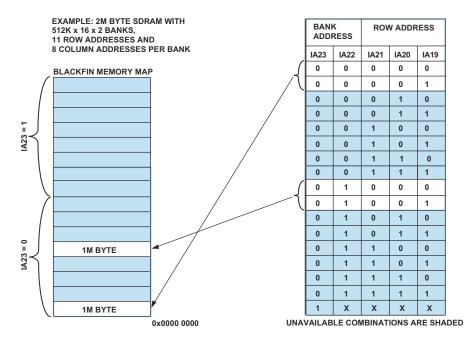

| SDRAM Address Mapping 18                             | -54 |

| 16-Bit Wide SDRAM Address Muxing 18                  | -55 |

| Data Mask (SDQM[1:0]) Encodings 18                   | -56 |

| SDC Operation                                        | -57 |

| SDC Configuration                                    | -57 |

| SDC Commands 18                                      | -59 |

| Precharge Commands 18                                | -60 |

| Bank Activate Command 18                             | -61 |

| Load Mode Register Command 18                        | -61 |

| Read/Write Command 18                                | -62 |

| Auto-Refresh Command 18                              | -63 |

| Self-Refresh Command                  | 18-63 |

|---------------------------------------|-------|

| No Operation/Command Inhibit Commands | 18-64 |

| SDRAM Timing Specifications           | 18-64 |

| SDRAM Performance                     | 18-65 |

| Bus Request and Grant                 | 18-66 |

| Operation                             | 18-66 |

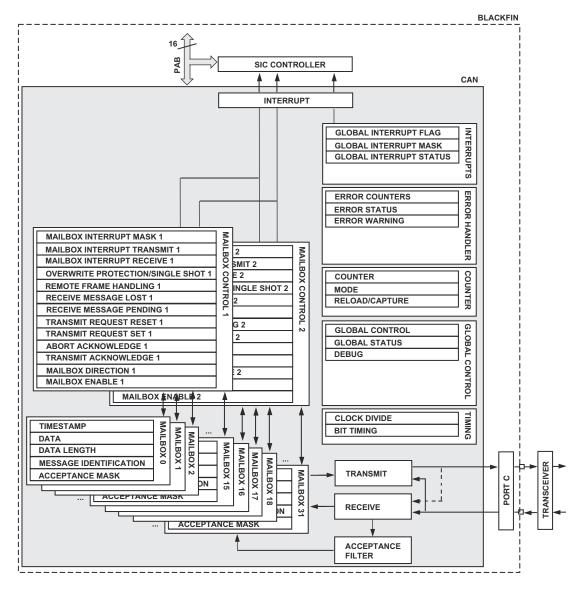

## CAN MODULE

| Overview                              |

|---------------------------------------|

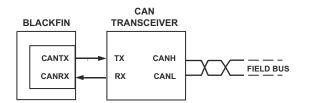

| Interface Overview 19-2               |

| CAN Mailbox Area 19-4                 |

| CAN Mailbox Control 19-6              |

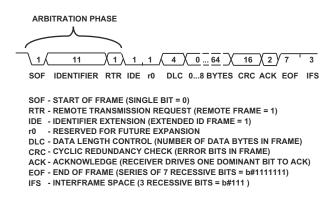

| CAN Protocol Basics 19-7              |

| CAN Operation 19-9                    |

| Bit Timing 19-9                       |

| Transmit Operation                    |

| Retransmission                        |

| Single Shot Transmission 19-14        |

| Auto-Transmission 19-15               |

| Receive Operation 19-15               |

| Data Acceptance Filter 19-19          |

| Remote Frame Handling 19-20           |

| Watchdog Mode 19-21                   |

| Time Stamps 19-21                     |

| Temporarily Disabling Mailboxes 19-23 |

| Functional Operation                       | . 19-24 |

|--------------------------------------------|---------|

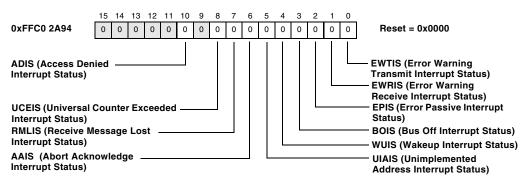

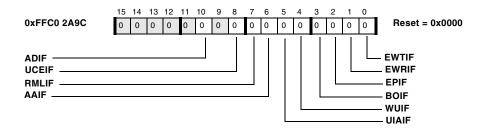

| CAN Interrupts                             | . 19-24 |

| Mailbox Interrupts                         | . 19-24 |

| Global CAN Interrupt                       | . 19-25 |

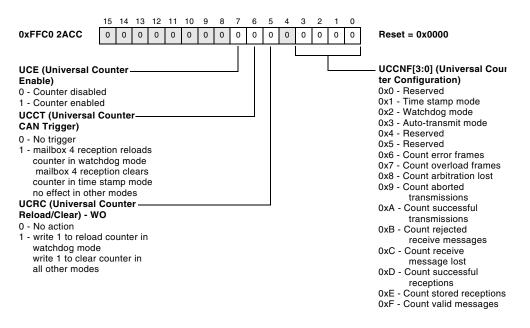

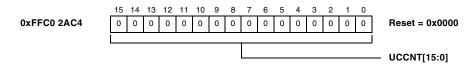

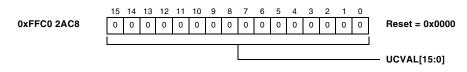

| Event Counter                              | . 19-29 |

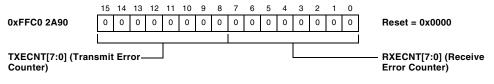

| CAN Warnings and Errors                    | . 19-30 |

| Programmable Warning Limits                | . 19-30 |

| CAN Error Handling                         | . 19-31 |

| Error Frames                               | . 19-32 |

| Error Levels                               | . 19-34 |

| Debug and Test Modes                       | . 19-36 |

| Low Power Features                         | . 19-39 |

| CAN Built-In Suspend Mode                  | . 19-40 |

| CAN Built-In Sleep Mode                    | . 19-40 |

| CAN Wakeup From Hibernate State            | . 19-41 |

| Register Definitions                       | . 19-42 |

| Global CAN Registers                       | . 19-45 |

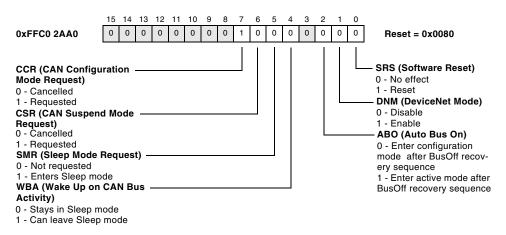

| CAN_CONTROL Master Control Register        | . 19-45 |

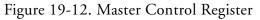

| CAN_STATUS Global CAN Status Register      | . 19-46 |

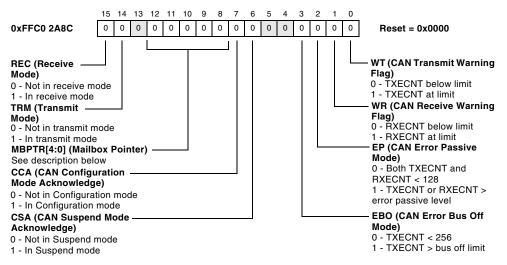

| CAN_DEBUG Register                         | . 19-47 |

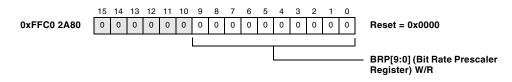

| CAN_CLOCK Register                         | . 19-47 |

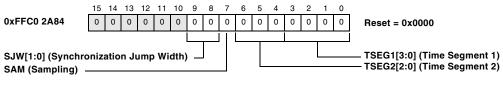

| CAN_TIMING Register                        | . 19-48 |

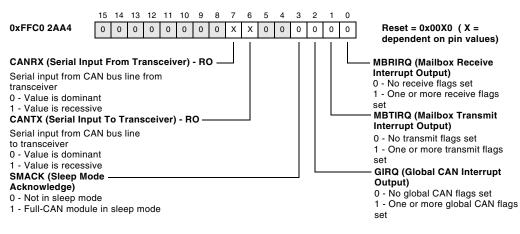

| CAN_INTR Interrupt Pending Register        | . 19-48 |

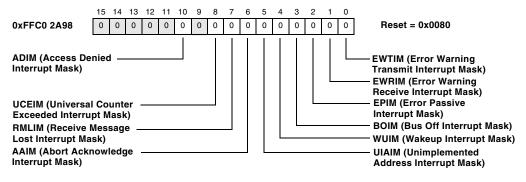

| CAN_GIM Global CAN Interrupt Mask Register | . 19-49 |

| CAN_GIS Global CAN Interrupt Status Register | 19-49 |

|----------------------------------------------|-------|

| CAN_GIF Global CAN Interrupt Flag Register   | 19-50 |

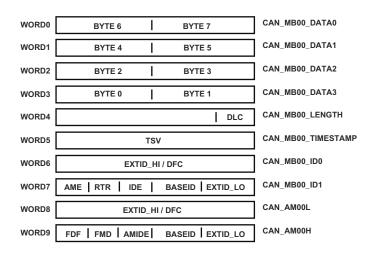

| Mailbox/Mask Registers                       | 19-50 |

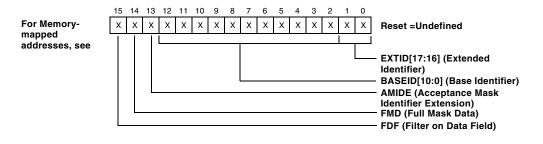

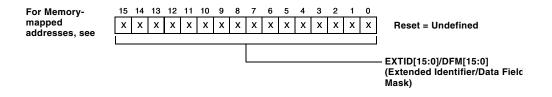

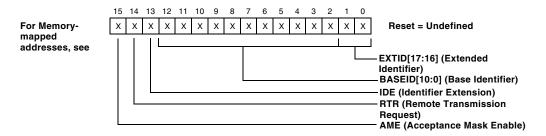

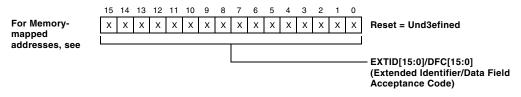

| CAN_AMxx Mailbox Acceptance Registers        | 19-50 |

| CAN_MBxx_ID1 Registers                       | 19-55 |

| CAN_MBxx_ID0 Registers                       | 19-57 |

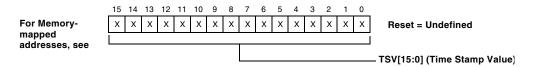

| CAN_MBxx_TIMESTAMP Registers                 | 19-59 |

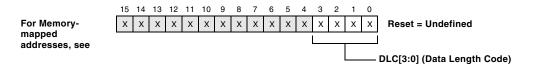

| CAN_MBxx_LENGTH Registers                    | 19-61 |

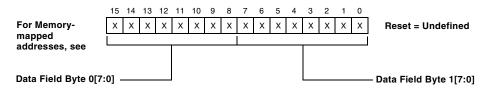

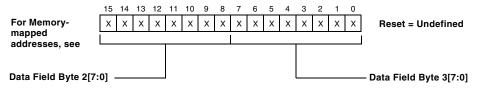

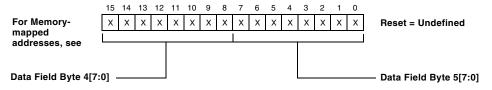

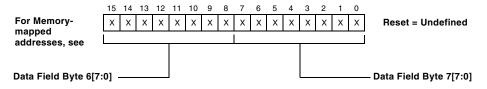

| CAN_MBxx_DATAx Registers                     | 19-63 |

| Mailbox Control Registers                    | 19-70 |

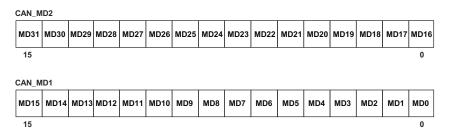

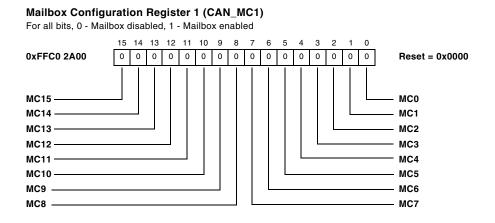

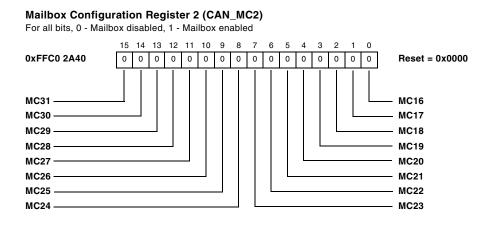

| CAN_MCx Mailbox Configuration Registers      | 19-71 |

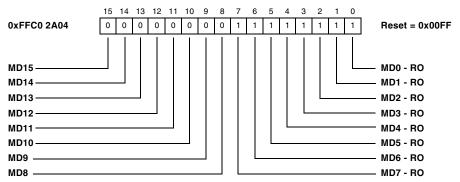

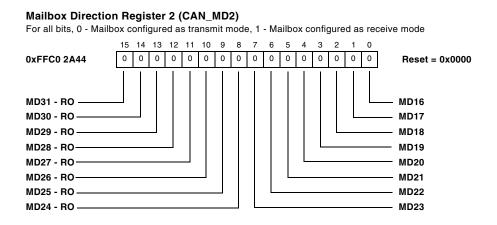

| CAN_MDx Mailbox Direction Registers          | 19-72 |

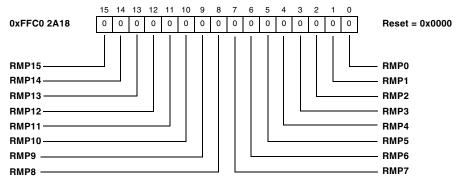

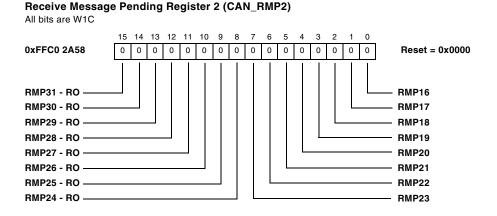

| CAN_RMPx Registers                           | 19-73 |

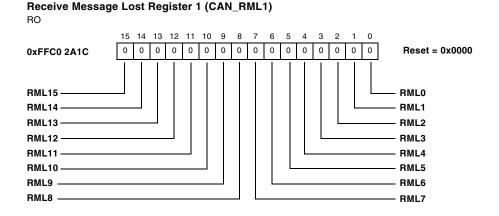

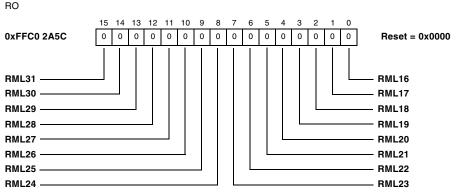

| CAN_RMLx Registers                           | 19-74 |

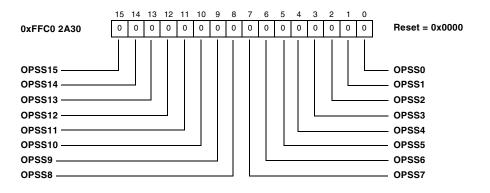

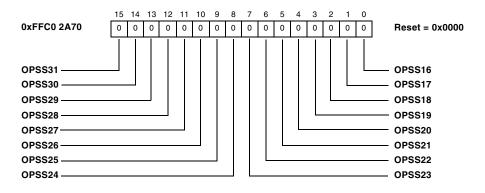

| CAN_OPSSx Register                           | 19-75 |

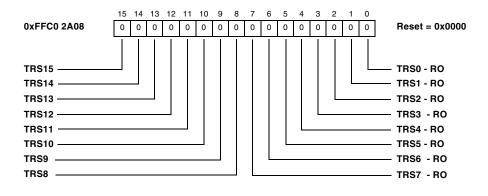

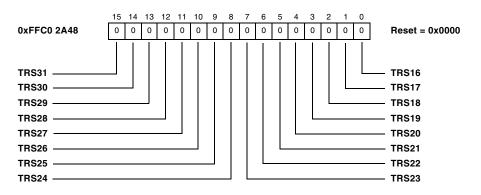

| CAN_TRSx Registers                           | 19-76 |

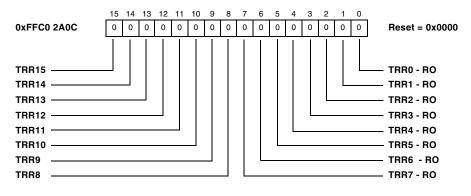

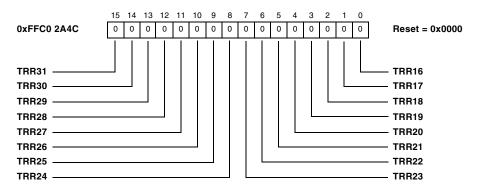

| CAN_TRRx Registers                           | 19-77 |

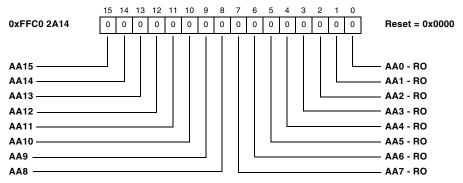

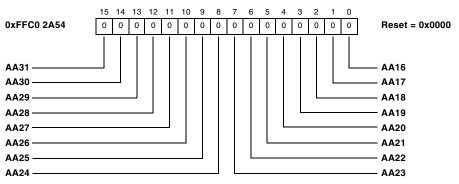

| CAN_AAx Registers                            | 19-78 |

| CAN_TAx Registers                            | 19-79 |

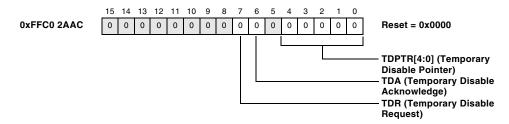

| CAN_MBTD Register                            | 19-80 |

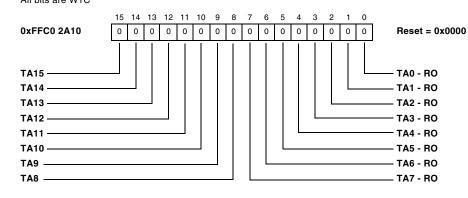

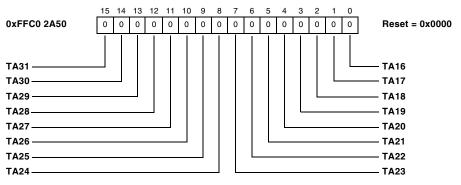

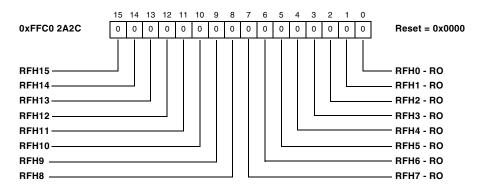

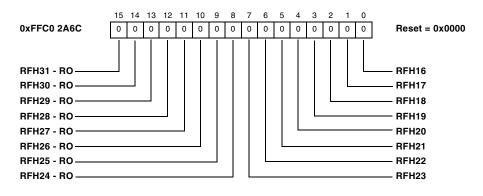

| CAN_RFHx Registers                           | 19-80 |

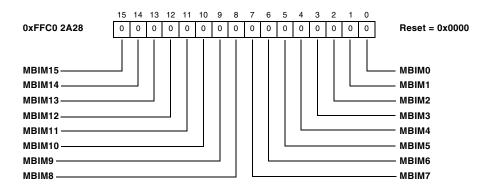

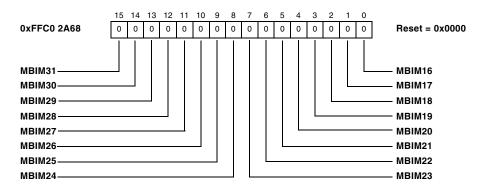

| CAN_MBIMx Registers                          | 19-82 |

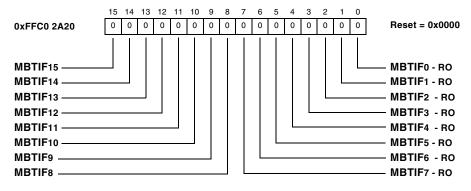

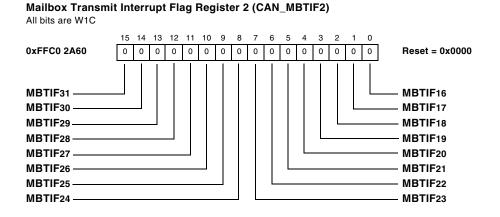

| CAN_MBTIFx Registers                         | 19-83 |

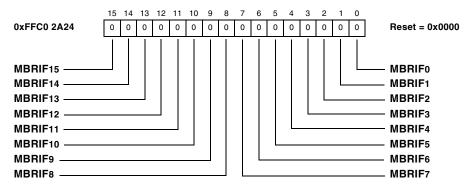

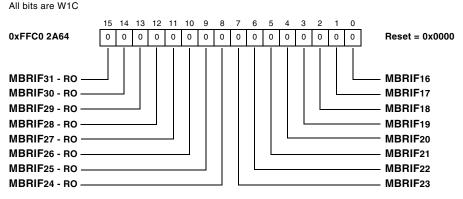

| CAN_MBRIFx Registers                         | 19-84 |

| 19-85 |

|-------|

| 19-85 |

| 19-86 |

| 19-86 |

| 19-86 |

| 19-87 |

| 19-87 |

| 19-87 |

| 19-88 |

| 19-88 |

| 19-90 |

| 19-92 |

|       |

## **TWO-WIRE INTERFACE CONTROLLERS**

| Overview                                              | 0-1 |

|-------------------------------------------------------|-----|

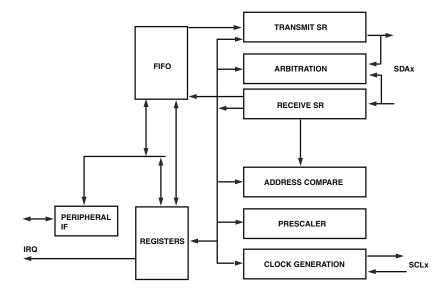

| Architecture                                          | 0-3 |

| Register Descriptions                                 | 0-5 |

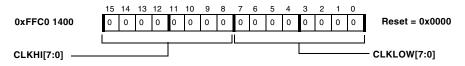

| TWI Control (TWIx_CONTROL) Registers 2                | 0-5 |

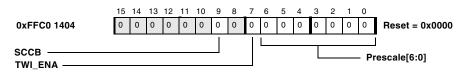

| TWI Clock Divider (TWIx_CLKDIV) Registers 24          | 0-6 |

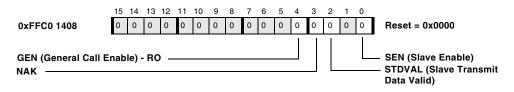

| TWI Slave Mode Control (TWIx_SLAVE_CTRL)<br>Registers | 0-7 |

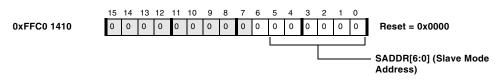

| TWI Slave Mode Address (TWIx_SLAVE_ADDR)<br>Registers | 0-9 |

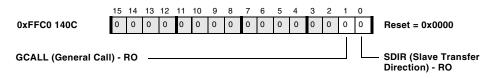

| TWI Slave Mode Status (TWIx_SLAVE_STAT)<br>Registers  | -10 |

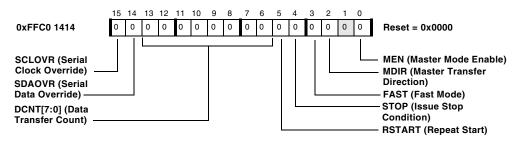

|                         | TWI Master Mode Control (TWIx_MASTER_CTRL)<br>Registers           | 20-11 |

|-------------------------|-------------------------------------------------------------------|-------|

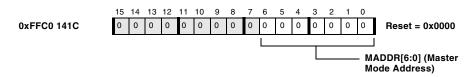

|                         | TWI Master Mode Address (TWIx_MASTER_ADDR)<br>Registers           | 20-14 |

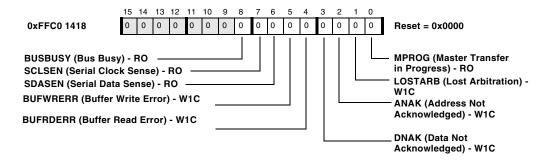

|                         | TWI Master Mode Status (TWIx_MASTER_STAT)<br>Registers            | 20-15 |

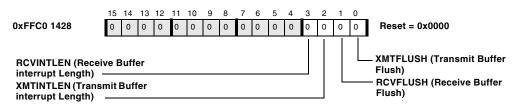

|                         | TWI FIFO Control (TWIx_FIFO_CTRL) Registers                       | 20-19 |

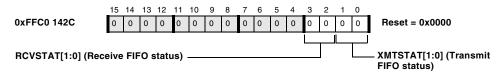

|                         | TWI FIFO Status (TWIx_FIFO_STAT) Registers                        | 20-21 |

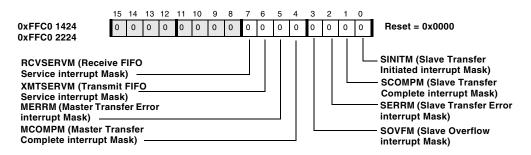

|                         | TWI Interrupt Mask (TWIx_INT_ENABLE) Registers                    | 20-22 |

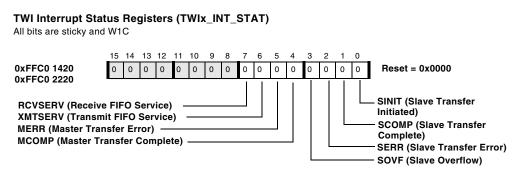

|                         | TWI Interrupt Status (TWIx_INT_STAT) Registers                    | 20-25 |

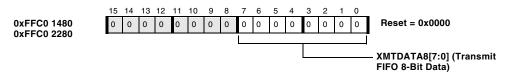

|                         | TWI FIFO Transmit Data Single Byte<br>(TWIx_XMT_DATA8) Registers  | 20-28 |

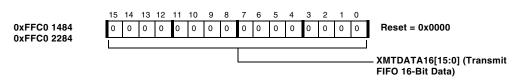

|                         | TWI FIFO Transmit Data Double Byte<br>(TWIx_XMT_DATA16) Registers | 20-29 |

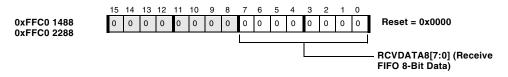

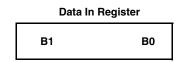

|                         | TWI FIFO Receive Data Single Byte<br>(TWIx_RCV_DATA8) Registers   | 20-30 |

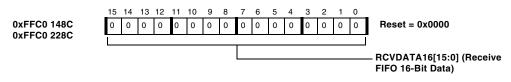

|                         | TWI FIFO Receive Data Double Byte<br>(TWIx_RCV_DATA16) Registers  | 20-31 |

| Data Transfer Mechanics |                                                                   | 20-32 |

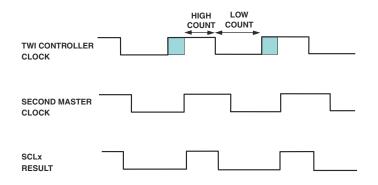

|                         | Clock Generation and Synchronization                              | 20-32 |

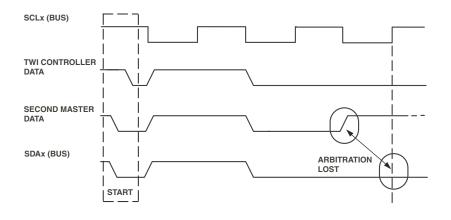

|                         | Bus Arbitration                                                   | 20-33 |

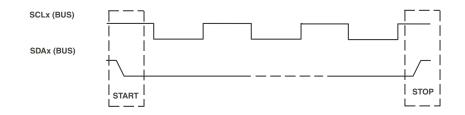

|                         | Start and Stop Conditions                                         | 20-34 |

|                         | General Call Support                                              |       |

|                         | Fast Mode                                                         |       |

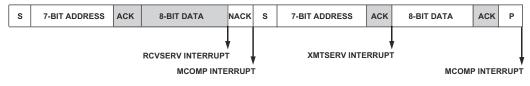

| Programming Examples 20-37                             |

|--------------------------------------------------------|

| General Setup 20-37                                    |

| Slave Mode 20-38                                       |

| Master Mode Clock Setup 20-39                          |

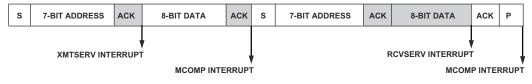

| Master Mode Transmit 20-39                             |

| Master Mode Receive 20-40                              |

| Repeated Start Condition 20-41                         |

| Transmit/Receive Repeated Start Sequence 20-42         |

| Receive/Transmit Repeated Start Sequence 20-43         |

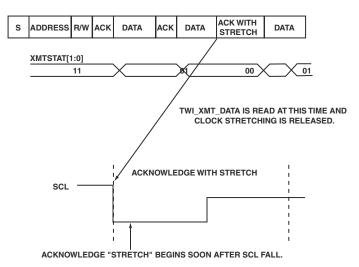

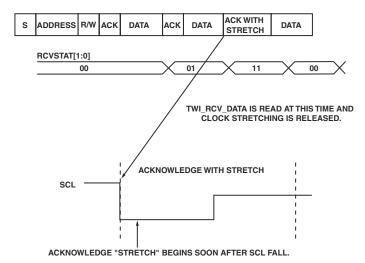

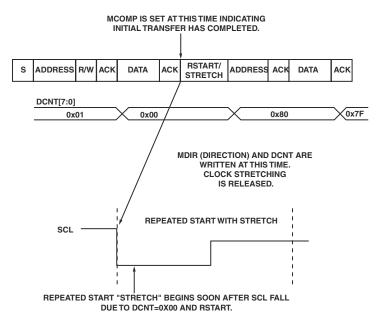

| Clock Stretching 20-44                                 |

| Clock Stretching During FIFO Underflow 20-45           |

| Clock Stretching During FIFO Overflow 20-46            |

| Clock Stretching During Repeated Start Condition 20-48 |

| Electrical Specifications 20-49                        |

## MEDIA TRANSCEIVER MODULE (MXVR)

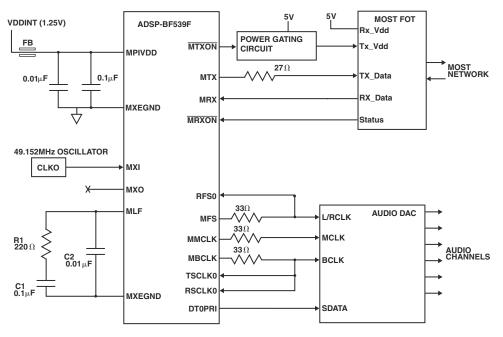

| Interface Signals 21-2                               |

|------------------------------------------------------|

| MXVR Memory Map 21-4                                 |

| Register Descriptions 21-5                           |

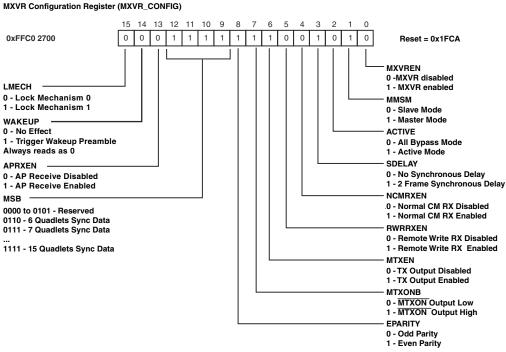

| MXVR Configuration Register (MXVR_CONFIG) 21-5       |

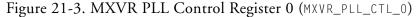

| MXVR PLL Control Register 0 (MXVR_PLL_CTL_0) 21-11   |

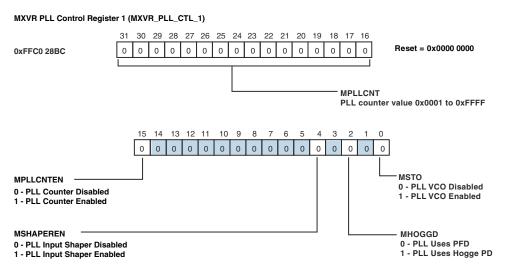

| MXVR PLL Control Register 1 (MXVR_PLL_CTL_1) 21-18   |

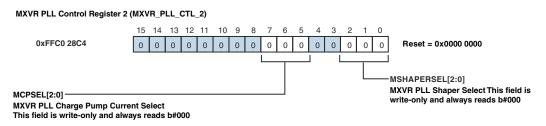

| MXVR PLL Control Register 2 (MXVR_PLL_CTL_2) 21-20   |

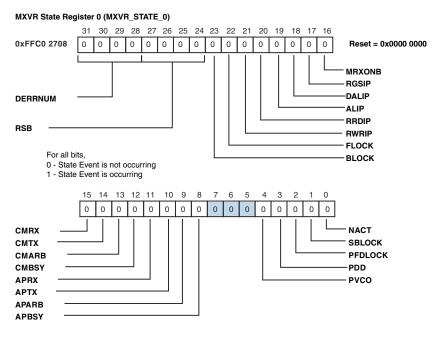

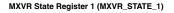

| MXVR State Registers (MXVR_STATE_0,<br>MXVR_STATE_1) |

|                                                      |

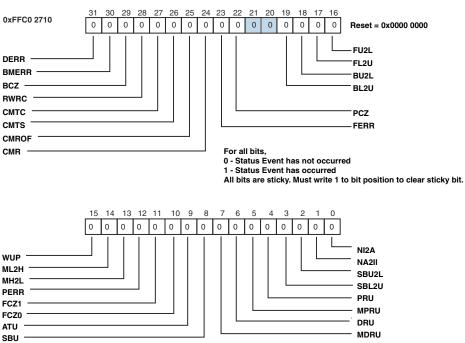

| MXVR Interrupt Status Register 0<br>(MXVR_INT_STAT_0)                                               | 21-31 |

|-----------------------------------------------------------------------------------------------------|-------|

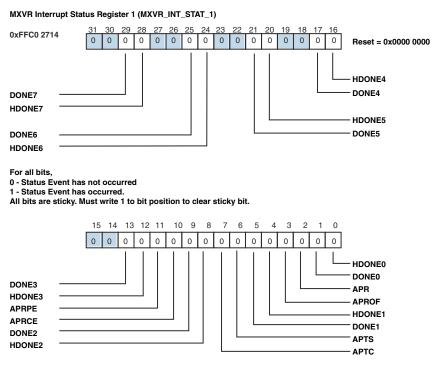

| MXVR Interrupt Status Register_1<br>(MXVR_INT_STAT_1)                                               | 21-42 |

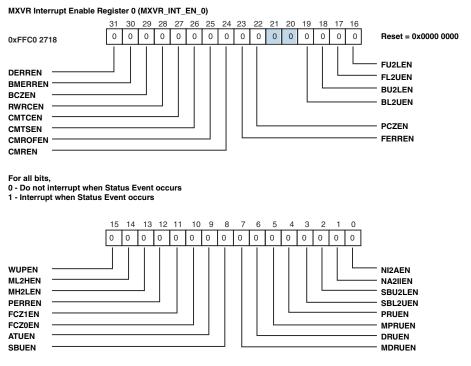

| MXVR Interrupt Enable Register 0<br>(MXVR_INT_EN_0)                                                 | 21-46 |

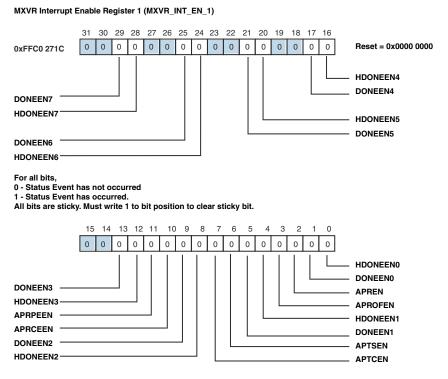

| MXVR Interrupt Enable Register 1 (MXVR_INT_EN_1)                                                    | 21-48 |

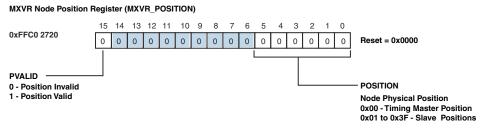

| MXVR Node Position Register (MXVR_POSITION)                                                         | 21-50 |

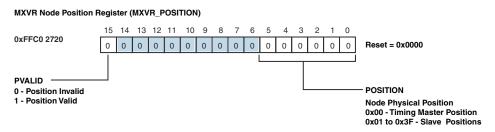

| MXVR Maximum Node Position Register<br>(MXVR_MAX_POSITION)                                          | 21-51 |

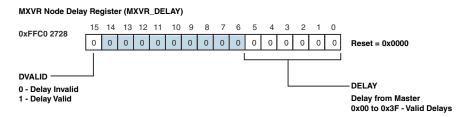

| MXVR Node Frame Delay Register (MXVR_DELAY)                                                         | 21-53 |

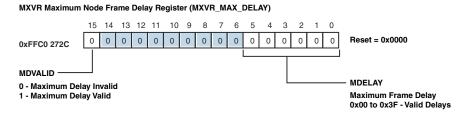

| MXVR Maximum Node Frame Delay Register<br>(MXVR_MAX_DELAY)                                          | 21-55 |

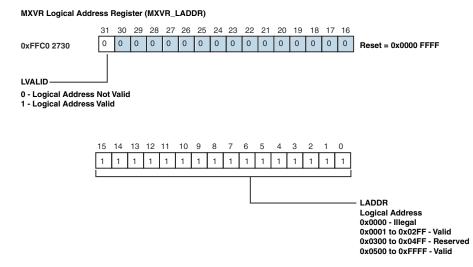

| MXVR Logical Address Register (MXVR_LADDR)                                                          | 21-57 |

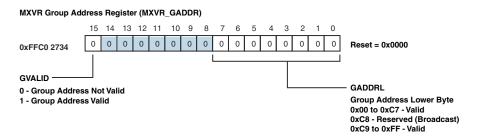

| MXVR Group Address Register (MXVR_GADDR)                                                            | 21-59 |

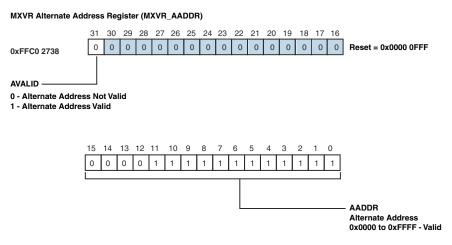

| MXVR Alternate Address Register (MXVR_AADDR)                                                        | 21-59 |

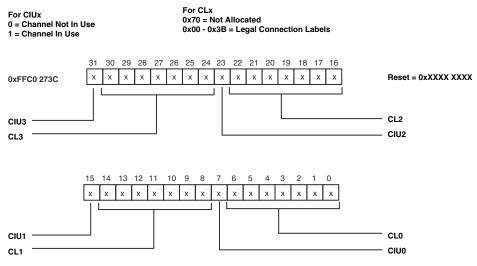

| MXVR Allocation Table Registers (MXVR_ALLOC_0 –<br>MXVR_ALLOC_14)                                   | 21-60 |

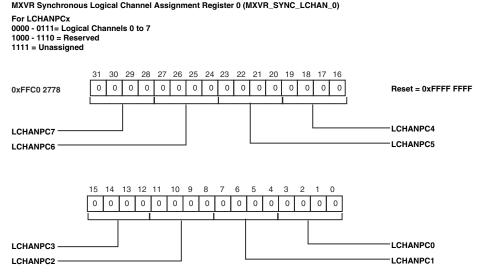

| MXVR Synchronous Logical Channel Assignment Registers<br>(MXVR_SYNC_LCHAN_0 –<br>MXVR_SYNC_LCHAN_7) | 21-62 |

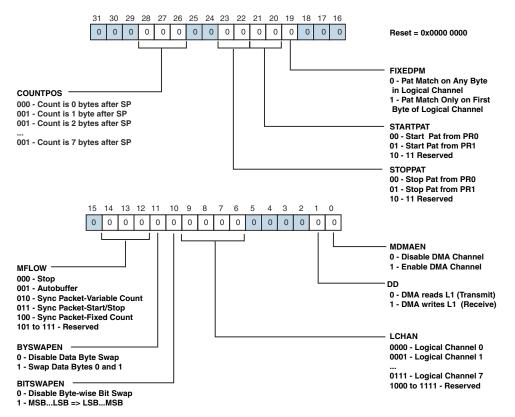

| MXVR DMA Channel x Configuration Registers<br>(MXVR_DMA0_CONFIG –<br>MXVR_DMA7_CONFIG)              | 21-64 |

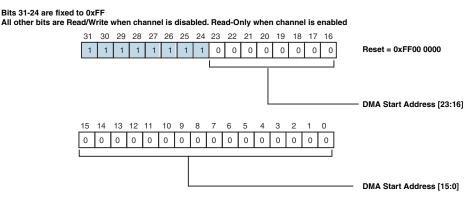

| MXVR DMA Channel x Start Address Registers<br>(MXVR_DMA0_START_ADDR –<br>MXVR_DMA7_START_ADDR)      | 21-73 |

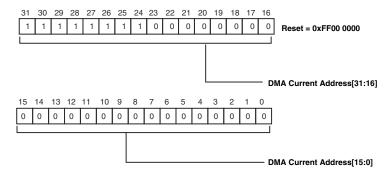

| MXVR DMA Channel x Current Address Registers<br>(MXVR_DMA0_CURR_ADDR –<br>MXVR_DMA7_CURR_ADDR)                |

|---------------------------------------------------------------------------------------------------------------|

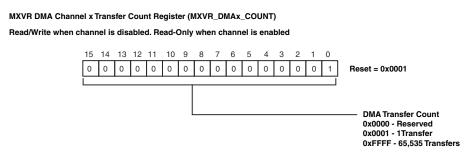

| MXVR DMA Channel x Transfer Count Registers<br>(MXVR_DMA0_COUNT – MXVR_DMA7_COUNT) 21-75                      |

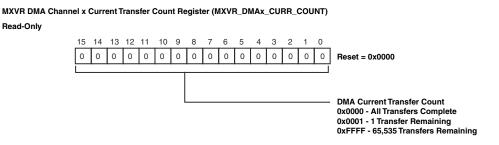

| MXVR DMA Channel x Current Transfer Count Registers<br>(MXVR_DMA0_CURR_COUNT –<br>MXVR_DMA7_CURR_COUNT) 21-78 |

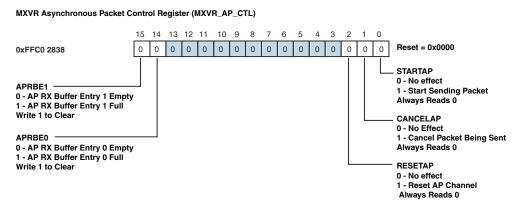

| MXVR Asynchronous Packet Control Register<br>(MXVR_AP_CTL)                                                    |

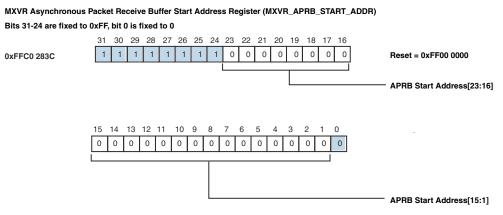

| MXVR Asynchronous Packet Receive Buffer Start Address<br>Register (MXVR_APRB_START_ADDR) 21-83                |

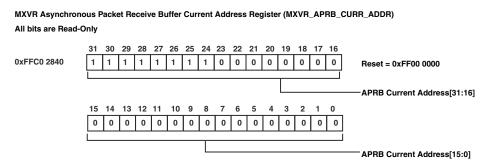

| MXVR Asynchronous Packet Receive Buffer Current Address<br>Register (MXVR_APRB_CURR_ADDR) 21-84               |

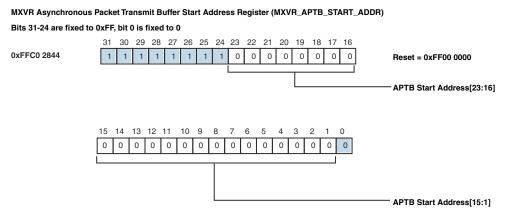

| MXVR Asynchronous Packet Transmit Buffer Start Address<br>Register (MXVR_APTB_START_ADDR) 21-85               |

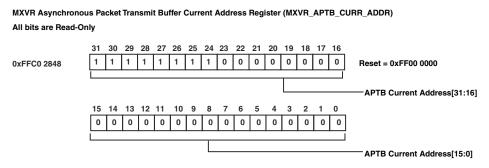

| MXVR Asynchronous Packet Transmit Buffer Current Address<br>Register (MXVR_APTB_CURR_ADDR) 21-86              |

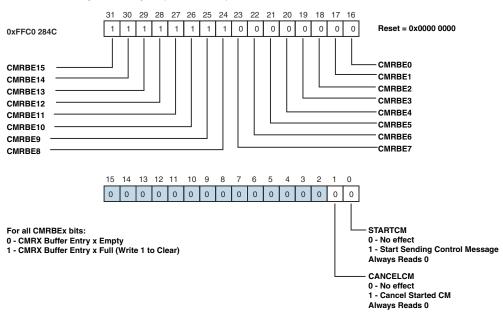

| MXVR Control Message Control Register<br>(MXVR_CM_CTL)                                                        |

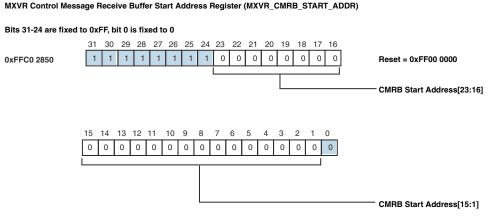

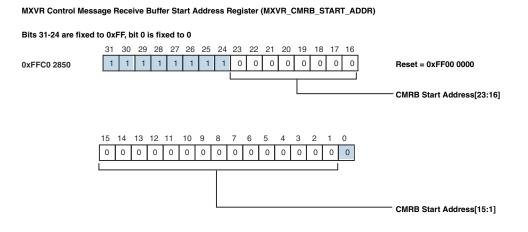

| MXVR Control Message Receive Buffer Start Address<br>Register (MXVR_CMRB_START_ADDR) 21-89                    |

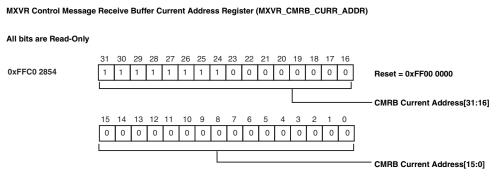

| MXVR Control Message Receive Buffer Current Address<br>Register (MXVR_CMRB_CURR_ADDR) 21-90                   |

| MXVR Control Message Transmit Buffer Start Address<br>Register (MXVR_CMTB_START_ADDR) 21-91                   |

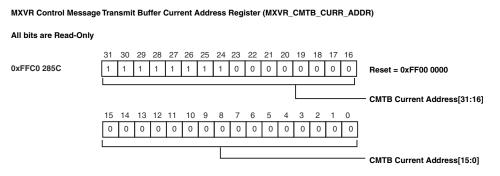

| MXVR Control Message Transmit Buffer Current Address<br>Register (MXVR_CMTB_CURR_ADDR) 21-92                  |

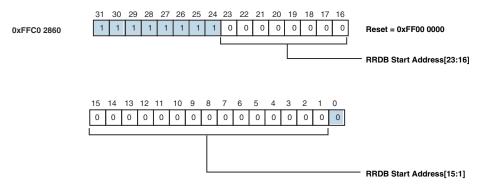

| MXVR Remote Read Buffer Start Address Register<br>(MXVR_RRDB_START_ADDR) 21  | -93 |

|------------------------------------------------------------------------------|-----|

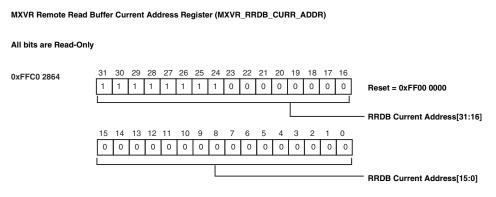

| MXVR Remote Read Buffer Current Address Register<br>(MXVR_RRDB_CURR_ADDR) 21 | -94 |

| MXVR Pattern Registers 21                                                    | -94 |

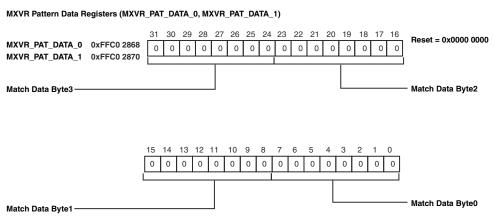

| MXVR Pattern Data Registers (MXVR_PAT_DATA_0,<br>MXVR_PAT_DATA_1) 21         | -95 |

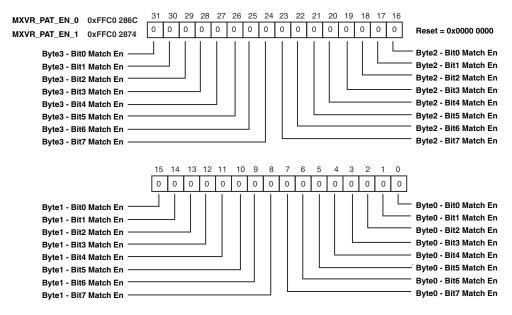

| MXVR Pattern Enable Registers (MXVR_PAT_EN_0,<br>MXVR_PAT_EN_1) 21           | -96 |

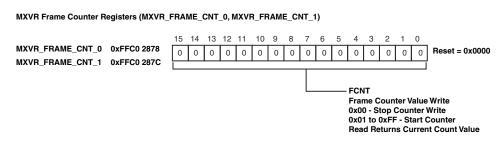

| MXVR Frame Counter Registers (MXVR_FRAME_CNT_0,<br>MXVR_FRAME_CNT_1) 21      | -97 |

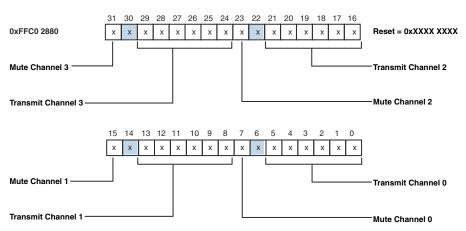

| MXVR Routing Registers (MXVR_ROUTING_0 –<br>MXVR_ROUTING_14) 21              | -98 |

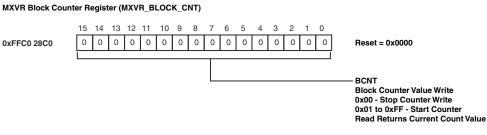

| MXVR Block Counter Register (MXVR_BLOCK_CNT) 21-                             | 101 |

| General Operation 21-                                                        | 102 |

| Network Services Software 21-                                                | 103 |

| Network Activity Detection 21-                                               | 103 |

| Node Initialization 21-                                                      | 105 |

| Master Mode Initialization of the MXVR_CONFIG<br>Register                    | 105 |

| Slave Mode Initialization of the MXVR_CONFIG<br>Register                     | 106 |

| Initialization of the MXVR_PLL_CTL_0 Register 21-                            | 106 |

| Initialization of the MXVR_PLL_CTL_1 Register 21-                            | 106 |

| Initialization of the MXVR_ROUTING_x Registers 21-                           | 107 |

| Initialization of the Buffer Start Address Registers 21-                     | 107 |

| PLL Start-Up Sequence 21-                                                    | 108 |

| Network Lock                                            | 09 |

|---------------------------------------------------------|----|

| For a Master node: 21-1                                 | 10 |

| For a Slave node: 21-1                                  | 11 |

| Network Initialization 21-1                             | 11 |

| Synchronous Data Routing, Muting, and Transmission 21-1 | 13 |

| Asynchronous Packet Transmission 21-1                   | 16 |

| Asynchronous Packet Reception 21-1                      | 19 |

| Control Message Transmission 21-12                      | 21 |

| Normal Control Message Transmission 21-12               | 25 |

| Remote Read Control Message Transmission 21-12          | 27 |

| Remote Write Control Message Transmission 21-12         | 29 |

| Resource Allocate Control Message Transmission 21-12    | 31 |

| Resource De-Allocate Control Message Transmission 21-12 | 34 |

| Remote GetSource Control Message Transmission 21-12     | 37 |

| Control Message Reception 21-14                         | 40 |

| Normal Control Message Reception 21-14                  | 40 |

| Remote Read and Remote Write Reception 21-14            | 42 |

| Resource Allocate Reception 21-14                       | 44 |

| Resource De-Allocate Reception 21-14                    | 44 |

| Remote GetSource Reception                              | 45 |

| MXVR Low Power Operation 21-14                          | 46 |

| Full On Mode 21-14                                      | 47 |

| Active Mode 21-14                                       | 49 |

| Sleep Mode 21-1                                         | 50 |

|                                                         |    |

| Deep Sleep Mode                       | 21-152 |

|---------------------------------------|--------|

| Hibernate State                       | 21-153 |

| Power Gating the ADSP-BF539 Processor | 21-155 |

## SYSTEM DESIGN

| Pin Descriptions 22-1                              |

|----------------------------------------------------|

| Recommendations for Unused Pins 22-1               |

| Resetting the Processor 22-1                       |

| Booting the Processor 22-2                         |

| Managing Clocks 22-4                               |

| Managing Core and System Clocks 22-4               |

| Configuring and Servicing Interrupts 22-4          |

| Semaphores 22-5                                    |

| Example Code for Query Semaphore 22-6              |

| Data Delays, Latencies and Throughput 22-6         |

| Bus Priorities 22-7                                |

| External Memory Design Issues 22-7                 |

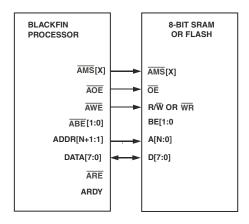

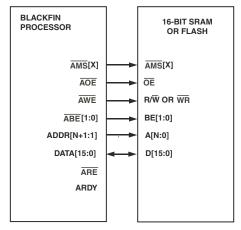

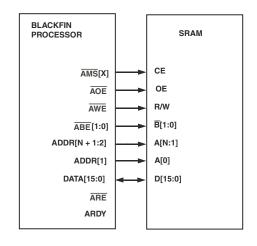

| Example Asynchronous Memory Interfaces 22-7        |

| Using SDRAMs Smaller than 16M byte 22-8            |

| Managing SDRAM Refresh During PLL Transitions 22-9 |

| Avoiding Bus Contention 22-11                      |

| High Frequency Design Considerations 22-12         |

| Point-to-Point Connections on Serial Ports 22-12   |

| Signal Integrity 22-12                             |

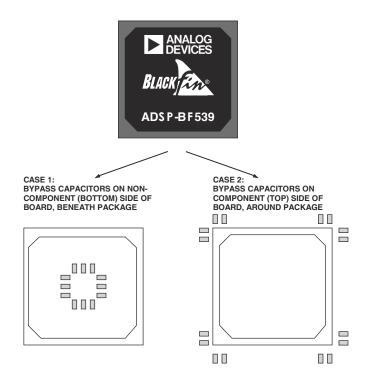

| Decoupling Capacitors and Ground Planes 22-14      |

| Oscilloscope Probes                            | 22-15  |

|------------------------------------------------|--------|

| Recommended Reading                            | 22-15  |

| BLACKFIN PROCESSOR DEBUG                       |        |

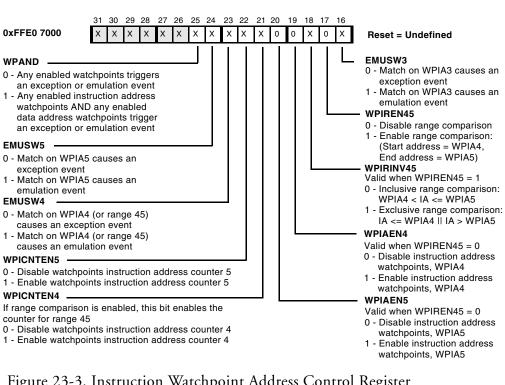

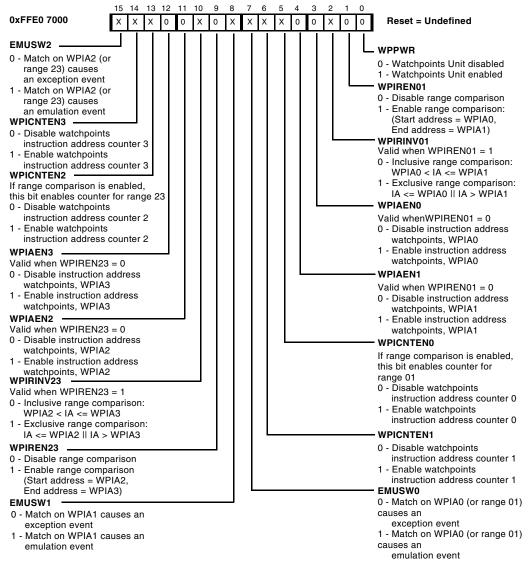

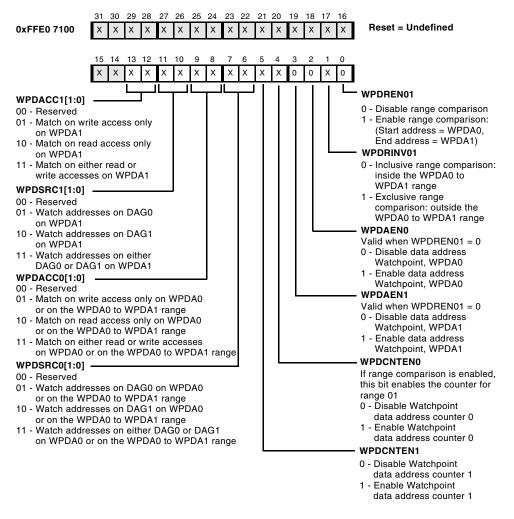

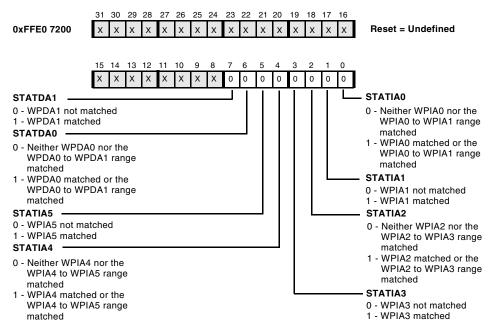

| Watchpoint Unit                                | 23-1   |

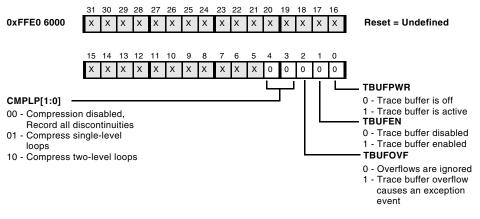

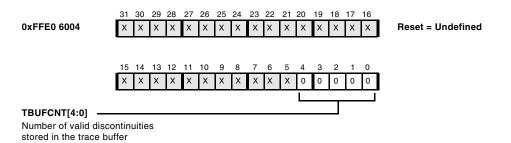

| Trace Unit                                     | 23-14  |

| TBUFCTL Register                               | 23-16  |

| TBUFSTAT Register                              | 23-17  |

| TBUF Register                                  | 23-18  |

| Code to Recreate the Execution Trace in Memory | 23-19  |

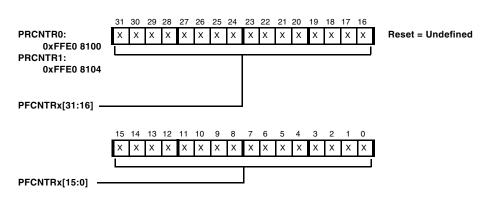

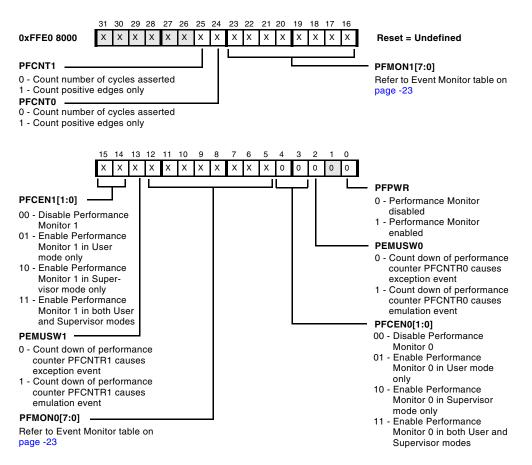

| Performance Monitoring Unit                    | 23-20  |

| PFCNTRn Registers                              | 23-20  |

| PFCTL Register                                 | 23-21  |

| Event Monitor Table                            |        |

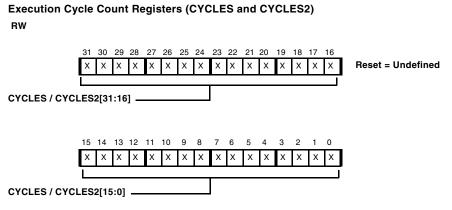

| Cycle Counter                                  | 23-25  |

| CYCLES and CYCLES2 Registers                   | 23-26  |

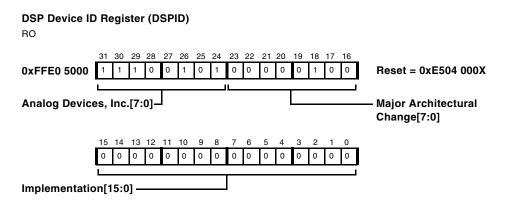

| Product Identification Register                | 23-26  |

| DSPID Register                                 | 23-27  |

| BLACKFIN PROCESSOR CORE MMR ASSIG              | NMENTS |

| L1 Data Memory Controller Registers            | A-2    |

| L1 Instruction Memory Controller Registers     | A-5    |

| Interrupt Controller Registers                 | A-8    |

| Core Timer Registers                           | A-9    |

| DSP Identification Register                    | A-10   |

|                                                |        |

| Trace Unit Registers           | A-10 |

|--------------------------------|------|

| Watchpoint and Patch Registers | A-11 |

| Performance Monitor Registers  | A-12 |

## SYSTEM MMR ASSIGNMENTS

| Dynamic Power Management Registers              | В-2  |

|-------------------------------------------------|------|

| System Reset and Interrupt Control<br>Registers | B-2  |

| Watchdog Timer Registers                        | В-3  |

| Real-Time Clock Registers                       | B-4  |

| UART Controller Registers                       | B-4  |

| SPI Controller Registers                        | B-7  |

| Timer Registers                                 | B-8  |

| Programmable Flag Registers                     | B-10 |

| SPORT Controller Registers                      | B-11 |

| External Bus Interface Unit Registers           | B-18 |

| DMA/Memory DMA Control Registers                | B-19 |

| Parallel Peripheral Interface (PPI) Registers   | В-23 |

| Two-Wire Interface Registers                    | B-23 |

| GPIO Ports C, D, and E Registers                | B-26 |

| MXVR Interface Registers                        | B-28 |

| CAN Registers                                   | B-34 |

|                                                 |      |

## **TEST FEATURES**

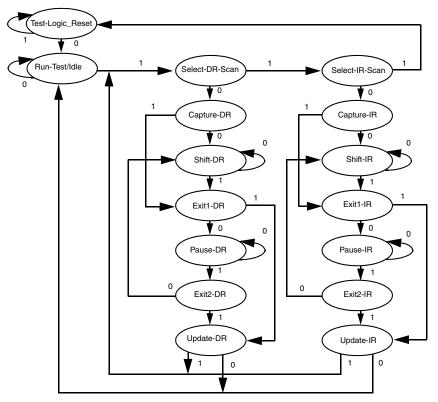

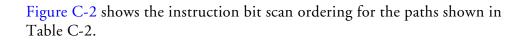

| JTAG Standard              | C-1 |

|----------------------------|-----|

| Boundary-Scan Architecture | C-2 |

| Instruction Register               | C-4 |

|------------------------------------|-----|

| Public Instructions                | C-5 |

| EXTEST – Binary Code 00000         | C-6 |

| SAMPLE/PRELOAD – Binary Code 10000 | C-6 |

| BYPASS – Binary Code 11111         | C-6 |

| Boundary-Scan Register             | C-7 |

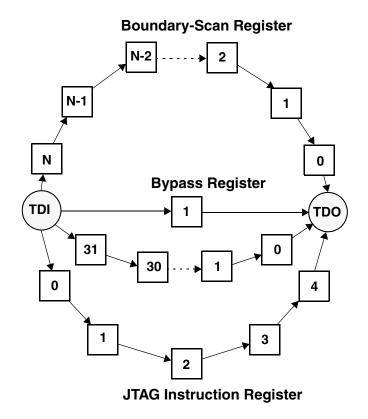

### NUMERIC FORMATS

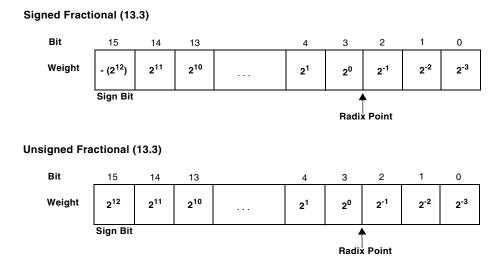

| Unsigned or Signed: Two's-complement Format | D-1         |

|---------------------------------------------|-------------|

| Integer or Fractional                       | D-1         |

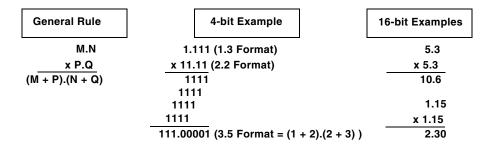

| Binary Multiplication                       | D-5         |

| Fractional Mode And Integer Mode            | D-6         |

| Block Floating-point Format                 | <b>D-</b> 7 |

# PREFACE

Thank you for purchasing and developing systems using Blackfin® processors from Analog Devices.

# **Purpose of This Manual**

ADSP-BF539 Blackfin Processor Hardware Reference contains information about the architecture for the ADSP-BF539 processors. The architectural descriptions cover functional blocks, buses, and ports, including all features and processes that they support.

For programming information, see ADSP-BF53x/BF56x Blackfin Processor Programming Reference. For timing, electrical, and package specifications, see ADSP-BF539/ADSP-BF539F Embedded Processor Data Sheet.

## **Intended Audience**

The primary audience for this manual is a programmer who is familiar with Analog Devices processors. The manual assumes the audience has a working knowledge of the appropriate processor architecture and instruction set. Programmers who are unfamiliar with Analog Devices processors can use this manual, but should supplement it with other texts, such as hardware and programming reference manuals that describe their target architecture.

# **Manual Contents**

This manual contains:

• Chapter 1, "Introduction"

Provides a high level overview of the processor. Architectural descriptions include functional blocks, buses, and ports, including features and processes they support.

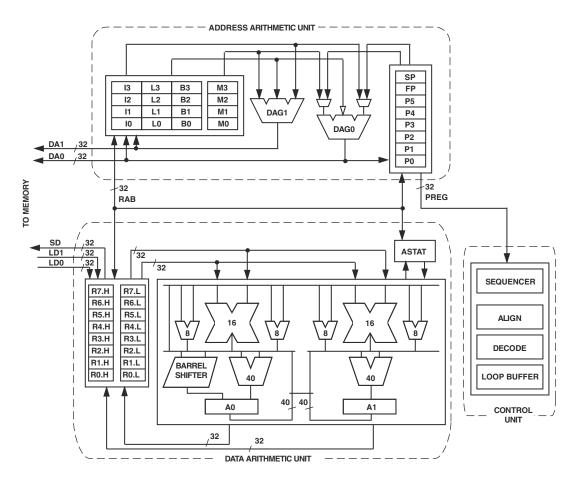

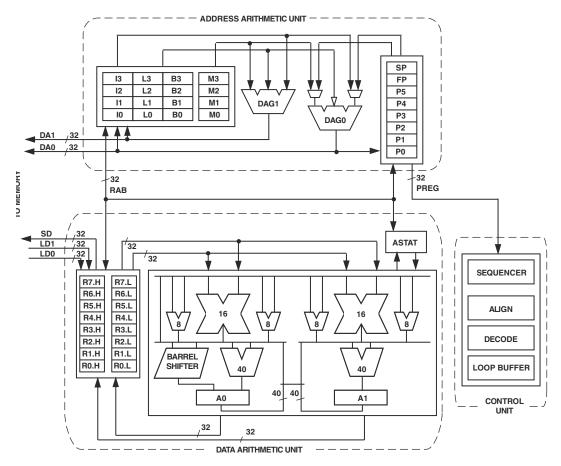

- Chapter 2, "Computational Units" Describes the arithmetic/logic units (ALUs), multiplier/accumulator units (MACs), shifter, and the set of video ALUs. The chapter also discusses data formats, data types, and register files.

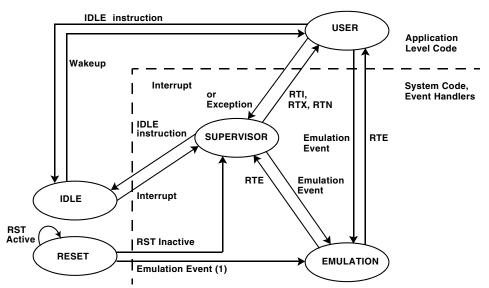

- Chapter 3, "Operating Modes and States" Describes the three operating modes of the processor: Emulation mode, Supervisor mode, and User mode. The chapter also describes Idle state and Reset state.

- Chapter 4, "Program Sequencer" Describes the operation of the program sequencer, which controls program flow by providing the address of the next instruction to be executed. The chapter also discusses loops, subroutines, jumps, interrupts, and exceptions.

- Chapter 5, "Data Address Generators" Describes the Data Address Generators (DAGs), addressing modes, how to modify DAG and Pointer registers, memory address alignment, and DAG instructions.

- Chapter 6, "Memory"

Describes L1 memories. In particular, details their memory architecture, memory model, memory transaction model, and memory-mapped registers (MMRs). Discusses the instruction, data, and scratchpad memory, which are part of the Blackfin processor core.

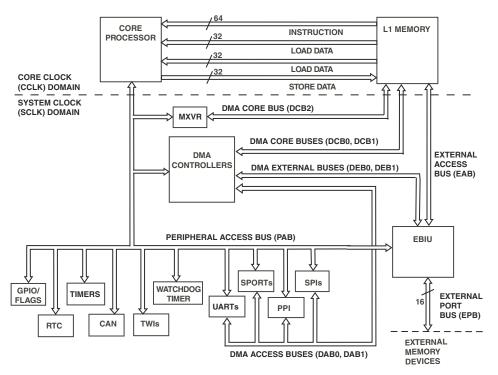

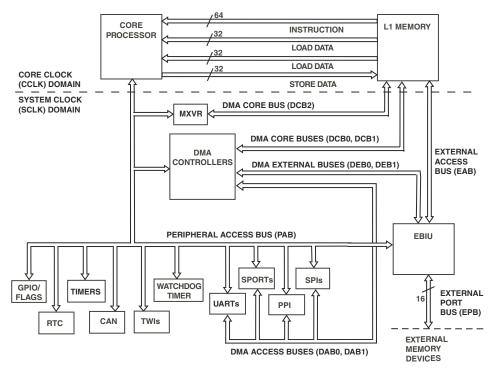

- Chapter 7, "Chip Bus Hierarchy" Describes on-chip buses, including how data moves through the system. The chapter also discusses the system memory map, major system components, and the system interconnects.

- Chapter 8, "Dynamic Power Management" Describes system reset and power-up configuration, system clocking and control, and power management.

- Chapter 9, "Direct Memory Access" Describes the peripheral DMA and memory DMA controllers. The peripheral DMA section discusses direct, block data movements between a peripheral with DMA access and internal or external memory spaces.

The memory DMA section discusses memory-to-memory transfer capabilities among the processor memory spaces and the L1, external synchronous, and asynchronous memories.

- Chapter 10, "SPI Compatible Port Controllers" Describes the serial peripheral interface (SPI) ports that provide an I/O interface to a variety of SPI compatible peripheral devices.

- Chapter 11, "Parallel Peripheral Interface" Describes the parallel peripheral interface (PPI) of the processor. The PPI is a half-duplex, bidirectional port accommodating up to 16 bits of data and used for digital video and data converter applications.

- Chapter 12, "Serial Port Controllers" Describes the independent, synchronous serial port controllers that provide an I/O interface to a variety of serial peripheral devices.

- Chapter 13, "UART Port Controllers" Describes the Universal Asynchronous Receiver/Transmitter (UART) ports, which convert data between serial and parallel for-

mats and includes modem control and interrupt handling hardware. The UARTs support the half-duplex IrDA® SIR protocol as a mode-enabled feature.

- Chapter 14, "Programmable Flags" Describes the programmable flags, including how to configure the pins as inputs and outputs and how to generate interrupts.

- Chapter 15, "General Purpose Input/Output Ports" Describes the general purpose I/O pins, including how to configure the pins as inputs and outputs.

- Chapter 16, "Timers"

Describes the general purpose timers that can be configured in any of three modes; the core timer that can generate periodic interrupts for a variety of timing functions; and the watchdog timer that can implement software watchdog functions, such as generating events to the Blackfin processor core.

#### • Chapter 17, "Real-Time Clock"

Describes a set of digital watch features of the processor, including time of day, alarm, and stopwatch countdown.

#### • Chapter 18, "External Bus Interface Unit"

Describes the External Bus Interface Unit of the processor. The chapter also discusses the asynchronous memory interface, the SDRAM controller (SDC), related registers, and SDC configuration and commands.

#### • Chapter 19, "CAN Module" Describes the CAN module, a low bit rate serial interface intended for use in applications where bit rates are typically up to 1Mbit/s.

Chapter 20, "Two-Wire Interface Controllers" Describes the Two-Wire Interface (TWI) controller, which allows a device to interface to an Inter IC bus as specified by the *Philips* I<sup>2</sup>C Bus Specification version 2.1 dated January 2000.

- Chapter 21, "Media Transceiver Module (MXVR)" Describes the Media Transceiver Module of the processor, which is capable of transmitting and receiving synchronous data streams, asynchronous packet data, and control messages on the MOST<sup>®</sup> bus. The MXVR is fully compatible with industry standard MOST network transceiver devices.

- Chapter 22, "System Design"

Describes how to use the processor as part of an overall system. It

includes information about interfacing the processor to external

memory chips, bus timing and latency numbers, semaphores, and a

discussion of the treatment of unused pins.

- Chapter 23, "Blackfin Processor Debug" Describes the Blackfin processor debug functionality, which can be used for software debugging and complements some services often found in an operating system.

- Appendix A, "Blackfin Processor Core MMR Assignments" Lists the core memory-mapped registers, their addresses, and cross-references to text.

- Appendix B, "System MMR Assignments" Lists the system memory-mapped registers, their addresses, and cross-references to text.

- Appendix C, "Test Features" Describes test features for the processor; discusses the JTAG standard, boundary-scan architecture, instruction and boundary registers, and public instructions.

- Appendix D, "Numeric Formats" Describes various aspects of the 16-bit data format. The chapter also describes how to implement a block floating-point format in software.

# What's New in This Manual

This is Revision 1.1 of the *ADSP-BF539 Blackfin Processor Hardware Reference*. This revision corrects minor typographical errors and the following issues:

- UART not half-duplex in Chapter 1, "Introduction"

- Core Double Fault Reset Enable bit (DOUBLE\_FAULT) set in the SWRST register in Chapter 3, "Operating Modes and States"

- RETI instructions need not be first in nested interrupts and complete table of hardware conditions causing hardware interrupts in Chapter 4, "Program Sequencer"

- Core priority over DMA when accessing L1 SRAM in Chapter 7, "Chip Bus Hierarchy"

- Removal of reference to datasheet, note on programming the STOPCK bit, and description of the WAKE bit in Chapter 8, "Dynamic Power Management"

- Obsolete DMA error address range deleted in Chapter 9, "Direct Memory Access"

- Termination of SPI TX DMA operations in Chapter 10, "SPI Compatible Port Controllers"

- Behavior on startup when using an external clock and receiver and transmitter enable bit names standardized on RSPEN and TSPEN in Chapter 12, "Serial Port Controllers"

- Note on the TINT bit in the TCNTL register in Chapter 16, "Timers"

- Sampling the ARDY pin when it is asserted and note on timing dependencies for the TRP and TRAS settings in the EBIU\_SDGCTL register in Chapter 18, "External Bus Interface Unit"

- Detection of recessive-to-dominant edges and note on CAN\_GIS and CAN\_GIF programming in Chapter 19, "CAN Module"

- Coverage of previously undocumented clock stretching behavior and miscellaneous changes across Chapter 20, "Two-Wire Interface Controllers"

- Clarification of watchpoint ranges in Chapter 23, "Blackfin Processor Debug"

# **Technical Support**

You can reach Analog Devices processors and DSP technical support in the following ways:

- Post your questions in the processors and DSP support community at EngineerZone<sup>®</sup>: http://ez.analog.com/community/dsp

- Submit your questions to technical support directly at: http://www.analog.com/support

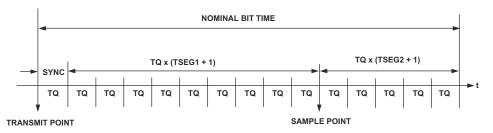

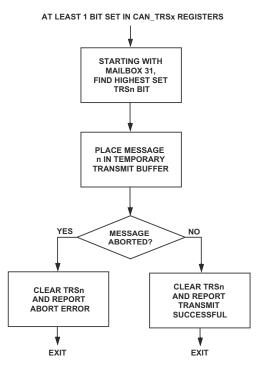

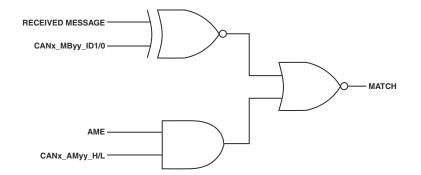

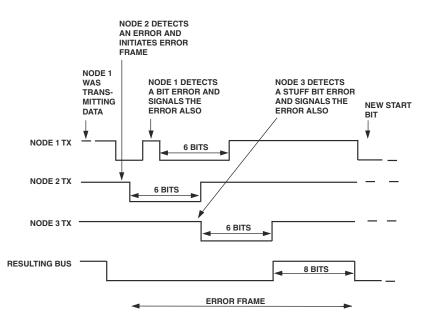

- E-mail your questions about processors, DSPs, and tools development software from CrossCore<sup>®</sup> Embedded Studio or VisualDSP++<sup>®</sup>: