# PLC DCS Analog Input Module Design Breaks Barriers in Channel-to-Channel Isolation and High Density

By Van Yang, Songtao Mu, and Derrick Hartmann

# Share on 🕥 🚹 in

# Introduction

In high end factory automation applications such as gas and oil plants and power plants, the requirements of low EMI, small size, high reliability, and low cost are especially challenging for channel-to-channel isolated designs. For this reason, the standard module implementation has a channel density that is typically limited to only four or eight channels, with only hundreds of volts of channel-to-channel isolation.

This article will briefly discuss isolation in the process control analog input module and the traditional approaches to achieving this. It then outlines an alternative high density, easy to design channel-to-channel isolation analog input module architecture. Test results are included that show that the 16-channel, 2.5 kV rms channel-to-channel isolation demo module easily passes the EN55022, Class B isolation standard.

# Isolation in the Process Control Analog Input Module

Galvanic isolation is the principle of physically and electrically separating two circuits, so that there is no direct conduction path but data and power can still be exchanged. This is typically achieved using transformers, optocouplers, or capacitors. Isolation is used to protect circuitry and human beings, break ground loops, and improve common-mode voltage and noise rejection performance.

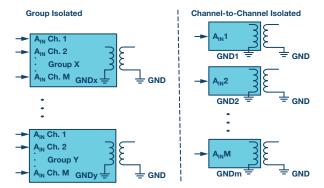

Typically process control inputs are either group isolated or channel-tochannel isolated (see Figure 1). For group isolation, a number of input channels are grouped together to share a single isolation barrier, including power isolation and signal isolation. This saves cost over channel-to-channel isolation, but it limits the common-mode voltage difference between channels in the group, meaning they should all be placed in the same zone. Channel-to-channel isolation, as in the right of Figure 1, is always favorable for its improved robustness. That said, it comes at a much higher cost perchannel, so this trade-off must be carefully assessed by plant builders.

Figure 1. Group isolation and channel-to-channel isolation.

With a channel-to-channel isolation design, every channel needs dedicated power isolation and signal isolation. The isolation is one of the key limitations for input module channel density, EMI, cost, and reliability. In modern designs, a digital isolator is used per channel for data isolation. A typical digital isolator, such as the ADuM141E, would have four isolated data channels in a 16-lead SOIC (6.2 mm  $\times$  10 mm) package. Power isolation is still required per channel, though, so let's discuss three traditional approaches to power isolation: multitaps transformer, push-pull design, and isolated dc-to-dc modules.

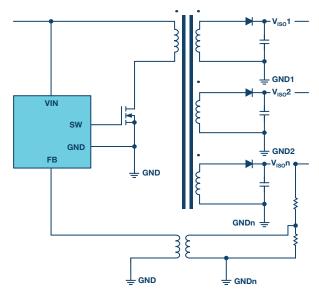

Figure 2 shows a flyback isolation dc-to-dc architecture with a multitap transformer. A flyback converter drives the transformer to generate multiple outputs on the taps. It's a mature power architecture but has six major disadvantages for process control applications, which are:

- It needs a customized transformer with multitaps and a shield to control EMI. This is hard to achieve in a small form factor with sufficient reliability.

- 2. Only one channel could be used for a feedback control loop, meaning that the other channels are more loosely regulated. This needs to be carefully evaluated to ensure reliable operation.

- 3. Channel density is limited by specific transformer placement. For the power coming from each tap output, the transformer is placed as the center of the analog input module with each input channel laid out in fanout sectors around the transformer, limiting the analog input module card channels to four or eight.

- 4. Interference from one channel can be coupled into other channels through the coupling capacitors between the taps of the transformer.

- The isolation voltage level. Multitap transformers can only achieve hundreds of volts of channel-to-channel isolation unless special insulation materials or design are incorporated, which significantly increases the transformer cost.

- 6. The high cost of achieving UL/CSA certification for the customized transformer.

Figure 2. Multitap transformer power isolation design.

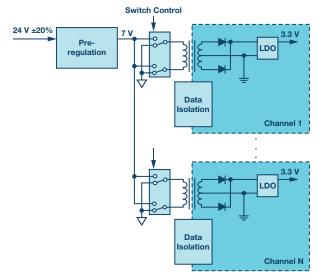

Another approach is to use a separate transformer per channel and use a push-pull approach to isolating each channel. In this approach, no feedback is used. Instead, a well-regulated supply (for example, 7 V) is used to drive each of the transformers, which is then further regulated on the secondary side using an LDO. This approach is feasible as the current draw on the secondary side is relatively low, which makes adequate regulation possible.

Some of the drawbacks of this approach are the requirement for preregulation as well as additional components per channel. The transformer selected must meet the isolation rating required. The preregulation, as well as a transformer, switches, and an LDO per channel take up board space and add cost. There is also a significant evaluation effort required to ensure that the regulation is sufficient under all conditions.

Figure 3. Push-pull isolation design.

Using surface-mount isolated dc-to-dc modules certified by UL/CSA make the isolated power design much easier and can improve channel density

while increasing isolation voltage to thousands of volts. That said, the cost is relatively high and typically these can only pass the EN55022 Class A. These modules may also have conducted electromagnetic interference issues as most of the modules PWM frequency are below 1 MHz to minimize the electromagnetic radiation interference. Also, the majority of the process control analog input modules consume less than 10 mA current, far less than most of the isolated power modules in the market.

All three traditional approaches discussed struggle to meet the required isolation performance and cost. These approaches also still require separate data isolators per channel, adding additional space and cost. What if the power isolation could be included as part of the data isolator? It can, and it is.

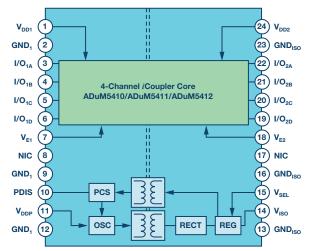

ADI *i*Coupler<sup>®</sup> techology and *iso*Power<sup>®</sup> technology are widely used in the industrial and automotive market and these two technologies can be integrated into a single package. Taking the ADuM5411 as an example, per the block diagram shown in Figure 4, this device includes complete power isolation and four channels of data isolation in a 7.8 mm × 8.2 mm, 24-lead TSSOP package. It offers up to 150 mW output, enough for analog input signal conditioning and digitizing and passes the 2500 V rms UL1577 isolation standard. What's more, the CMTI (common-mode transient immunity) is greater than 75 kV/ $\mu$ s, making it ideal for harsh industrial environments, such as power plants, where high transient voltages and currents exist.

Figure 4. ADuM5411 block diagram.

Due to the high integration of both data and power isolation, the analog input module design is greatly simplified and higher channel densities are possible. It enables the possibility of providing 16 or more channels in the same space as eight channels using older isolation methods.

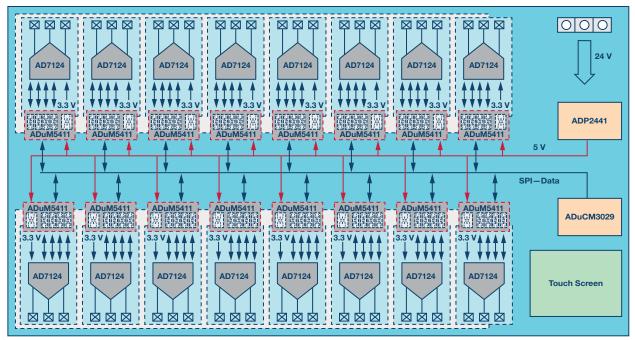

A 16-channel, channel-to-channel isolation temperature input module was designed and tested using this isolation approach (see Figure 5). The ADuM5411 devices in the module provide isolated power and data to each of the 16 temperature input channels. The thermocouple and/or RTD measurements are performed by highly integrated temperature front-end ICs (AD7124, or AD7792) providing additional space saving over more discrete designs. The ADP2441 converts the 24 V backplane supply to 3.3 V to power the MCU, touchscreen, and the ADuM5411. Each input channel requires an area of only 63.5 mm  $\times$  17.9 mm.

Figure 5. 16-channel temperature channel-to-channel isolation input module block diagram.

## Layout Design for ADuM5411

The ADuM5411 uses a switching frequency of 125 MHz. Due to the high number of channels, special care was taken to ensure the board would pass the electromagnetic radiation interference test per EN55022 to Class B.

To minimize the radiated emission, the principles used were to minimize the power draw and minimize the current loop return path. The power was minimized by using low power integrated temperature front-end ICs. This means less power will be drawn across the isolation barrier, meaning there will also be less energy radiated. The AD7124 only draws 0.9 mA when fully active. To minimize the current return loop, both ferrite beads as well as a small amount of stitching capacitance were used.

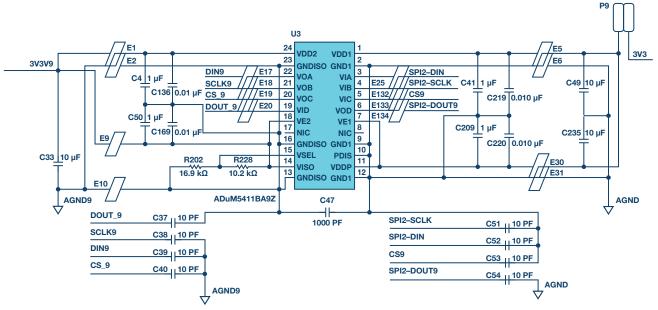

Ferrite beads are a useful method to control the radiating signal at its source by presenting a much higher impedance than a PCB trace. Referring to Figure 6, ferrite beads were placed in series with the ADuM5411's pins. The frequency response of the ferrite beads is a very important consideration. The ferrite bead used is BLM15HD182SN1, which provides greater than 2 k $\Omega$ —between 100 MHz and 1 GHz frequency range. The ferrite beads should be placed as close to the ADuM5411's pad as possible. E9 on the VISO path and E10 on the GNDISO path are the most critical ferrite beads.

Figure 6. ADuM5411 schematic.

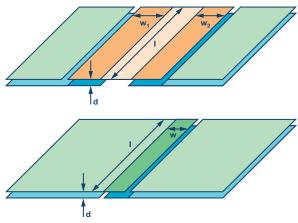

Capacitance can also be used to provide a low impedance return path, thus reducing emissions. One method to do this is to use a surface-mounted safety rated capacitor crossing the barrier, guaranteed to meet standards for creepage, clearance, and withstand voltage. These capacitors are available from suppliers like Murata or Vishay. This method is only effective up to around 200 MHz, though, due to the inductance introduced by mounting the capacitor. For this reason, a more effective technique is to build a stitching capacitance internal to the PCB under the ADuM5411. This could be a floating stitching capacitor or an overlapping stitching capacitor, as shown in Figure 7.

Figure 7. Floating stitching capacitor and overlapping stitching capacitor.

For the floating stitching capacitor, two serial capacitors are built in, C1 and C2. The total capacitance is calculated by Equation 1.

$$C = \frac{C1 \times C2}{C1 + C2}, C1 = \frac{lw_1\varepsilon}{d}, C2 = \frac{lw_2\varepsilon}{d}$$

#### where:

$\epsilon$  is the permittivity of the PCB insulation material, 4.5 for FR4 material

For the overlapping stitching capacitor, the capacitance is calculated by Equation 2.

$$C1 = \frac{lw\varepsilon}{d}$$

,  $\varepsilon$

#### where:

$\epsilon$  is the permittivity of the PCB insulation material,  $4\times 10^{-1}$  1 F/m for FR4 material

With the same material, area, and distance, the total capacitance value of floating stitching is half that of the overlapping stitching, but the thickness of the insulation material is doubled. Reinforced insulation, per IEC60950 2.10.6.4, requires 0.4 mm (15.74 mils) minimum insulation material thickness in the interior layers but basic insulation has no such requirement. As the ADuM5411 only provides 2.5 kV rms basic isolation, an overlapping stitching capacitor was chosen to maximize the capacitance. The thickness of the interior layers has also been controlled to 5 mils for the same reason.

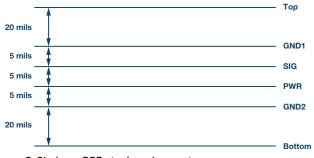

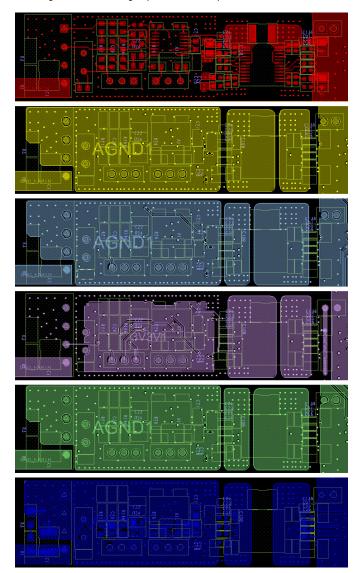

The 16-channel, channel-to-channel temperature input module PCB uses a 6-layer board. To maintain mechanical and EMI performance, the top and bottom layers were controlled to 20 mils and interior layers to 5 mils, as per Figure 8.

Figure 8. Six-layer PCB stack assignment.

As per Figure 9, the overlap stitching capacitors' planes are built in the GND1, SIG, PWR, and GND2. The planes on GND1 and PWR are connected to the ADuM5411's secondary side and the planes in the SIG and GND2 are connected to ADuM5411's primary side. This means three parallel stitching capacitors are formed between GND1 and SIG, SIG and PWR, PWR and GND2. The width of the overlap area is 4.5 mm, and the length is 17 mm, meaning the total stitching capacitance is 72 pF.

Figure 9. Six-layer PCB layout of the ADuM5411 area.

# Test Results Against the EN55022 Specification

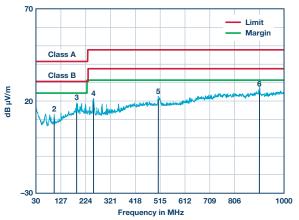

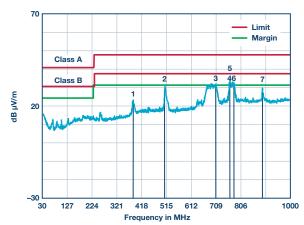

Two sets of EMI tests were performed at 10 m, as per the EN55022 specification. For the first test, a board with stitching capacitance was used, as shown in Figure 10. Figure 11 shows the results, it passed the EN55022 Class B standard with about 11.59 dB margin. For the second test, a board with no stitching capacitance was used, and, instead, external safety capacitors, KEMET C1812C102KHRACTU 3 kV, 150 pF, were mounted on the board. Figure 12 shows the results—it passed the EN55022 Class B standard with 0.82 dB margin.

Figure 10. Stitching capacitors built into the PCB without safety capacitors.

Figure 11. Stitching capacitors built into PCB EN55022 Class B test result.

Figure 12. The no stitching capacitance, but with safety capacitors PCB, EN55022 Class B test result.

The results proved that stitching capacitors under the IC is a more effective decoupling method than the safety capacitors.

# Conclusion

Channel-to-channel isolation is often viewed as a design challenge in high end process control systems. ADI's *iso*Power technology and *i*Coupler technology enables significant increases in channel density over traditional digital and power isolation approaches. They also greatly simplify the design task and can improve channel robustness and reliability. With stitching capacitor built into the PCB, or safety capacitor mounted aside the PCB, EMI radiation can be easily controlled to pass EN55022 Class B or Class A. It's a breakthough in technology.

## References

ADuM5411 data sheet. Analog Devices, Inc.

AN-0971, *Recommendations for Control of Radiated Emissions with isoPowerDevices*. Analog Devices, Inc.

AN-1349, *PCB Implementation Guidelines to Minimize Radiated Emissions on the ADM2582E/ADM2587E RS-485/RS-422 Transceivers.* Analog Devices, Inc.

Van Yang [van.yang@analog.com] Van Yang is a field application engineer at Analog Devices in Shanghai, China. He joined ADI in 2015 to support regional medical and industrial customers in China. Prior to joining ADI, Van worked at Texas Instruments as an FAE for four years. Van earned his master's degree in communication and information systems from Huazhong University of Science and Technology in Wuhan, in 2011. In his spare time he is a super fan of basketball and enjoys hiking.

Songtao Mu [songtao.mu@analog.com] Songtao Mu is a system applications engineer in Analog Devices' Industrial Automation Group. He is based in Shanghai, China. Prior to join Analog Devices, Songtao worked at Schneider Electric Co., Ltd., as a hardware design engineer for over eight years. Songtao holds a bachelor's degree in industrial automation from the Harbin institute of Technology University, China.

Derrick Hartmann [derrick.hartmann@analog.com] Derrick Hartmann is a system applications engineer in the Industrial Automation Group at Analog Devices. He is based in Wilmington, MA. Prior to his current role, Derrick was a product applications engineer supporting Analog Devices' industrial DAC portfolio. Derrick holds a degree in electronic engineering from the University of Limerick, Ireland.

Songtao Mu

Van Yang

Also by this Author:

PLC Evaluation Board Simplifies Design of Industrial Process Control Systems