# 高速转换器技术的进步对下一代 无线通信系统设计的支持

作者: Yi Zhang和Michele Viani, ADI公司高速转换器部 门应用工程师

### 简介

无线通信网络正在迅猛发展。消费者对增强数据服务的需求日益增长,对带宽的使用率也在上升。新一代无线通信系统要求更高的数据吞吐速率、更低的功耗和更高的可靠性。这些要求通常互相冲突。为了满足这些要求需要有高采样速率、高信号带宽、高效率的数模转换器(DAC)解决方案。新一代高速DAC产品具有GSPS采样率和输入数据速率,可为多频段、多标准无线电基站提供多载波GSM兼容性能,同时能够降低系统的总功耗和散热密度。本文讨论高速转换器如何藉由更高的采样速率、更宽的数据带宽以及更低的功耗,来帮助系统设计人员推动无线通信系统的创新。

#### 高带宽对系统的挑战

现代移动基站的发射带宽超过300 MHz并不是罕见现象。为了支持更宽数据带宽和数字预失真技术的要求,提升了对高速DAC产品的可用信号带宽和动态性能标准指标要求。为了实现更高的系统带宽,存在三方面挑战。

第一,更高的信号带宽要求DAC采样速率更快。奈奎斯特一香农采样理论规定,转换器采样速率至少应为待合成信号频率的两倍。因此,在不考虑其它设计约束的情况下,DAC采样速率需要以信号带宽2倍的速率提高。而且模拟重构滤波是系统设计的另一重要因素,为了简化这个滤波器的设计需要有更高的DAC采样率。在无线发射机中

使用矩形模拟滤波器既不可行,也无甚效果。实践中,系统要求DAC采样速率相对于合成信号带宽有一定的过采样比,以便在目标信号与需要抑制的高频DAC采样镜像之间构建一个滤波器过渡带。例如,如果要合成的信号带宽是±50 MHz且中心频率为150 MHz,则DAC输出信号的上限是200 MHz;而如果要合成的信号带宽是±150 MHz且中心频率为300 MHz,则DAC输出信号的上限是450 MHz。可以看出,第二种情况对DAC采样速率的要求要高得多。

第二,更高的信号带宽要求转换器数据接口更快且更可靠。所需的信号带宽与发射数据的吞吐速率成比例提高。要利用IQ调制实现300 MHz系统带宽,双通道DAC(I和Q)的组合输入数据速率需为750 MSPS(假设滤波器滚降系数为0.2)。因此,输入数据周期为1.33 ns,必须尽可能消除数据总线的位间时序不对准情况以便满足建立和保持时序要求,这会给系统设计人员带来巨大压力。若采用传统的并行数据接口方案,如LVDS和CMOS等,实现难度将非常大。新型JESD204B高速串行接口提供一种可靠且可扩展的解决方案,支持升级到更高的数据速率。

第三,集成电路(IC)器件并非理想器件。DAC也不例外。 更高的输出带宽要求DAC器件提供更好的动态性能,原因 有二:首先,动态范围一般随着DAC输出频率的提高而降 低。此外,当带宽较大时,落入目标频段内的杂散成分往 往也更多。然而,系统杂散要求并不随着信号带宽变大而 提高或而降低。无论支持多大的信号带宽,移动基站都要 满足发射模板要求。具有出色动态性能的DAC会简化系统 的频率规划和滤波工作。

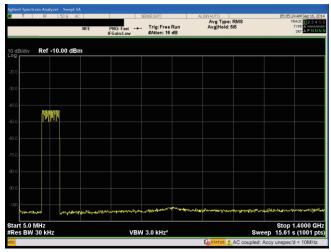

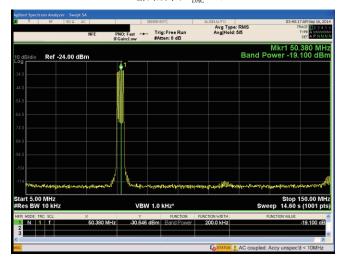

图1和图2显示了AD9144 DAC以2,800 MSPS的DAC采样速率合成一个80 MHz信号(16载波C-WCDMA)的实测频谱性能。

## MS-2773

图1. AD9144 DAC合成16载波C-WCDMA信号的实测宽带性能 (最高达奈奎斯特频率), $f_{\rm DAC}$  = 2,800 MSPS

图2. ADRF6720 QMOD输出端的实测宽带性能, 3 GHz RF频率,利用同样的AD9144 DAC输出 (如同图1)驱动QMOD

#### 系统的低功耗和高可靠性挑战

为了提高发射带宽和数据容量,系统设计人员还面临着其它挑战,包括功耗、散热和系统可靠性。这些方面常常不利于实现更高系统带宽,有时甚至与这一目标相冲突。因此,系统设计人员需要一种能够在同一封装中实现更高特性集成度、更低功耗、更低工作发热密度、更宽带宽的新型DAC产品。

高速DAC产品近年来发展迅速,并且集成了更多的数字和 模拟特性。DAC片内时钟倍频器PLL和通信专用信号处理 特性就是两个突出的例子。过去,这些特性是在系统中的其它地方实现,例如高速时钟合成芯片器和基带ASIC/FPGA。 具备这些功能的DAC不仅能降低总BOM成本,而且可简化设计并提高可靠性。由于DAC内置时钟倍频器,系统仅需为器件提供低频参考时钟。时钟倍频器锁定外部参考时钟,产生DAC内部使用的高速采样时钟。这样就可以减少对高速时钟耦合和PCB走线阻抗匹配的担忧。功率检测和保护等新数字特性为RF信号链提供额外的保护,防止其受到超范围信号或异常系统行为损害。尽管集成度明显提高,DAC器件的功耗与前代产品相比却大致上保持稳定,甚至降低,这些归功于硅工艺节点尺寸更小和高速DAC技术的进步,这对解决这些系统挑战发挥了巨大作用。

除了功耗和碳排放更低以外,低功耗器件的另一大好处是 热量密度更低。无线通信系统通常是局限在水密性密闭的 金属机箱内。尺寸和重量限制一般不允许采用主动冷却。 IC器件产生的热量需通过机箱散去。机箱内部的空腔和 PCB温度可能非常高,以至于会影响系统的长期可靠性。 积累的热量可能会影响PCB机械特性、器件与板之间的焊 接接头并加速老化,即IC器件电气特性的也会产生长期偏 移。系统中的热分布/散热并不均匀,产生热量的主要是信 号处理密集的器件,高速DAC是其中之一。因此,特性丰 富且功耗很低的DAC对系统设计人员极具吸引力。

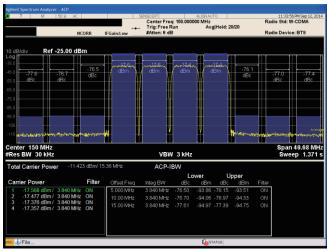

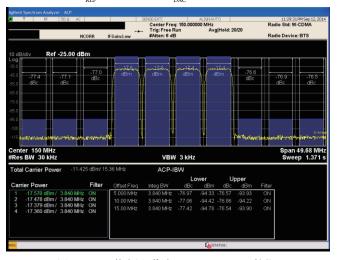

图3和图4分别显示了AD9144在开启和关闭DAC片内时钟倍 频器的情况下,以1966 MSPS的DAC采样速率合成一个4载 波C-WCDMA信号的实测性能。

<sup>&</sup>lt;sup>1</sup> www.analog.com

图3. AD9144的实测4载波C-WCDMA ACLR性能, 150 MHz输出频率,片内时钟倍频器使能, f<sub>REF</sub> = 245.76 MHz, f<sub>DAC</sub> = 1,966 MSPS

图4. AD9144的实测4载波C-WCDMA ACLR性能, 150 MH2输出频率,片内时钟倍频器禁用,  $f_{DAC}=1,966$  MSPS

#### 系统在通用平台设计方面的挑战

在要求更广覆盖范围和更宽带宽的同时,消费者对数据服务需求的快速扩张,需要有则呼唤多标准无线电(MSR)基站支持。不同的无线电技术以及不断增加的频率分配使控制网络和降低成本变得更为复杂。为了满足这些需求,必须通过有效且相对廉价的方案来解决MSR基站构建问题,即通用平台设计。DAC技术进步支持基站设计的这种发展。一般认为多载波GSM (MC-GSM)是对动态范围要求最苛刻的空中标准。MC-GSM测试常用来判断一款DAC产品是否支持通用平台设计。

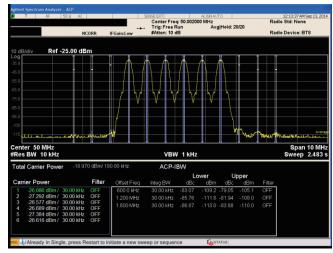

图5和图6显示了AD9144以1,966 MSPS的DAC采样速率合成一个6C-GSM信号的实测性能。

图5. AD9144的实测6 C-GSM IMD性能, 50 MHz DAC输出频率, $f_{DAC}$  = 1,966 MSPS

图6. AD9144的实测6 C-GSM宽带性能, 50 MHz DAC输出频率, $f_{DAC}=1,966$  MSPS

#### 小结

现代无线通信网络正在朝着更多数据服务和更高带宽使用率方向发展。为了支持这一趋势,新一代无线通信系统必须具备更高的数据吞吐速率、更低的功耗和更高的可靠性。高速DAC技术的进步,例如ADI公司推出的AD9144,可以支持下一代多标准无线电设计,并且已经帮助系统设计人员在多个关键技术维度上实现了突破性创新。

# **MS-2773**

#### 作者简介

Yi Zhang是ADI公司高速转换器部门应用工程师。他于2007年加入ADI公司,拥有超过8年的高速转换器产品和高速混合信号应用经验。他为好几代高速数模转换器(DAC)产品撰写了数据手册、应用笔记和技术文章。他拥有康奈尔大学电气工程硕士学位。

Michele Viani是ADI公司高速转换器部门应用工程师,已工作5年。他既是产品工程师,也是应用工程师,负责评估高速数模转换器产品,并向客户提供技术支持以解决实施问题。他拥有伦斯勒理工学院电气工程学士学位。

#### 资源

分享本文

Linked in