特性

## *MAX7456*

# 集成了EEPROM的 单通道、单色随屏显示器

#### 概述

MAX7456单通道、单色随屏显示(OSD)发生器省去了外部 视频驱动器、同步分离器、视频开关以及EEPROM,有效 降低系统成本。MAX7456采用符合NTSC和PAL制式的256 个用户可编程字符,适合全球市场。MAX7456能够方便 地以任意字符、尺寸显示各种信息,例如公司标识、常 用图形、时间、日期等。MAX7456预先装载了256个字符 和图形,并可通过SPI™接口进行在线编程。

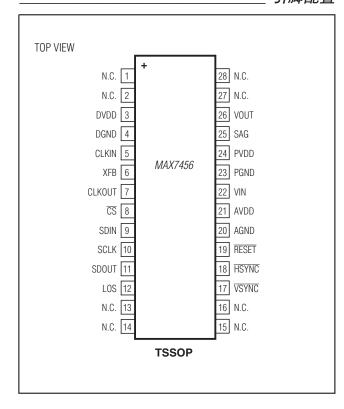

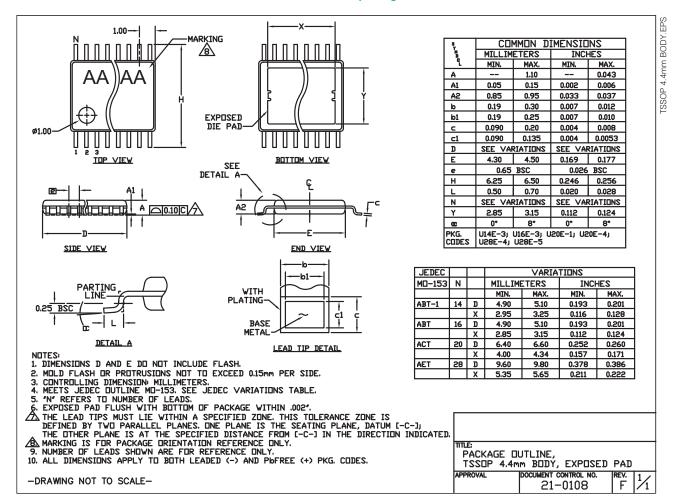

MAX7456提供28引脚TSSOP封装,工作于扩展级(-40°C至 +85°C)温度范围。

应用

安全监控系统

安全监控摄像机

工业应用

室内娱乐系统

消费类电子

- ◆ 256个用户定义字符或图形存储于EEPROM

- ◆ 字符大小为12 x 18象素

- ◆ 闪烁、反色和背景控制字符

- ◆ 可逐行设置亮度

- ◆ 最多显示16行 x 30列字符

- ◆ 视频驱动器输出带有衰减补偿

- ♦ LOS、VSYNC、HSYNC和时钟输出

- ◆ 内置同步发生器

- ◆ 兼容于NTSC和PAL

- ◆ SPI兼容串行接口

- ◆ 出厂时带有预先编程的字符组

定购信息

| PART          | PIN-PACKAGE  | LANGUAGE |

|---------------|--------------|----------|

| MAX7456EUI+   | 28 TSSOP-EP* | English/ |

| IVIAX7430LUI+ | 20 13301 -Li | Japanese |

\*EP = 裸焊盘。

+表示无铅/符合RoHS标准的封装。

注:该器件工作于-40°C至+85°C温度范围。

#### 引脚配置在数据资料的最后给出。

SPI是Motorola, Inc.的商标。

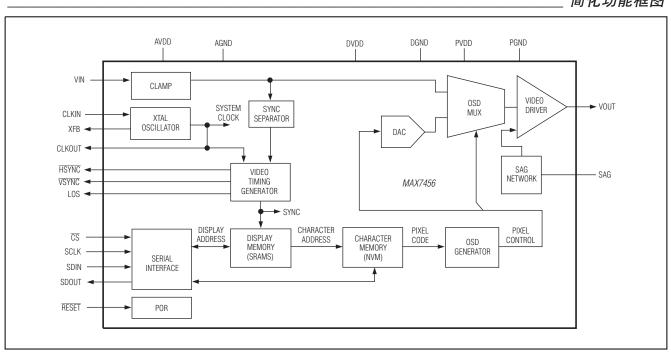

#### 简化功能框图

本文是英文数据资料的译文,文中可能存在翻译上的不准确或错误。如需进一步确认,请在您的设计中参考英文资料。 有关价格、供货及订购信息,请联络Maxim亚洲销售中心: 10800 852 1249 (北中国区), 10800 152 1249 (南中国区), 或访问Maxim的中文网站: china.maximintegrated.com。

## 集成了EEPROM的 单通道、单色随屏显示器

#### **ABSOLUTE MAXIMUM RATINGS**

| AVDD to AGND                                                         | 0.3V to +6V                        |

|----------------------------------------------------------------------|------------------------------------|

| AGND to DGNDAGND to PGND                                             | 0.3V to +0.3V                      |

| DGND to PGND<br>VIN, VOUT, SAG to AGND<br>HSYNC, VSYNC, LOS to AGND. | 0.3V to (V <sub>AVDD</sub> + 0.3V) |

| RESET to AGND                                                        |                                    |

| CLKIN, CLKOUT, XFB to DGND0.3V to (V                  | DVDD + 0.3V  |

|-------------------------------------------------------|--------------|

| SDIN, SCLK, CS, SDOUT to DGND0.3V to (V               | DVDD + 0.3V) |

| Maximum Continuous Current into VOUT                  | ±100mA       |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |              |

| 28-Pin TSSOP (derate 27mW/°C above +70°C)             | 2162mW*      |

| Operating Temperature Range4                          | 0°C to +85°C |

| Junction Temperature                                  | +150°C       |

| Storage Temperature Range60                           | °C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C       |

|                                                       |              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{AVDD} = +4.75V \text{ to } +5.25V, V_{DVDD} = +4.75V \text{ to } +5.25V, V_{PVDD} = +4.75V \text{ to } +5.25V, T_A = T_{MIN} \text{ to } T_{MAX}.$  Typical values are at  $V_{AVDD} = V_{DVDD} = V_{PVDD} = +5V, T_A = +25^{\circ}C,$  unless otherwise noted.) (Note 1)

| PARAMETER                 | SYMBOL             | CONDITIONS                                                                                            | MIN  | TYP     | MAX  | UNITS  |

|---------------------------|--------------------|-------------------------------------------------------------------------------------------------------|------|---------|------|--------|

| POWER SUPPLIES            |                    |                                                                                                       | '    |         |      |        |

| Analog Supply Voltage     | Vavdd              |                                                                                                       | 4.75 | 5       | 5.25 | V      |

| Digital Supply Voltage    | V <sub>D</sub> VDD |                                                                                                       | 4.75 | 5       | 5.25 | V      |

| Driver Supply Voltage     | V <sub>P</sub> VDD |                                                                                                       | 4.75 | 5       | 5.25 | V      |

| Analog Supply Current     | lavdd              | $V_{IN}$ = 1V <sub>P-P</sub> (100% white flat field signal), VOUT load, R <sub>L</sub> = 150 $\Omega$ |      | 24      | 35   | mA     |

| Digital Supply Current    | ldvdd              | $V_{IN}$ = 1V <sub>P-P</sub> (100% white flat field signal), VOUT load, R <sub>L</sub> = 150 $\Omega$ |      | 25      | 30   | mA     |

| Driver Supply Current     | IPVDD              | $V_{IN}$ = 1V <sub>P-P</sub> (100% white flat field signal), VOUT load, R <sub>L</sub> = 150 $\Omega$ |      | 58      | 80   | mA     |

| NONVOLATILE MEMORY        | •                  |                                                                                                       |      |         |      |        |

| Data Retention            |                    | $T_A = +25^{\circ}C$                                                                                  |      | 100     |      | Years  |

| Endurance                 |                    | $T_A = +25^{\circ}C$                                                                                  |      | 100,000 |      | Stores |

| DIGITAL INPUTS (CS, SDIN, | RESET, SCLK)       |                                                                                                       |      |         |      |        |

| Input High Voltage        | VIH                |                                                                                                       | 2.0  |         |      | V      |

| Input Low Voltage         | VIL                |                                                                                                       |      |         | 0.8  | V      |

| Input Hysteresis          | V <sub>H</sub> YS  |                                                                                                       |      | 50      |      | mV     |

| Input Leakage Current     |                    | $V_{IN} = 0$ or $V_{DVDD}$                                                                            |      |         | ±10  | μΑ     |

| Input Capacitance         | CIN                |                                                                                                       |      | 5       |      | pF     |

| DIGITAL OUTPUTS (SDOUT,   | CLKOUT, VSY        | NC, HSYNC, LOS)                                                                                       |      |         |      |        |

| Output High Voltage       | VoH                | ISOURCE = 4mA (SDOUT, CLKOUT) 2.4                                                                     |      |         |      | V      |

| Output Low Voltage        | VoL                | I <sub>SINK</sub> = 4mA 0.45                                                                          |      |         |      | V      |

| Tri-State Leakage Current |                    | SDOUT, $\overline{CS} = V_{DVDD}$                                                                     | ±10  | μΑ      |      |        |

<sup>\*</sup>As per JEDEC51 Standard (Multilayer Board).

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = +4.75 \text{V to } +5.25 \text{V}, V_{DVDD} = +4.75 \text{V to } +5.25 \text{V}, V_{PVDD} = +4.75 \text{V to } +5.25 \text{V}, T_{A} = T_{MIN} \text{ to } T_{MAX}. \text{ Typical values are at } V_{AVDD} = V_{DVDD} = V_{PVDD} = +5 \text{V}, T_{A} = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.}) \text{ (Note 1)}$

| PARAMETER                             | SYMBOL                                          | CONDITIONS                                                                                                                | MIN                        | TYP | MAX                        | UNITS            |

|---------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|----------------------------|------------------|

| CLOCK INPUT (CLKIN)                   |                                                 | ·                                                                                                                         |                            |     |                            |                  |

| Clock Frequency                       |                                                 |                                                                                                                           |                            | 27  |                            | MHz              |

| Clock-Pulse High                      |                                                 |                                                                                                                           | 14                         |     |                            | ns               |

| Clock-Pulse Low                       |                                                 |                                                                                                                           | 14                         |     |                            | ns               |

| Input High Voltage                    |                                                 |                                                                                                                           | 0.7 x<br>V <sub>DVDD</sub> |     |                            | V                |

| Input Low Voltage                     |                                                 |                                                                                                                           |                            |     | 0.3 x<br>V <sub>DVDD</sub> | V                |

| Input Leakage Current                 |                                                 | $V_{IN} = 0V$ or $V_{DVDD}$                                                                                               |                            |     | ±50                        | μΑ               |

| CLOCK OUTPUT (CLKOUT)                 |                                                 |                                                                                                                           |                            |     |                            |                  |

| Duty Cycle                            |                                                 | 5pF and 10kΩ to DGND                                                                                                      | 40                         | 50  | 60                         | %                |

| Rise Time                             |                                                 | 5pF and 10kΩ to DGND                                                                                                      |                            | 3   |                            | ns               |

| Fall Time                             |                                                 | 5pF and 10kΩ to DGND                                                                                                      |                            | 3   |                            | ns               |

| VIDEO CHARACTERISTICS                 |                                                 |                                                                                                                           |                            |     |                            |                  |

| DC Power-Supply Rejection             |                                                 | V <sub>AVDD</sub> = V <sub>DVDD</sub> = V <sub>PVDD</sub> = 5V;<br>V <sub>IN</sub> = 1V <sub>P-P</sub> , measured at VOUT |                            | 40  |                            | dB               |

| AC Power-Supply Rejection             |                                                 | VAVDD = VDVDD = VPVDD = 5V;<br>VIN = 1VP-P, measured at VOUT;<br>f = 5MHz; power-supply ripple = 0.2VP-P                  |                            | 30  |                            | dB               |

| Short-Circuit Current                 |                                                 | VOUT to PGND                                                                                                              |                            |     | 230                        | mA               |

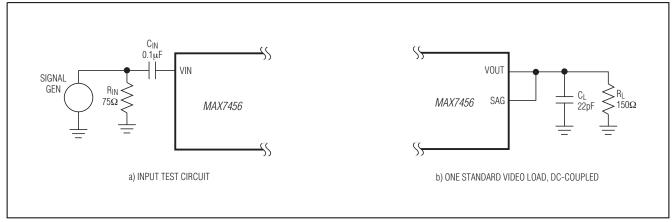

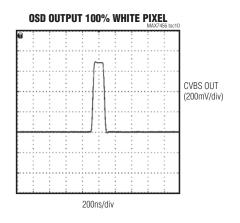

| Line-Time Distortion                  | LTD                                             | Figures 1a, 1b                                                                                                            |                            |     | 0.5                        | %                |

| Output Impedance                      | Z <sub>OUT</sub>                                | Figures 1a, 1b                                                                                                            |                            | 0.2 |                            | Ω                |

| Gain                                  |                                                 | Figures 1a, 1b                                                                                                            | 1.89                       | 2.0 | 2.11                       | V/V              |

| Black Level                           |                                                 | At VOUT, Figures 1a, 1b                                                                                                   |                            |     | AGND<br>+ 1.5              | V                |

| Input-Voltage Operating Range         | VIN                                             | Figures 1a, 3 (Note 2)                                                                                                    | 0.5                        |     | 1.2                        | V <sub>P-P</sub> |

| Input-Voltage Sync Detection<br>Range | V <sub>INSD</sub>                               | Figures 1a, 3 (Note 3)                                                                                                    | 0.5                        |     | 2.0                        | V <sub>P-P</sub> |

| Maximum Output-Voltage Swing          | aximum Output-Voltage Swing VOUT Figures 1a, 1b |                                                                                                                           | 2.4                        |     |                            | V <sub>P-P</sub> |

| Output-Voltage Sync Tip Level         |                                                 |                                                                                                                           |                            | 0.7 |                            | V                |

| Large Signal Bandwidth (0.2dB)        | BW                                              | V <sub>OUT</sub> = 2V <sub>P-P</sub> , Figures 1a, 1b                                                                     |                            | 6   |                            | MHz              |

| VIN to VOUT Delay                     |                                                 |                                                                                                                           |                            | 30  |                            | ns               |

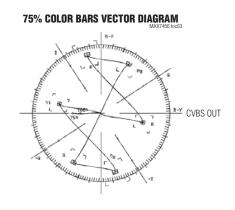

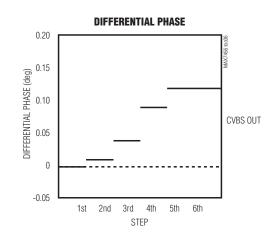

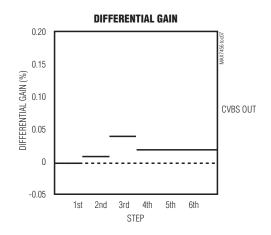

| Differential Gain                     | DG                                              |                                                                                                                           |                            | 0.5 |                            | %                |

| Differential Phase                    | DP                                              |                                                                                                                           |                            | 0.5 |                            | Degrees          |

| OSD White Level                       |                                                 | VOUT 100% white level with respect to black level 1.25 1.33 1.4                                                           |                            |     |                            | V                |

| Horizontal Pixel Jitter               |                                                 | Between consecutive horizontal lines                                                                                      |                            | 24  |                            | ns               |

| Video Clamp Settling Time             |                                                 |                                                                                                                           |                            | 32  |                            | Lines            |

# 集成了EEPROM的 单通道、单色随屏显示器

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = +4.75V \text{ to } +5.25V, V_{DVDD} = +4.75V \text{ to } +5.25V, V_{PVDD} = +4.75V \text{ to } +5.25V, T_A = T_{MIN} \text{ to } T_{MAX}.$  Typical values are at  $V_{AVDD} = V_{DVDD} = V_{PVDD} = +5V, T_A = +25^{\circ}C,$  unless otherwise noted.) (Note 1)

| PARAMETER                     | SYMBOL | SYMBOL CONDITIONS                                |    |    | MAX | UNITS |

|-------------------------------|--------|--------------------------------------------------|----|----|-----|-------|

| OSD CHARACTERISTICS           |        |                                                  |    |    |     |       |

| OSD Rise Time                 |        | OSD insertion mux register<br>OSDM[5,4,3] = 011b | 60 |    |     | ns    |

| OSD Fall Time                 |        | OSD insertion mux register<br>OSDM[5,4,3] = 011b |    | 60 |     | ns    |

| OSD Insertion Mux Switch Time |        | OSD insertion mux register<br>OSDM[2,1,0] = 011b |    | 75 |     | ns    |

#### **TIMING CHARACTERISTICS**

(VAVDD = +4.75V to +5.25V, VDVDD = +4.75V to +5.25V, VPVDD = +4.75V to +5.25V, TA = TMIN to TMAX. Typical values are at VAVDD =  $VDVDD = VDVDD = VDVDD = +5V, TA = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                             | SYMBOL           | CONDITIONS                            | MIN | TYP M | ΑX | UNITS |  |

|-------------------------------------------------------|------------------|---------------------------------------|-----|-------|----|-------|--|

| SPI TIMING                                            | '                |                                       |     |       |    | •     |  |

| SCLK Period                                           | tCP              |                                       | 100 |       |    | ns    |  |

| SCLK Pulse-Width High                                 | tсн              |                                       | 40  |       |    | ns    |  |

| SCLK Pulse-Width Low                                  | tCL              |                                       | 40  |       |    | ns    |  |

| CS Fall to SCLK Rise Setup                            | tcsso            |                                       | 30  |       |    | ns    |  |

| CS Fall After SCLK Rise Hold                          | tCSH0            |                                       | 0   |       |    | ns    |  |

| CS Rise to SCLK Setup                                 | tCSS1            |                                       | 30  |       |    | ns    |  |

| CS Rise After SCLK Hold                               | tCSH1            |                                       | 0   |       |    | ns    |  |

| CS Pulse-Width High                                   | tcsw             |                                       | 100 |       |    | ns    |  |

| SDIN to SCLK Setup                                    | t <sub>DS</sub>  |                                       | 30  |       |    | ns    |  |

| SDIN to SCLK Hold                                     | tDH              |                                       | 0   |       |    | ns    |  |

| SDOUT Valid Before SCLK                               | t <sub>DO1</sub> | 20pF to ground                        | 25  | 25    |    | ns    |  |

| SDOUT Valid After SCLK                                | t <sub>DO2</sub> | 20pF to ground                        | 0   | 0     |    | ns    |  |

| CS High to SDOUT High Impedance                       | t <sub>DO3</sub> | 20pF to ground                        | 300 |       |    | ns    |  |

| CS Low to SDOUT Logic Level                           | t <sub>DO4</sub> | 20pF to ground                        | 20  |       |    | ns    |  |

| HSYNC, VSYNC, AND LOS TIM                             | NG               |                                       |     |       |    |       |  |

| LOS, VSYNC, and HSYNC Valid before CLKOUT Rising Edge | t <sub>DOV</sub> | 20pF to ground 30                     |     |       | ns |       |  |

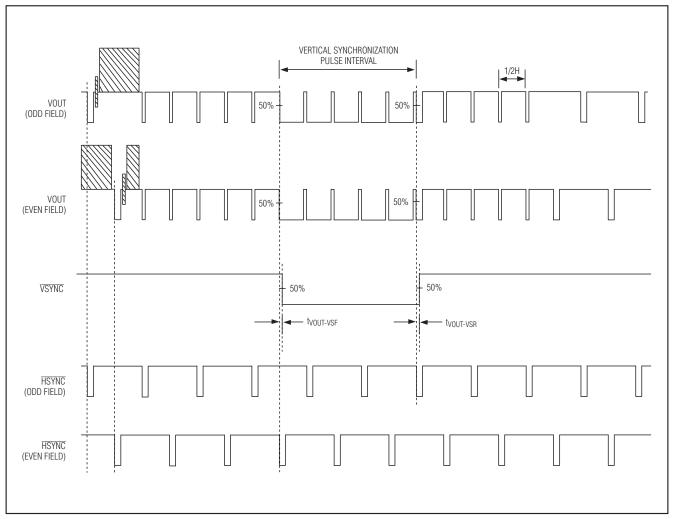

| VOUT Sync to VSYNC Falling                            | t                | NTSC external sync mode, Figure 4 375 |     |       |    | 10.5  |  |

| Edge Delay                                            | tvout-vsf        | PAL external sync mode, Figure 6      | 400 |       |    | ns    |  |

#### **TIMING CHARACTERISTICS (continued)**

$(V_{AVDD} = +4.75V \text{ to } +5.25V, V_{DVDD} = +4.75V \text{ to } +5.25V, V_{PVDD} = +4.75V \text{ to } +5.25V, T_A = T_{MIN} \text{ to } T_{MAX}.$  Typical values are at  $V_{AVDD} = V_{DVDD} = V_{PVDD} = +5V, T_A = +25^{\circ}C,$  unless otherwise noted.) (Note 1)

| PARAMETER                             | SYMBOL           | CONDITIONS                                | MIN | TYP | MAX | UNITS |  |

|---------------------------------------|------------------|-------------------------------------------|-----|-----|-----|-------|--|

| VOUT Sync to VSYNC Rising             | tuo              | NTSC external sync mode, Figure 4         |     | 400 |     | ns    |  |

| Edge Delay                            | tvout-vsr        | PAL external sync mode, Figure 6          |     | 425 |     | 115   |  |

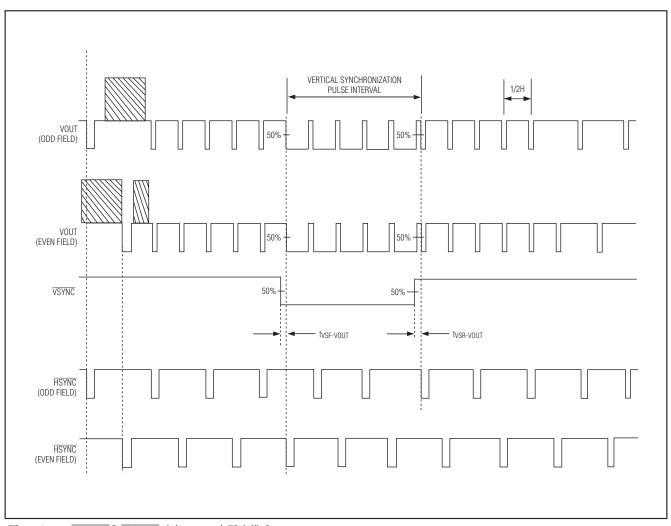

| VSYNC Falling Edge to VOUT            | t. (05. ) (01.17 | NTSC internal sync mode, Figure 5         |     | 40  |     | ns    |  |

| Sync Delay                            | tvsf-vout        | PAL internal sync mode, Figure 7          |     | 45  |     | 115   |  |

| VSYNC Rising Edge to VOUT             | t. (OD. ) (OUT   | NTSC internal sync mode, Figure 5         |     | 32  |     | ns    |  |

| Sync Delay                            | tvsr-vout        | PAL internal sync mode, Figure 7          | 30  |     |     | 118   |  |

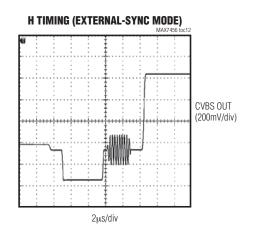

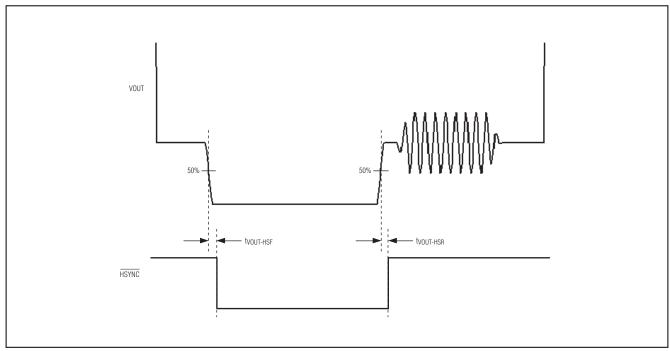

| VOUT Sync to HSYNC Falling Edge Delay | tvout-HSF        | NTSC and PAL external sync mode, Figure 8 | 310 |     |     | ns    |  |

| VOUT Sync to HSYNC Rising Edge Delay  | tvout-HSR        | NTSC and PAL external sync mode, Figure 8 |     | 325 |     | ns    |  |

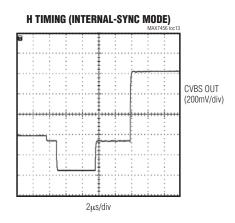

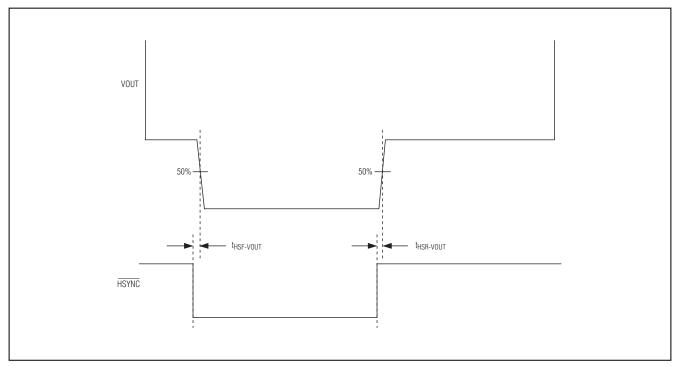

| HSYNC Falling Edge to VOUT Sync Delay | tHSF-VOUT        | NTSC and PAL internal sync mode, Figure 9 |     | 115 |     | ns    |  |

| HSYNC Rising Edge to VOUT Sync Delay  | tHSR-VOUT        | NTSC and PAL internal sync mode, Figure 9 |     | 115 |     | ns    |  |

| All Supplies High to CS Low           | tpup             | Power-up delay                            |     | 50  |     | ms    |  |

| NVM Write Busy                        | t <sub>NVW</sub> |                                           |     | 12  |     | ms    |  |

Note 1: See the standard test circuits of Figure 1. R<sub>L</sub> = 75Ω, unless otherwise specified. All digital input signals are timed from a voltage level of (V<sub>IH</sub> + V<sub>IL</sub>) / 2. All parameters are tested at T<sub>A</sub> = +85°C and values through temperature range are guaranteed by design.

Note 2: The input-voltage operating range is the input range over which the output signal parameters are guaranteed (Figure 3).

Note 3: The input-voltage sync detection range is the input composite video range over which an input sync signal is properly detected and the OSD signal appears at VOUT. However, the output voltage specifications are not guaranteed for input signals exceeding the maximum specified in the input operating voltage range (Figure 3).

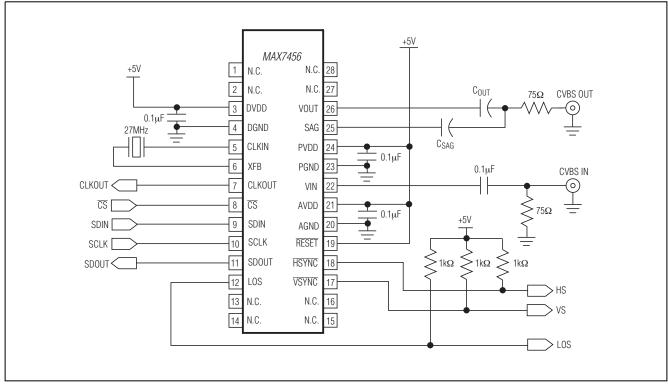

图1. 标准测试电路

# 集成了EEPROM的 单通道、单色随屏显示器

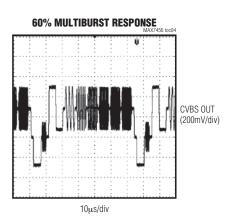

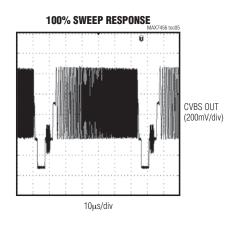

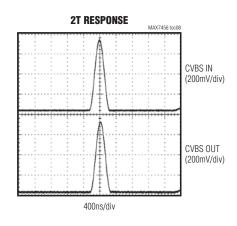

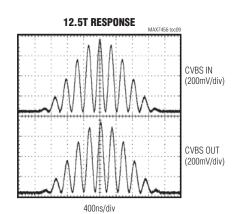

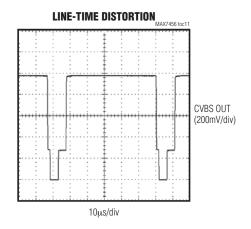

典型工作特性

(V<sub>AVDD</sub> = +5V, V<sub>DVDD</sub> = +5V, V<sub>PVDD</sub> = +5V, T<sub>A</sub> = +25°C, unless otherwise noted. See the *Typical Operating Circuit* of Figure 2, if applicable.)

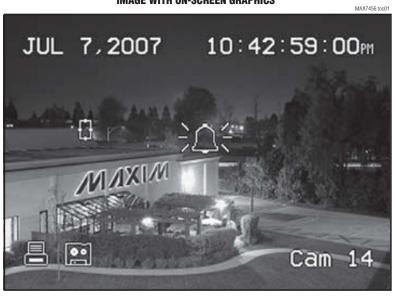

#### **IMAGE WITH ON-SCREEN GRAPHICS**

# 100% COLOR BARS RESPONSE MAX7456 tool2 CVBS OUT (200mV/div)

#### 典型工作特性(续)

(VAVDD = +5V, VDVDD = +5V, VPVDD = +5V, TA = +25°C, unless otherwise noted. See the Typical Operating Circuit of Figure 2, if applicable.)

# 集成了EEPROM的 单通道、单色随屏显示器

典型工作特性(续)

(VAVDD = +5V, VDVDD = +5V, VPVDD = +5V, TA = +25°C, unless otherwise noted. See the *Typical Operating Circuit* of Figure 2, if applicable.)

# 集成了EEPROM的 单通道、单色随屏显示器

#### 引脚说明

| 引脚                     | 名称     | 功能                                                                                                                                           |

|------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 13–16,<br>27, 28 | N.C.   | 不连接。内部未连接。                                                                                                                                   |

| 3                      | DVDD   | 数字电源输入,用一个0.1μF电容旁路至DGND。                                                                                                                    |

| 4                      | DGND   | 数字地。                                                                                                                                         |

| 5                      | CLKIN  | 晶体连接1。在CLKIN和XFB之间连接一个并联谐振、基频模式晶体构成晶体振荡器,或使用27MHz系统<br>参考时钟直接驱动CLKIN。                                                                        |

| 6                      | XFB    | 晶体连接2。在CLKIN和XFB之间连接一个并联谐振、基频模式晶体构成晶体振荡器,如果使用27MHz<br>系统参考时钟驱动CLKIN,将XFB悬空。                                                                  |

| 7                      | CLKOUT | 时钟输出。27MHz逻辑电平输出的系统时钟。                                                                                                                       |

| 8                      | CS     | 低电平有效片选输人。当 $\overline{\text{CS}}$ 为高电平时, $\overline{\text{SDOUT}}$ 变为高阻抗。                                                                   |

| 9                      | SDIN   | 串行数据输入。数据在SCLK上升沿移人。                                                                                                                         |

| 10                     | SCLK   | 串行时钟输入。为数据输入到SDIN和从SDOUT输出提供时钟,占空比必须在40%至60%之间。                                                                                              |

| 11                     | SDOUT  | 串行数据输出。数据在SCLK下降沿输出。当 <del>CS</del> 为高电平时,变为高阻抗。                                                                                             |

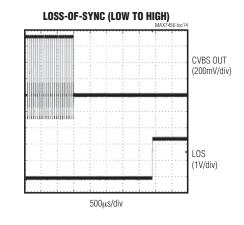

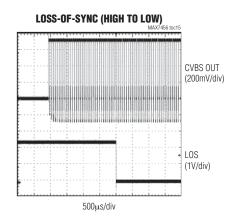

| 12                     | LOS    | 同步丢失输出(开漏)。当VIN同步脉冲丢失32个连续周期时,LOS变为高电平。当接收到32个连续有效同步脉冲时,LOS变为低电平。通过1kΩ上拉电阻连接至DVDD或另一个符合接收器件的电源正极。                                            |

| 17                     | VSYNC  | 场同步输出(开漏)。视频输入场同步期间, $\overline{VSYNC}$ 变为低电平。 $\overline{VSYNC}$ 可以从 $VIN$ 恢复,也可以在内同步模式下内部产生。通过 $1k\Omega$ 上拉电阻连接至 $DVDD$ 或者另一个符合接收器件的电源正极。 |

| 18                     | HSYNC  | 行同步输出(开漏)。视频输入行同步期间, <del>HSYNC</del> 变为低电平。 <del>HSYNC</del> 可以从VIN恢复,也可以在内同步模式下内部产生。通过1kΩ上拉电阻连接至DVDD或另一个符合接收器件的电源正极。                       |

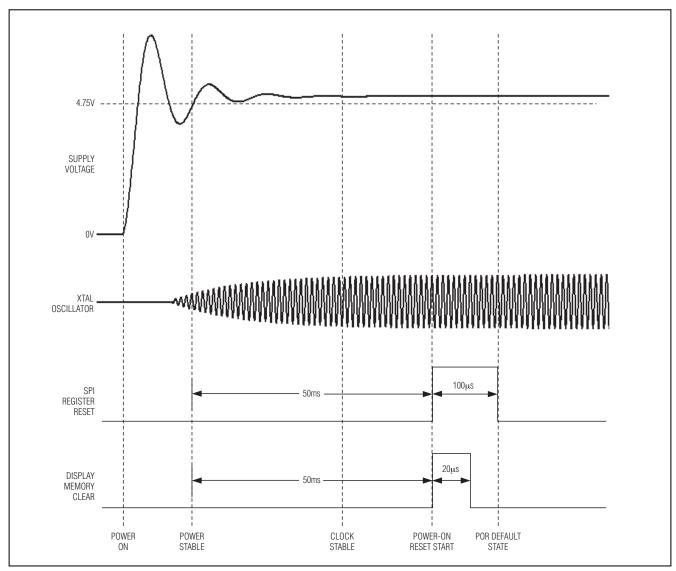

| 19                     | RESET  | 系统复位输入。最小RESET脉冲宽度为50ms。RESET上升沿100μs后,所有SPI寄存器被复位至默认值。在此期间,不能对寄存器进行读写访问。RESET上升沿20μs后,显示存储器所有位置都被复位至默认值00H。                                 |

| 20                     | AGND   | 模拟地。                                                                                                                                         |

| 21                     | AVDD   | 模拟电源输入,用一个0.1μF电容旁路至AGND。                                                                                                                    |

| 22                     | VIN    | PAL或者NTSC CVBS视频输入。                                                                                                                          |

| 23                     | PGND   | 驱动器地,在一个点连接至AGND。                                                                                                                            |

| 24                     | PVDD   | 驱动器电源输入,用一个 $0.1\mu$ F电容旁路至PGND。                                                                                                             |

| 25                     | SAG    | 电压衰减修正输入,如果不使用须连接至VOUT,参考图1b。                                                                                                                |

| 26                     | VOUT   | 视频输出。                                                                                                                                        |

| _                      | EP     | 裸焊盘。内部连接至AGND。将EP连接至AGND层以提高散热性能。不要将EP用作唯一的地连接。                                                                                              |

## 集成了EEPROM的 单通道、单色随屏显示器

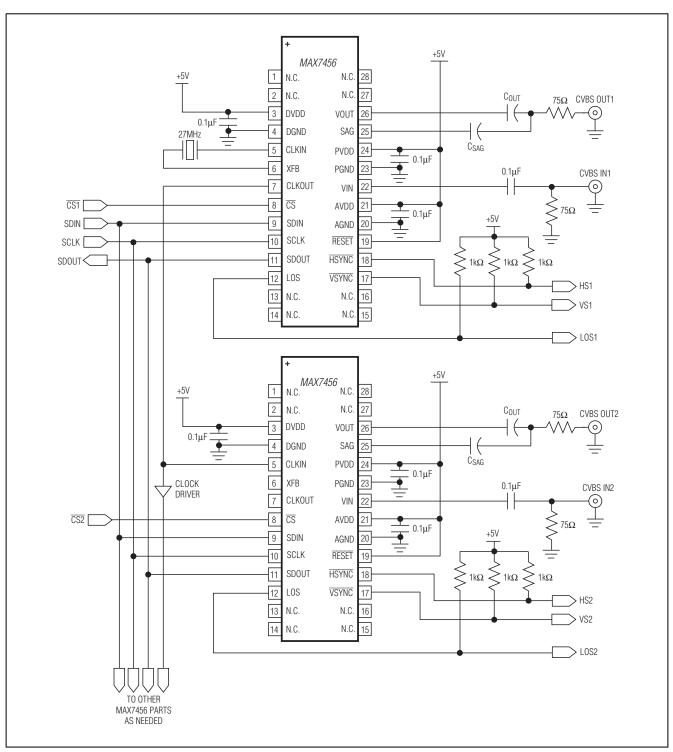

图2. 典型工作电路

#### 详细说明

MAX7456单通道单色随屏显示(OSD)发生器集成了产生用户定义的OSD并加载到输出信号所需的全部功能。MAX7456能够接收NTSC或者PAL复合视频信号。器件包括输入钳位、同步分离器、视频时序发生器、OSD插入复用器、非易失字符存储器、显示存储器、OSD发生器、晶体振荡器以及读/写OSD数据的SPI兼容接口和视频驱动器等(请参考简化功能框图)。此外,MAX7456还为系统同步提供场同步(VSYNC)、行同步(HSYNC)和同步丢失(LOS)输出信号。时钟输出信号(CLKOUT)支持多个器件的菊型链接。

请参考*MAX7456寄存器说明*部分,了解本数据资料中使用的寄存器符号。

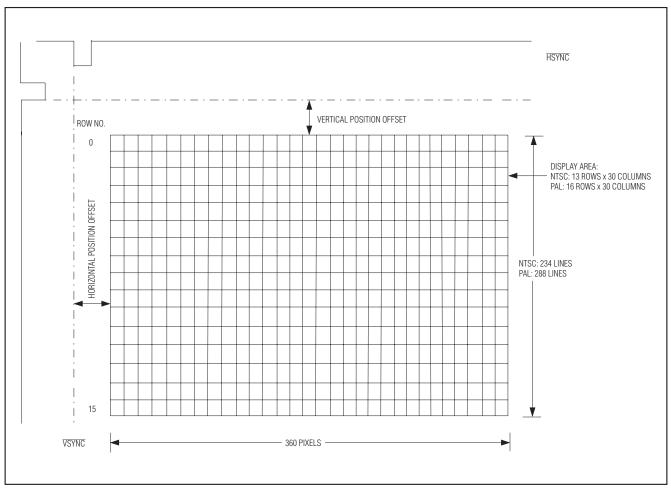

256个用户定义12 x 18象素字符组具有预装人,并与输入视频流复合,产生带有OSD视频输出的CVBS信号。在NVM中,最多可以重设256个12 x 18象素字符。在NTSC制式中,显示13行 x 30个字符。在PAL制式中,显示16行 x 30个字符。没有输入视频信号时,使用MAX7456的内部视频时序发生器,仍然可以显示OSD图像。

#### 视频输入

MAX7456的VIN可接收标准NTSC或者PAL CVBS信号。必须用一个 $0.1\mu$ F电容对视频信号输入进行交流耦合,并在内部钳位。需要 $0.1\mu$ F输入耦合电容确保规定的线时间失真(LTD)和视频钳位稳定时间。视频钳位稳定时间随输入耦合电容同比例变化,而LTD随电容反比例变化。

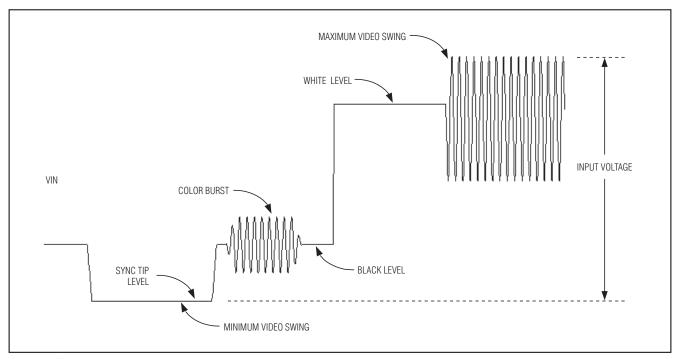

图3. 术语定义

#### 输入钳位

MAX7456的钳位是直流重建电路,在逐行基础上,使用输入耦合电容校正输入信号的直流偏移,将VIN的同步头钳位在约550mV。在VIN端建立的直流电平可用于片内同步检测和视频处理功能。该电路还消除了低频噪声,例如60Hz杂音或其它加入的低频噪声。

#### 同步分离器

同步分离器检测视频输入的复合同步脉冲,提取出时序信息,产生HSYNC和VSYNC信号;还用于内部OSD同步和同步丢失(LOS)检测。如果在VIN上32条连续行周期没有探测到同步信号,LOS变为高电平,如果探测到32个连续行同步信号,则变为低电平。在LOS状态期间,当VM0[5] = 0 (视频模式0寄存器,第5位)时,只有OSD出现在VOUT上。此时,输入图像在VOUT被设置为由VM1[6:4]确定的灰度级。表1列出了所有同步模式。

#### 表1. 视频同步模式

| VIDEO MODE            | VIN      | VSYNC           | HSYNC           | LOS  | VOUT                  |

|-----------------------|----------|-----------------|-----------------|------|-----------------------|

| Auto Sync Select Mode | Video    | Active          | Active          | Low  | V <sub>IN</sub> + OSD |

| VM0[5, 4] = 0x        | No input | Active          | Active          | High | OSD only              |

| External Sync Select  | Video    | Active          | Active          | Low  | V <sub>IN</sub> + OSD |

| VM0[5, 4] = 10        | No input | Inactive (high) | Inactive (high) | High | DC                    |

| Internal Sync Select  | Video    | Active          | Active          | High | OSD only              |

| VM0[5, 4] = 11        | No input | Active          | Active          | High | OSD only              |

$X = \mathcal{X} \neq \mathcal{X}$

## 集成了EEPROM的 单通道、单色随屏显示器

#### 视频时序发生器

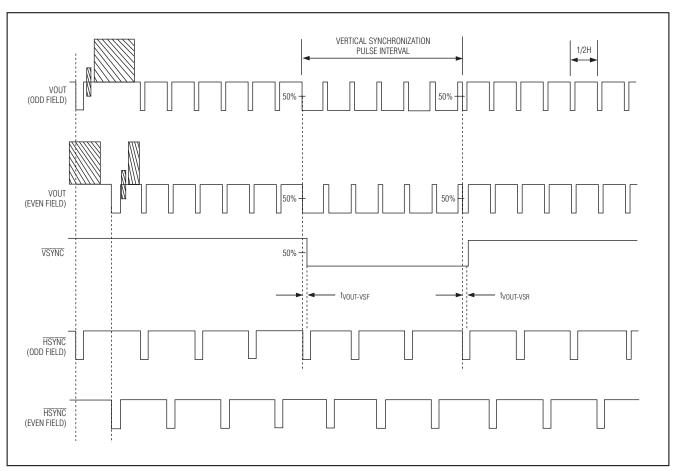

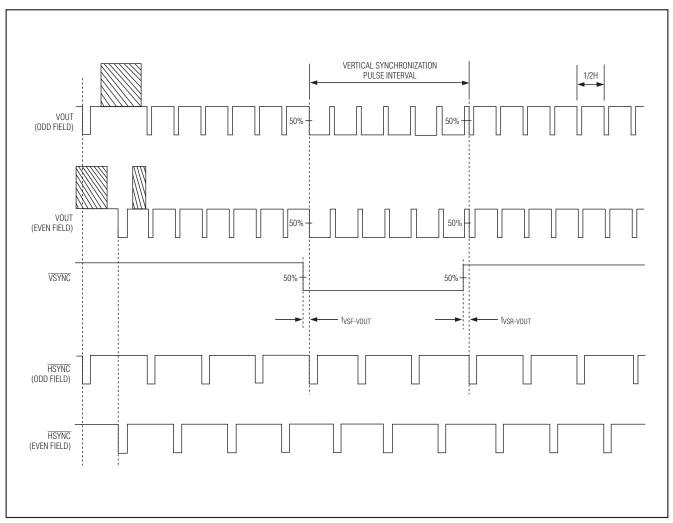

视频时序发生器是数字电路,产生所有的内部和外部 (VSYNC和HSYNC)时序信号。VSYNC和HSYNC可以和 VIN同步,或在内部同步模式下独立于输入运行。视频时序发生器能够使用同一个27MHz晶体产生NTSC或者PAL 时序(请参考图4至图9)。

#### 晶体振荡器

内部晶体振荡器产生视频时序发生器使用的系统时钟。振荡器使用一个27MHz晶体,也可以由CLKIN端外部27MHz TTL时钟驱动。外部时钟模式下,在CLKIN端连接一个 27MHz TTL输入时钟,XFB端悬空。

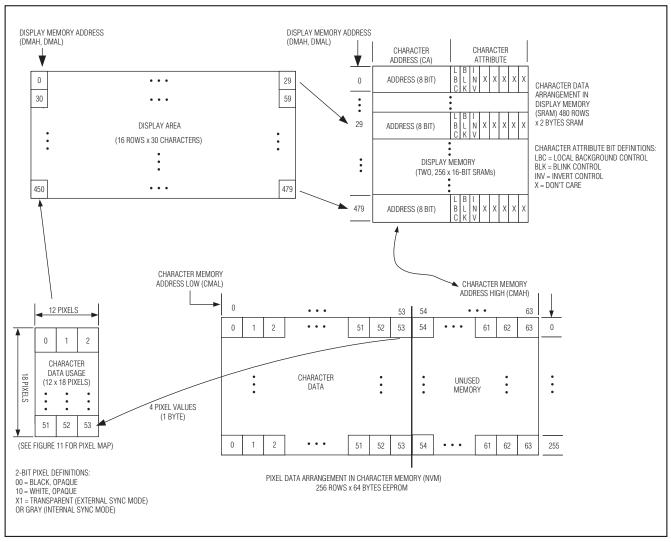

#### 显示存储器(SRAM)

显示存储器存储了480个字符地址,这些地址指向存储在NVM字符存储器中的字符。用户可以通过SPI兼容串口设置显示存储器的内容。显示存储器地址对应于监视器的固定位置(参考图10)。在场消隐期间写人显示存储器,可防止OSD图像的瞬时变暗。可将VSYNC作为主机处理器中断,启动写人显示存储器操作,以实现上述功能。

图4. VOUT、VSYNC和HSYNC时序(NTSC,外同步模式)

图5. VOUT、VSYNC和HSYNC时序(NTSC,内同步模式)

# 集成了EEPROM的 单通道、单色随屏显示器

图6. VOUT、VSYNC和HSYNC时序(PAL,外同步模式)

图7. VOUT、VSYNC和HSYNC时序(PAL,内同步模式)

# 集成了EEPROM的 单通道、单色随屏显示器

图8. VOUT和HSYNC行同步时序(NTSC和PAL,外同步模式)

图9. VOUT和HSYNC行同步时序(NTSC和PAL,内同步模式)

## 集成了EEPROM的 单通道、单色随屏显示器

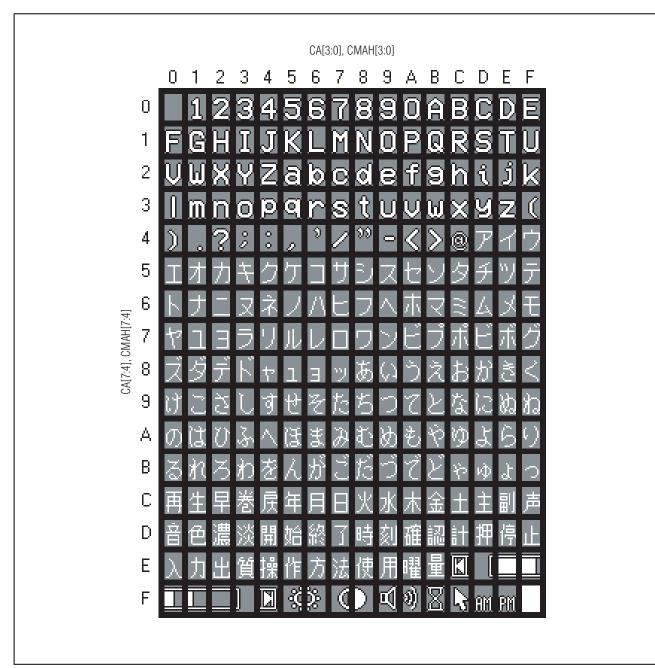

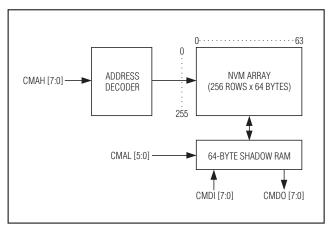

#### 字符存储器(NVM)

字符存储器是256行 x 64字节宽非易失存储器(NVM),存储字符或者图形,在工厂中预装人了图12所示的字符。用户可通过SPI兼容串口设置字符存储器中的内容。每一行都包含一个OSD字符的描述。每一字符由12个行 x 18 列象素组成,每个象素点由具有三种状态的2位数据表示,三种状态为:白色、黑色或者透明。因此,每个字符需要54字节的象素数据(图11)。

NVM需要一次读写所有字符(64字节),通过被称为镜像RAM的存储器行实现。64字节临时镜像RAM包含有所选字符(CMAH[7:0])的所有象素数据,用作NVM读写操作的缓冲(图13)。总是通过镜像RAM访问NVM,所以需要两个操作步骤。向NVM写人字符时,用户首先利用54个8位SPI写操作写人镜像RAM,然后执行一条镜像RAM写命令。类似的,读取一个字符的象素时,先将字符的象素数据读入镜像RAM,再从镜像RAM将所需的象素数据读至SPI端口。

图10. 各种参数定义

# 集成了EEPROM的 单通道、单色随屏显示器

|                  | PIXEL COLUMN NUMBER |                |                |                          |        |        |        |        |        |        | OUADACTED MEMODY |        |                                        |

|------------------|---------------------|----------------|----------------|--------------------------|--------|--------|--------|--------|--------|--------|------------------|--------|----------------------------------------|

|                  | 0                   | 1              | 2              | 3                        | 4      | 5      | 6      | 7      | 8      | 9      | 10               | 11     | CHARACTER MEMORY ADDRESS LOW CMAL[5:0] |

| 0                | CDMI<br>[7, 6]      | CDMI<br>[5, 4] | CDMI<br>[3, 2] | CDMI<br>[1, 0]           | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 0, 1, 2                                |

| 1                | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 3, 4, 5                                |

| 2                | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 6, 7, 8                                |

| 3                | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 9, 10, 11                              |

| 4                | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 12, 13, 14                             |

| 5                | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 15, 16, 17                             |

| 6                | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 18, 19, 20                             |

| 7                | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 21, 22, 23                             |

| 8 8EB            | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 24, 25, 26                             |

| PIXEL ROW NUMBER | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 27, 28, 29                             |

| ₩ 10             | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 30, 31, 32                             |

| 11               | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 33, 34, 35                             |

| 12               | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 36, 37, 38                             |

| 13               | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 39, 40, 41                             |

| 14               | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 42, 43, 44                             |

| 15               | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 45, 46, 47                             |

| 16               | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 48, 49, 50                             |

| 17               | [7, 6]              | [5, 4]         | [3, 2]         | [1, 0]                   | [7, 6] | [5, 4] | [3, 2] | [1, 0] | [7, 6] | [5, 4] | [3, 2]           | [1, 0] | 51, 52, 53                             |

|                  | 2-BIT PIXE          | L DEFINITIO    | N:             |                          |        |        |        |        |        |        |                  |        |                                        |

|                  | [x, y]              | 00 = BLAC      | K              |                          |        |        |        |        |        |        |                  |        |                                        |

|                  | [x, y]              | 10 = WHIT      | E              |                          |        |        |        |        |        |        |                  |        |                                        |

|                  | [x, y]              |                | RAY (INTERI    | EXTERNAL :<br>NAL SYNC N |        | E)     |        |        |        |        |                  |        |                                        |

|                  | 多丰咖食                |                |                |                          |        |        |        |        |        |        |                  |        |                                        |

图11. 字符数据使用(象素映射)

图12. 字符地址映射(默认字符集)

## 集成了EEPROM的 单通道、单色随屏显示器

图13. NVM结构

#### 随屏显示(OSD)发生器

OSD发生器根据字符存储器和行亮度寄存器(RB0-RB15)的内容,设置每一象素的亮度。

#### OSD插入复用器

OSD插入复用器在OSD象素和输入视频信号之间进行选择。OSD图像锐度由OSD插入复用器(OSDM)寄存器中的OSD上升和下降时间位以及OSD插入复用器开关时间位控制。该寄存器控制OSD图像锐度和色彩串扰/亮度串扰之间的均衡。减小时间设置可锐化象素,但是有可能增强色彩串扰/亮度串扰。最优设置取决于实际应用的需求,因此,可由用户设置。

#### 视频输出驱动器

MAX7456包含增益为2倍的视频输出驱动器。驱动器最大输出摆幅为2.4V<sub>P-P</sub>,信号带宽高达6MHz(衰减小于等于0.2dB)。驱动器输出可驱动两个150Ω标准视频负载。

#### 电压衰减修正

通过电压衰减修正能够降低输出耦合电容的电路要求和物理尺寸,并将线时失真降到可接受的水平。电压衰减修正对具有对150Ω背向匹配电阻的同轴电缆和输出耦合电容组成的高通滤波器进行低频补偿。该电路的截止点

必须足够低至能通过场同步间隔(PAL小于25Hz,NTSC小于30Hz),以避免场倾斜。传统上,截止点小于5Hz,耦合电容必须非常大,典型为大于330μF。MAX7456降低了该电容值,并用两个较小的电容(C<sub>OUT</sub>和C<sub>SAG</sub>)替代,有效降低了耦合电容的成本和体积,同时获得了可接受的线时失真(表2)。如果不使用,将SAG连接至VOUT。

#### 表2. SAG修正电容值

| C <sub>OUT</sub> (µF) | C <sub>SAG</sub> (μF) | LINE-TIME DISTORTION<br>(% typ) |

|-----------------------|-----------------------|---------------------------------|

| 470                   | _                     | 0.2                             |

| 100                   | _                     | 0.4                             |

| 100                   | 22                    | 0.3                             |

| 47                    | 47                    | 0.3                             |

| 22                    | 22                    | 0.4                             |

| 10                    | 10                    | 0.6                             |

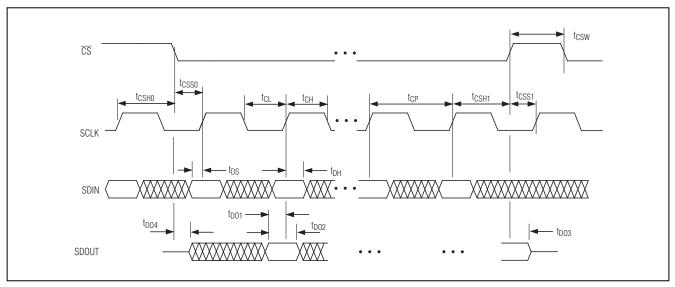

#### 串行接口

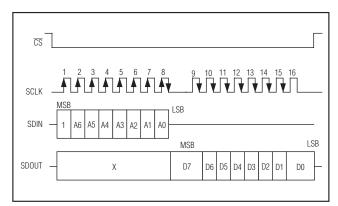

SPI兼容串口设置工作模式和OSD数据。读功能支持写校验和读取状态(STAT)、显示存储器数据输出(DMDO)和字符存储器数据输出(CMDO)寄存器。

#### 读写操作

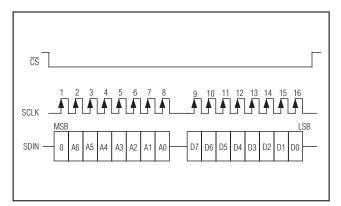

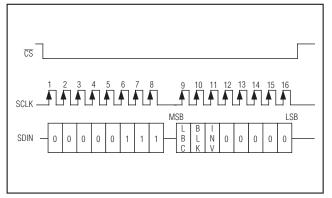

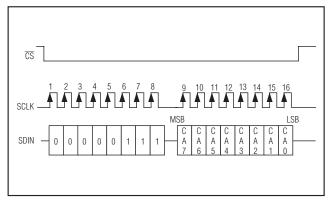

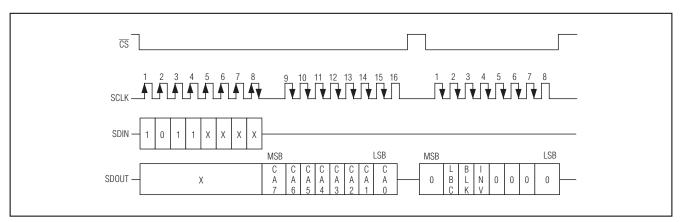

MAX7456支持高达10MHz的接口时钟(SCLK)。图15所示为数据写人,图16为从MAX7456读取数据。拉低 $\overline{CS}$ 使能串口。在SCLK上升沿数据输入SDIN。当 $\overline{CS}$ 变为高电平时,数据被锁存至输入寄存器。如果 $\overline{CS}$ 在传输中间变为高电平,则本次操作失败(即,数据没有被写入到寄存器中)。 $\overline{CS}$ 变为低电平后,器件等待第一个输入到SDIN中的字节,以确定所执行数据传输的类型。

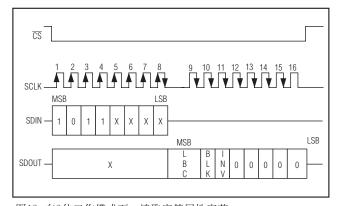

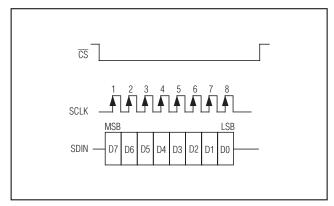

SPI命令为16位长,高8位(MSB)代表寄存器地址,低8位(LSB)代表数据(图15和图16)。这种配置有两个例外情况:

- 1)显示存储器访问所使用的自动递增写人模式是一个8位操作(图21)。当执行显示存储器自动递增写人操作时,8位地址是内部产生的,串口只需要8位数据。

- 2) 在16位工作模式时,从显示存储器读取字符数据是24位操作(8位地址以及16位数据),参考图20。

图14. 串口时序详述

图15. 写操作

图17. 在8位工作模式下,写入字符属性字节

图16. 读操作

图18. 在8位工作模式下,读取字符属性字节

## 集成了EEPROM的 单通道、单色随屏显示器

图19. 在8位和16位工作模式下,写入字符地址字节

图20. 在16位工作模式下, 读取字符地址和字符属性字节

图21. 自动递增模式下的写操作

#### 复位 上电复位

MAX7456的上电复位电路(POR)提供一个内部复位信号,在电源电压稳定后开始工作。内部复位信号将所有寄存器复位至默认值,清除显示存储器。寄存器复位过程需要100µs,为避免出现不期望的结果,在这期间不允许进行读/写操作。一般在供电电压稳定,并且27MHz时钟信号稳定50ms后,显示存储器复位,OSD使能。用户在这段时间中应避免SPI操作,以防止出现不期望的结果。50ms (典型值)后,可查询STAT[6]确认复位时序是否完成(图22)。

## 集成了EEPROM的 单通道、单色随屏显示器

图22. 上电复位顺序

#### 软件复位

MAX7456具有一个软件复位位(VM0[1]), 当该位被置为高电平时,显示存储器被清除,除了OSD黑电平寄存器 (OSDBL),所有的寄存器复位为默认值。100μs (典型值)后,可查询STAT[6]确认复位过程是否完成。

#### 硬件复位

MAX7456提供一个硬件复位输入(RESET),其功能和POR相同。当RESET被驱动至低电平时,所有寄存器复位至默认值,不能进行读/写操作。建立复位过程需要 $\geq$ 50ms宽的RESET脉冲,在这期间不允许其他操作。RESET上升沿100 $\mu$ s后,所有SPI寄存器被复位至默认值。RESET上升沿20 $\mu$ s后,显示存储器的所有位置都被复位至默认值00H。RESET优先级高于软件复位位。RESET完毕后,可查询STAT[6]确认复位序列是否完成。

## 集成了EEPROM的 单通道、单色随屏显示器

MAX7456寄存器说明

通过表3列出了所有的SPI寄存器来访问MAX7456操作,包括显示存储器和字符存储器访问等。通过SPI端口不能直接访问显示和字符存储器。请参考应用信息部分,了解对访问存储器所需的SPI操作步骤说明。

本数据资料采用的寄存器格式为REGISTER\_NAME [BIT\_NUMBERS]。例如,视频模式0寄存器的第1位表述为VM0[1]。

#### 表3. 寄存器映射

| WRITE<br>ADDRESS | READ<br>ADDRESS | REGISTER<br>NAME | REGISTER<br>DESCRIPTION       |  |

|------------------|-----------------|------------------|-------------------------------|--|

| 00H              | 80H             | VMO              | Video Mode 0                  |  |

| 01H              | 81H             | VM1              | Video Mode 1                  |  |

| 02H              | 82H             | HOS              | Horizontal Offset             |  |

| 03H              | 83H             | VOS              | Vertical Offset               |  |

| 04H              | 84H             | DMM              | Display Memory Mode           |  |

| 05H              | 85H             | DMAH             | Display Memory Address High   |  |

| 06H              | 86H             | DMAL             | Display Memory Address Low    |  |

| 07H              | 87H             | DMDI             | Display Memory Data In        |  |

| 08H              | 88H             | CMM              | Character Memory Mode         |  |

| 09H              | 89H             | CMAH             | Character Memory Address High |  |

| 0AH              | 8AH             | CMAL             | Character Memory Address Low  |  |

| 0BH              | 8BH             | CMDI             | Character Memory Data In      |  |

| 0CH              | 8CH             | OSDM             | OSD Insertion Mux             |  |

| 10H              | 90H             | RB0              | Row 0 Brightness              |  |

| 11H              | 91H             | RB1              | Row 1 Brightness              |  |

| 12H              | 92H             | RB2              | Row 2 Brightness              |  |

| 13H              | 93H             | RB3              | Row 3 Brightness              |  |

| 14H              | 94H             | RB4              | Row 4 Brightness              |  |

| 15H              | 95H             | RB5              | Row 5 Brightness              |  |

| 16H              | 96H             | RB6              | Row 6 Brightness              |  |

| 17H              | 97H             | RB7              | Row 7 Brightness              |  |

| 18H              | 98H             | RB8              | Row 8 Brightness              |  |

| 19H              | 99H             | RB9              | Row 9 Brightness              |  |

| 1AH              | 9AH             | RB10             | Row 10 Brightness             |  |

| 1BH              | 9BH             | RB11             | Row 11 Brightness             |  |

| 1CH              | 9CH             | RB12             | Row 12 Brightness             |  |

| 1DH              | 9DH             | RB13             | Row 13 Brightness             |  |

| 1EH              | 9EH             | RB14             | Row 14 Brightness             |  |

| 1FH              | 9FH             | RB15             | Row 15 Brightness             |  |

| 6CH              | ECH             | OSDBL            | OSD Black Level               |  |

| _                | AxH             | STAT             | Status                        |  |

|                  | BxH             | DMDO             | Display Memory Data Out       |  |

| _                | CxH             | CMDO             | Character Memory Data Out     |  |

X = 无关。

视频模式0寄存器(VM0)

1) STAT[5] = 0, 字符存储器(NVM)不忙。

写地址 = 00H, 读地址 = 80H。

2) DMM[2] = 0,显示存储器(SRAM)没有处于被清除的过程中。

读/写访问:无限制。

写入该寄存器时,必须满足以下条件:

| BIT  | DEFAULT | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | 0       | Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6    | 0       | Video Standard Select 0 = NTSC 1 = PAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5, 4 | 00      | Sync Select Mode (Table 1)  0x = Autosync select (external sync when LOS = 0 and internal sync when LOS = 1)  10 = External  11 = Internal                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3    | 0       | Enable Display of OSD Image 0 = Off 1 = On                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2    | 0       | Vertical Synchronization of On-Screen Data 0 = Enable on-screen display immediately 1 = Enable on-screen display at the next VSYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1    | 0       | Software Reset Bit When this bit is set, all registers are set to their default values and the display memory is cleared. When a stable 27MHz clock is present, this bit is automatically cleared internally after typically 100µs. The user does not need to write a 0 afterwards. SPI operations should not be performed during this time or unpredictable results may occur. The status of the bit can be checked by reading this register after typically 100µs. This register is not accessible for writing until the display memory clear operation is finished (typically 20µs). |

| 0    | 0       | Video Buffer Enable 0 = Enable 1 = Disable (VOUT is high impedance)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

X =无关。

# 集成了EEPROM的 单通道、单色随屏显示器

#### 视频模式1寄存器(VM1)

写地址 = 01H, 读地址 = 81H。

读/写访问:无限制。

| BIT     | DEFAULT | FUNCTION                                                                                                                                                                                                                                                                                                                                                                 |

|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | 0       | Background Mode (See Table 4)  0 = The Local Background Control bit (see DMM[5] and DMDI[7]) sets the state of each character background.  1 = Sets all displayed background pixels to gray. The gray level is specified by bits VM1[6:4] below. This bit overrides the local background control bit.  Note: In internal sync mode, the background mode bit is set to 1. |

| 6, 5, 4 | 100     | Background Mode Brightness (% of OSD White Level)  000 = 0%  001 = 7%  010 = 14%  011 = 21%  100 = 28%  101 = 35%  110 = 42%  111 = 49%                                                                                                                                                                                                                                  |

| 3, 2    | 01      | Blinking Time (BT) 00 = 2 fields (33ms in NTSC mode, 40ms in PAL mode) 01 = 4 fields (67ms in NTSC mode, 80ms in PAL mode) 10 = 6 fields (100ms in NTSC mode, 120ms in PAL mode) 11 = 8 fields (133ms in NTSC mode, 160ms in PAL mode)                                                                                                                                   |

| 1, 0    | 11      | Blinking Duty Cycle (On : Off)  00 = BT : BT  01 = BT : (2 x BT)  10 = BT : (3 x BT)  11 = (3 x BT) : BT                                                                                                                                                                                                                                                                 |

#### 水平位置寄存器(HOS)

写地址 = 02H, 读地址 = 82H。 读/写访问: 无限制(图23)。

| BIT  | DEFAULT | FUNCTION                                                                                                                                                                                                 |

|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 6 | 00      | Don't Care                                                                                                                                                                                               |

| 5–0  | 10 0000 | Horizontal Position Offset (OSD video is not inserted into the horizontal blanking interval) 00 0000 = Farthest left (-32 pixels)  10 0000 = No horizontal offset  11 1111 = Farthest right (+31 pixels) |

#### 垂直位置寄存器(VOS)

写地址 = 03H, 读地址 = 83H。 读/写访问: 无限制(图23)。

| BIT     | DEFAULT | FUNCTION                                                                                                                                                                                            |

|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 6, 5 | 000     | Don't Care                                                                                                                                                                                          |

| 4-0     | 1 0000  | Vertical Position Offset (OSD video can be vertically shifted into the vertical blanking lines) 0 0000 = Farthest up (+16 pixels)  1 0000 = No vertical offset  1 1111 = Farthest down (-15 pixels) |

图23. 字符显示区

# 集成了EEPROM的 单通道、单色随屏显示器

显示存储器模式寄存器(DMM)

写入该寄存器时,必须满足以下条件:

写地址 = 04H, 读地址 = 84H。

DMM[2] = 0,显示存储器没有处于清除过程。

读/写访问:无限制。

| BIT | DEFAULT | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | 0       | Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6   | 0       | Operation Mode Selection  0 = 16-bit operation mode The 16-bit operation mode increases the speed at which the display memory can be updated. When writing to the display memory, the attribute byte is not entered through the SPI-compatible interface. It is entered automatically by copying DMM[5:3] to a character's attribute byte when a new character is written, thus reducing the number of SPI write operations per character from two to one (Figure 19). When in this mode, all characters written to the display memory have the same attribute byte. This mode is useful because successive characters commonly have the same attribute. This mode is distinct from the 8-bit operation mode where a character attribute byte must be written each time a character address byte is written to the display memory (see Table 5). When reading data from the display memory, both the Character Address byte and Character Attribute byte are transferred with the SPI-compatible interface (Figure 18).  1 = 8-bit operation mode |

|     |         | The 8-bit operation mode provides maximum flexibility when writing characters to the display memory. This mode enables writing individual Character Attribute bytes for each character (see Table 5). When writing to the display memory, DMAH[1] = 0 directs the data to the Character Address byte and DMAH[1] = 1 directs the Character Attributes byte to the data. This mode is distinct from the 16-bit operation mode where the attribute bits are automatically copied from DMM[5:3] when a character is written.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5   | 0       | Local Background Control Bit, LBC (see Table 4)  Applies to characters written in 16-bit operating mode.  0 = Sets the background pixels of the character to the video input (VIN) when in external sync mode.  1 = Sets the background pixels of the character to the background mode brightness level defined by VM1[6:4] in external or internal sync mode.  Note: In internal sync mode, the local background control bit behaves as if it is set to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4   | 0       | Blink Bit, BLK Applies to characters written in 16-bit operating mode.  0 = Blinking off 1 = Blinking on  Note: Blinking rate and blinking duty cycle data in the Video Mode 1 (VM1) register are used for blinking control.  In external sync mode: when the character is not displayed, VIN is displayed.  In internal sync mode: when the character is not displayed, background mode brightness is displayed (see VM1[6:4]).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3   | 0       | Invert Bit, INV Applies to characters written in 16-bit operating mode (see Figure 24).  0 = Normal (white pixels display white, black pixels display black)  1 = Invert (white pixels display black, black pixels display white)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### 显示存储器模式寄存器(DMM) (续)

| BIT | DEFAULT | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | 0       | Clear Display Memory  0 = Inactive  1 = Clear (fill all display memories with zeros)  Note: This bit is automatically cleared after the operation is completed (the operation requires 20µs). The user does not need to write a 0 afterwards. The status of the bit can be checked by reading this register.  This operation is automatically performed:  a) On power-up  b) Immediately following the rising edge of RESET  c) Immediately following the rising edge of CS after VM0[1] has been set to 1                                                                                                                                                                                                                                                                     |

| 1   | 0       | Vertical Sync Clear  Valid only when clear display memory = 1, (DMM[2] = 1)  0 = Immediately applies the clear display-memory command, DMM[2] = 1  1 = Applies the clear display-memory command, DMM[2] = 1, at the next VSYNC time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0   | 0       | Auto-Increment Mode Auto-increment mode increases the speed at which the display memory can be written by automatically incrementing the character address for each successive character written. This mode reduces the number of SPI commands, and thus the time needed to write a string of adjacent characters. This mode is useful when writing strings of characters written from left-to-right, top-to-bottom, on the display (see Table 5).  0 = Disabled 1 = Enabled When this bit is enabled for the first time, data in the Display Memory Address (DMAH[0] and DMAL[7:0]) registers are used as the starting location to which the data is written. When performing the auto-increment write for the display memory, the 8-bit address is internally generated, and |

|     |         | therefore only 8-bit data is required by the SPI-compatible interface (Figure 21). The content is to be interpreted as a Character Address byte if DMAH[1] = 0 or a Character Attribute byte if DMAH[1] = 1. This mode is disabled by writing the escape character 1111 1111. If the Clear Display Memory bit is set, this bit is reset internally.                                                                                                                                                                                                                                                                                                                                                                                                                            |

# 集成了EEPROM的 单通道、单色随屏显示器

| INVERT<br>BIT<br>DMM[3] | MODE AND LOCAL<br>NTROL BIT (LBC) = 0 | INTERNAL SYNC<br>BACKGROUND CON | MODE OR LOCAL<br>ITROL BIT (LBC) = 1 |

|-------------------------|---------------------------------------|---------------------------------|--------------------------------------|

| 0                       |                                       |                                 |                                      |

| 1                       |                                       |                                 |                                      |

图24. 字符属性位实例: 反色和本地背景控制

#### 表4. 字符背景控制

| SYNC MODE | BACKGROUND MODE,<br>VM1[7] | LOCAL BACKGROUND<br>CONTROL BIT, LBC<br>DMM[5], DMDI[7] | CHARACTER<br>BACKGROUND PIXEL |

|-----------|----------------------------|---------------------------------------------------------|-------------------------------|

|           | 0                          | 0                                                       | Input Video                   |

| External  | 0                          | 1                                                       | Gray                          |

| LAIGITIAI | 1                          | X                                                       | Gray                          |

| Internal  | X                          | X                                                       | Gray                          |

X =无关。

#### 显示存储器地址高位寄存器(DMAH)

写入该寄存器时,必须满足以下条件:

写地址 = 05H, 读地址 = 85H。

DMM[2] = 0,显示存储器没有处于清除过程。

读/写访问:无限制。

| BIT | DEFAULT | FUNCTION                                                                                                                                                                                                                                                                                           |  |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7–2 | 0000 00 | Don't Care                                                                                                                                                                                                                                                                                         |  |

| 1   | 0       | Byte Selection Bit This bit is valid only when in the 8-bit operation mode (DMM[6] = 1).  0 = Character Address byte is written to or read (DMDI[7:0] contains the Character Address byte).  1 = Character Attribute byte is written to or read (DMDI[7:0] contains the Character Attribute byte). |  |

| 0   | 0       | Display Memory Address Bit 8 This bit is the MSB of the display-memory address. The display-memory address sets the location of a character on the display (Figure 10). The lower order 8 bits of the display-memory address is found in DMAL[7:0].                                                |  |

#### 显示存储器地址低位寄存器(DMAL)

写入该寄存器时,必须满足以下条件:

写地址 = 06H, 读地址 = 86H。

DMM[2] = 0,显示存储器没有处于清除过程。

读/写访问:无限制。

| BIT | DEFAULT   | FUNCTION                                                                                                                                                                                                                               |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0 | 0000 0000 | Display Memory Address Bits 7–0 This byte is the lower 8 bits of the display-memory address. The display-memory address sets the location of a character on the display (Figure 10). The MSB of the display-memory address is DMAH[0]. |

# 集成了EEPROM的 单通道、单色随屏显示器

显示存储器数据输入寄存器(DMDI)

写入该寄存器时,必须满足以下条件:

写地址 = 07H, 读地址 = 87H。

DMM[2] = 0,显示存储器没有处于清除过程。

读/写访问:无限制。

| BIT | DEFAULT   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0 | 0000 0000 | Character Address or Character Attribute byte to be stored in the display memory.  8-Bit Operation Mode (DMM[6] = 1)  If DMAH[1] = 0, the content is to be interpreted as a Character Address byte, where Bits 7–0 = Character Address bits, CA[7:0] (Figure 12).  If DMAH[1] = 1, the content is to be interpreted as a Character Attribute byte where Bit 7 = Local Background Control bit, LBC (Figure 24 and Table 4)  Bit 6 = Blink bit, BLK  Bit 5 = Invert bit, INV (see Figure 24)  Bit 4–0 = 0  (The LBC, BLK, and INV bits are described in the Display Memory Mode register.)  16-Bit Operation Mode (DMM[6] = 0)  The content is always interpreted as a Character Address byte where bits 7–0 = CA[7:0] (Figure 12).  Auto-Increment Mode (DMM[0] = 1)  The character address CA[7:0] = FFH is reserved for use as an escape character that terminates the auto-increment mode. Therefore, the character located at address FFH is not available for writing to the display memory when in auto-increment mode. In all other modes, character FFH is available. |

#### 字符存储器模式寄存器(CMM)

写入该寄存器时,必须满足以下条件:

写地址 = 08H, 读地址 = 88H。

1) STAT[5] = 0, 字符存储器(NVM)不忙。

读/写访问:无限制。

2) VM0[3] = 0, OSD被禁止。

| BIT            | BIT DEFAULT FUNCTION     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |