特性

## 单诵道1-Wire 主控制器

## 概述

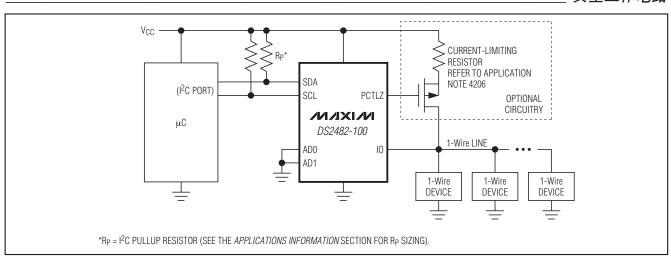

DS2482-100是I<sup>2</sup>C至1-Wire®的桥接器件,可直接与标准 (100kHz最大值)或快速(400kHz最大值)的I<sup>2</sup>C主机连接,完 成I<sup>2</sup>C主机和任意下游1-Wire从器件之间的双向协议转换。 相对于任何1-Wire从器件来说, DS2482-100则是一个 1-Wire主机。经过工厂校准的内部定时器将系统主处理器 从产生严格定时的1-Wire波形中释放出来,且同时支持标 准和高速的1-Wire通信速率。为了优化1-Wire波形的产生, DS2482-100在1-Wire的上升沿和下降沿进行了摆率控制, 且该器件具有可编程功能,以满足1-Wire从器件的驱动要 求。可编程的强上拉特性支持通过1-Wire总线向1-Wire从 器件供电,诸如EEPROM和传感器。DS2482-100将这些特 性整合在一起,并提供外部MOSFET控制,以满足强上拉 应用的要求。I<sup>2</sup>C从器件地址分配由2个二进制地址输入 控制,以解决系统中其它I2C从器件可能出现的地址冲突 问题。

应用

打印机 医疗仪器

工业传感器 蜂窝电话、PDA ◆ I<sup>2</sup>C主机接口,支持100kHz和400kHz I<sup>2</sup>C通信速率

- ◆ 1-Wire主控制器IO. 带有可选的有源或无源1-Wire上拉

- ◆ 提供复位/应答,八位、单位和三位1-Wire IO序列

- ◆ 标准和高速1-Wire通信速率

- ◆ 1-Wire边沿摆率控制

- ◆ 通过低阻信号路径提供1-Wire强上拉

- ◆ PCTLZ输出至可选控制外部MOSFET, 用于强上拉

- ◆ 两个地址输入引脚用于I<sup>2</sup>C地址分配

- ◆ 工作范围: 2.9V至5.5V, -40°C至+85°C

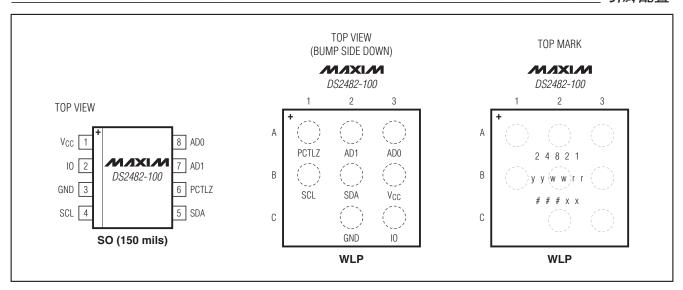

- ◆ 8引脚(150mil) SO封装、9焊球WLP封装

## 定购信息

| PART            | TEMP RANGE     | PIN-PACKAGE         |

|-----------------|----------------|---------------------|

| DS2482S-100+    | -40°C to +85°C | 8 SO (150 mils)     |

| DS2482S-100+T&R | -40°C to +85°C | 8 SO (150 mils)     |

| DS2482X-100+T   | -40°C to +85°C | 9 WLP (2.5k pieces) |

<sup>+</sup>表示无铅(Pb)/符合RoHS标准的封装。 T/T&R = 卷带包装。

引脚配置在数据资料的最后给出。

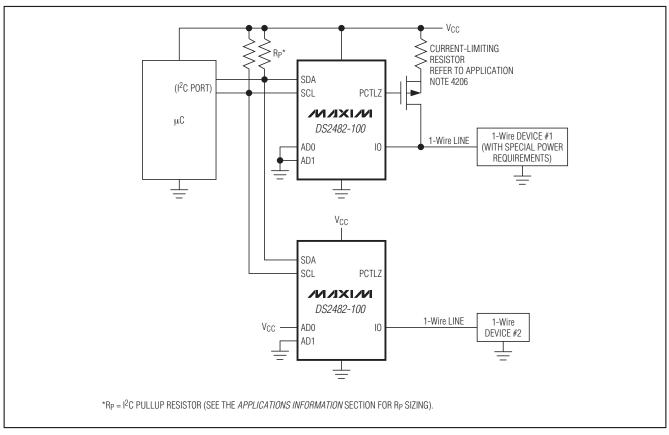

### 典型工作申路

1-Wire是Maxim Integrated Products, Inc.的注册商标。

MIXIM

Maxim Integrated Products 1

本文是英文数据资料的译文,文中可能存在翻译上的不准确或错误。如需进一步确认,请在您的设计中参考英文资料。 有关价格、供货及订购信息,请联络Maxim亚洲销售中心: 10800 852 1249 (北中国区), 10800 152 1249 (南中国区), 或访问Maxim的中文网站: china.maxim-ic.com。

## **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on Any Pin Relative to Ground0.5V to +6V | Junction Temperature+150°C                  |

|--------------------------------------------------------|---------------------------------------------|

| Maximum Current into Any Pin±20mA                      | Storage Temperature Range55°C to +125°C     |

| Operating Temperature Range40°C to +85°C               | Soldering TemperatureRefer to the IPC/JEDEC |

|                                                        | J-STD-020 Specification.                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 2.9V \text{ to } 5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                       | SYMBOL           | CONDITIONS                         | MIN  | TYP  | MAX  | UNITS  |  |

|---------------------------------|------------------|------------------------------------|------|------|------|--------|--|

| Owners had Market and           | M                | 3.3V                               | 2.9  | 3.3  | 3.7  |        |  |

| Supply Voltage                  | Vcc              | 5V                                 | 4.5  | 5.0  | 5.5  | V      |  |

| Operating Current               | Icc              | (Note 1)                           |      |      | 0.75 | mA     |  |

| 1-Wire Input High (Notes 2, 3)  | \/               | 3.3V                               | 1.9  |      |      | V      |  |

| 1-wire input High (Notes 2, 3)  | V <sub>IH1</sub> | 5V                                 | 3.4  |      |      | ]      |  |

| 1-Wire Input Low (Notes 2, 3)   | Vu               | 3.3V                               |      |      | 0.9  |        |  |

| 1-Wire Input Low (Notes 2, 3)   | V <sub>IL1</sub> | 5V                                 |      |      | 1.2  | ]      |  |

| 1-Wire Weak Pullup Resistor     | Rwpu             | (Note 4)                           | 1000 |      | 1675 | Ω      |  |

| 1-Wire Output Low               | V <sub>OL1</sub> | At 4mA load                        |      |      | 0.4  | V      |  |

| Active Pullup On Time           | t. 55.           | Standard                           | 2.3  | 2.5  | 2.7  | μs     |  |

| (Notes 4, 5)                    | tapuot           | Overdrive                          | 0.4  | 0.5  | 0.6  |        |  |

| Strong Pullup Voltage Drop      | 41/07000         | V <sub>CC</sub> ≥ 3.2V, 1.5mA load |      |      | 0.3  | V      |  |

|                                 | ΔVSTRPU          | V <sub>CC</sub> ≥ 5.2V, 3mA load   |      |      | 0.5  | ]      |  |

|                                 | PDsrc            | Standard (3.3V ±10%)               | 1    |      | 4.2  | - V/μs |  |

| Dulldown Clay Data (Note 6)     |                  | Overdrive (3.3V ±10%)              | 5    |      | 22.1 |        |  |

| Pulldown Slew Rate (Note 6)     |                  | Standard (5.0V ±10%)               | 2    |      | 6.5  |        |  |

|                                 |                  | Overdrive (5.0V ±10%)              | 10   |      | 40   |        |  |

|                                 |                  | Standard (3.3V ±10%)               | 0.8  |      | 4    | - V/μs |  |

| Pullup Slew Rate (Note 6)       | PUSRC            | Overdrive (3.3V ±10%)              | 2.7  |      | 20   |        |  |

| Fullup Siew Hate (Note 6)       | FUSRC            | Standard (5.0V ±10%)               | 1.3  |      | 6    |        |  |

|                                 |                  | Overdrive (5.0V ±10%)              | 3.4  |      | 31   |        |  |

| Power-On Reset Trip Point       | VPOR             |                                    |      |      | 2.2  | V      |  |

| 1-Wire TIMING (Note 5) (See Fig | ures 4, 5, and   | l 6)                               |      |      |      |        |  |

| Write-One/Read Low Time         | A                | Standard                           | 7.6  | 8    | 8.4  | μs     |  |

|                                 | t <sub>W1L</sub> | Overdrive                          | 0.9  | 1    | 1.1  |        |  |

| Pood Sample Time                | turon            | Standard                           | 13.3 | 14   | 15   | 0      |  |

| Read Sample Time                | tmsr             | Overdrive                          | 1.4  | 1.5  | 1.8  | μs     |  |

| 1-Wire Time Slot                | tour             | Standard                           | 65.8 | 69.3 | 72.8 | 0      |  |

| 1-vviile Tillille Silot         | tslot            | Overdrive                          | 9.9  | 10.5 | 11.0 | μs     |  |

|                                 | -                |                                    | -    |      |      |        |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 2.9V \text{ to } 5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                                                                                                                            | SYMBOL            | CONDITIONS                                 | MIN                       | TYP  | MAX    | UNITS |  |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------|---------------------------|------|--------|-------|--|

|                                                                                                                                      |                   | Standard (3.3V to 0V)                      | 0.54                      |      | 3.0    |       |  |

| Fall Time High-to-Low                                                                                                                |                   | Overdrive (3.3V to 0V)                     | 0.10                      |      | 0.59   |       |  |

| (Notes 6, 7)                                                                                                                         | tF1               | Standard (5.0V to 0V)                      | 0.55                      |      | 2.2    | μs    |  |

|                                                                                                                                      |                   | Overdrive (5.0V to 0V)                     | 0.09                      |      | 0.44   |       |  |

| Marita Zana Laur Tina                                                                                                                |                   | Standard                                   | 60                        | 64   | 68     |       |  |

| Write-Zero Low Time                                                                                                                  | twoL              | Overdrive                                  | 7.1                       | 7.5  | 7.9    | μs    |  |

| Maita Zana Danasana Tima                                                                                                             | 4                 | Standard                                   | 5.0                       | 5.3  | 5.6    |       |  |

| Write-Zero Recovery Time                                                                                                             | tREC0             | Overdrive                                  | 2.8                       | 3.0  | 3.2    | μs    |  |

| December Times                                                                                                                       |                   | Standard                                   | 570                       | 600  | 630    |       |  |

| Reset Low Time                                                                                                                       | t <sub>RSTL</sub> | Overdrive                                  | 68.4                      | 72   | 75.6   | μs    |  |

| D                                                                                                                                    |                   | Standard                                   | 66.5                      | 70   | 73.5   |       |  |

| Presence-Detect Sample Time                                                                                                          | tmsp              | Overdrive                                  | 7.1                       | 7.5  | 7.9    | μs    |  |

| Sampling for Short and Interrupt                                                                                                     |                   | Standard                                   | 7.6                       | 8    | 8.4    |       |  |

|                                                                                                                                      | tsı               | Overdrive                                  | 0.7                       | 0.75 | 0.8    | μs    |  |

| Decet High Time                                                                                                                      |                   | Standard                                   | 554.8                     | 584  | 613.2  |       |  |

| Reset High Time                                                                                                                      | trsth             | Overdrive                                  | 70.3                      | 74   | 77.7   | μs    |  |

| CONTROL PIN (PCTLZ)                                                                                                                  |                   | 1                                          | l .                       |      |        |       |  |

| Output Low Voltage                                                                                                                   | V <sub>OLP</sub>  | V <sub>CC</sub> = 2.9V, 1.2mA load current |                           |      | 0.4    | V     |  |

| Output High Voltage                                                                                                                  | VOHP              | 0.4mA load current                         | V <sub>CC</sub> - 0.5V    |      |        | V     |  |

| I <sup>2</sup> C PINS (SCL, SDA, AD0, AD1) (                                                                                         | Note 8) (See      | Figure 9)                                  | 0.01                      |      |        |       |  |

|                                                                                                                                      |                   |                                            |                           |      | 0.25 × |       |  |

|                                                                                                                                      | VIL               | $V_{CC} = 2.9V \text{ to } 3.7V$           | -0.5                      |      | Vcc    |       |  |

| Low-Level Input Voltage                                                                                                              |                   | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\     |                           |      | 0.22 × | \ \   |  |

|                                                                                                                                      |                   | V <sub>CC</sub> = 4.5V to 5.5V             | -0.5                      |      | VCC    |       |  |

| High-Level Input Voltage                                                                                                             | V <sub>IH</sub>   |                                            | 0.7 ×                     |      | VCC +  | V     |  |

| I ligh-Level input voltage                                                                                                           | VIH               |                                            | Vcc                       |      | 0.5V   | V     |  |

| Hysteresis of Schmitt Trigger Inputs                                                                                                 | VHYS              |                                            | 0.05 ×<br>V <sub>CC</sub> |      |        | V     |  |

| Low-Level Output Voltage at<br>3mA Sink Current                                                                                      | VoL               |                                            |                           |      | 0.4    | V     |  |

| Output Fall Time from V <sub>IH(MIN)</sub> to V <sub>IL(MAX)</sub> with a Bus Capacitance from 10pF to 400pF                         | tof               |                                            | 60                        |      | 250    | ns    |  |

| Pulse Width of Spikes That Are<br>Suppressed by the Input Filter                                                                     | tsp               | SDA and SCL pins only                      |                           |      | 50     | ns    |  |

| Input Current Each Input/Output<br>Pin with an Input Voltage<br>Between 0.1 x V <sub>CC(MAX)</sub> and<br>0.9 x V <sub>CC(MAX)</sub> | II                | (Notes 9, 10)                              | -10                       |      | +10    | μΑ    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 2.9V \text{ to } 5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                                                                                           | SYMBOL  | CONDITIONS     | MIN | TYP | MAX | UNITS |

|-----------------------------------------------------------------------------------------------------|---------|----------------|-----|-----|-----|-------|

| Input Capacitance                                                                                   | Cı      | (Note 9)       |     |     | 10  | рF    |

| SCL Clock Frequency                                                                                 | fSCL    |                | 0   |     | 400 | kHz   |

| Hold Time (Repeated) START<br>Condition (After this period, the<br>first clock pulse is generated.) | tHD:STA |                | 0.6 |     |     | μs    |

| Low Period of the SCL Clock                                                                         | tLOW    |                | 1.3 |     |     | μs    |

| High Period of the SCL Clock                                                                        | tHIGH   |                | 0.6 |     |     | μs    |

| Setup Time for a Repeated START Condition                                                           | tsu:sta |                | 0.6 |     |     | μs    |

| Data Hold Time                                                                                      | thd:dat | (Notes 11, 12) |     |     | 0.9 | μs    |

| Data Setup Time                                                                                     | tsu:dat | (Note 13)      | 250 |     |     | ns    |

| Setup Time for STOP Condition                                                                       | tsu:sto |                | 0.6 |     |     | μs    |

| Bus Free Time Between a STOP and START Condition                                                    | tBUF    |                | 1.3 |     |     | μs    |

| Capacitive Load for Each Bus Line                                                                   | СВ      | (Note 14)      |     |     | 400 | pF    |

| Oscillator Warmup Time                                                                              | toscwup | (Note 15)      |     |     | 100 | μs    |

- Note 1: Operating current with 1-Wire write-byte sequence followed by continuously reading the Status Register at 400kHz in overdrive.

- **Note 2:** With standard speed, the total capacitive load of the 1-Wire bus should not exceed 1nF. Otherwise, the passive pullup on threshold V<sub>IL1</sub> may not be reached in the available time. With overdrive speed, the capacitive load on the 1-Wire bus must not exceed 300pF.

- Note 3: Active pullup guaranteed to turn on between V<sub>IL1(MAX)</sub> and V<sub>IH1(MIN)</sub>.

- **Note 4:** Active or resistive pullup choice is configurable.

- **Note 5:** Except for t<sub>F1</sub>, all 1-Wire timing specifications and t<sub>APUOT</sub> are derived from the same timing circuit. Therefore, if one of these parameters is found to be off the typical value, it is safe to assume that all these parameters deviate from their typical value in the same direction and by the same degree.

- Note 6: These values apply at full load, i.e., 1nF at standard speed and 0.3nF at overdrive speed. For reduced load, the pulldown slew rate is slightly faster.

- Note 7: Fall time high-to-low (tF1) is derived from PDSRC, referenced from 0.9 x VCC to 0.1 x VCC.

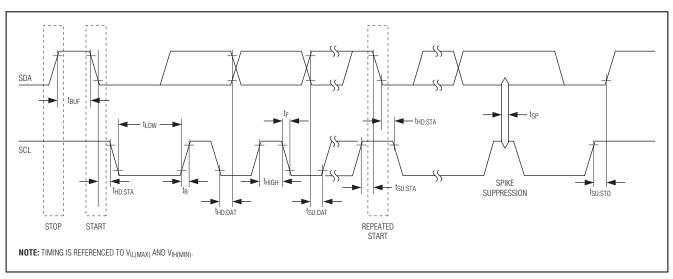

- **Note 8:** All I<sup>2</sup>C timing values are referred to V<sub>IH(MIN)</sub> and V<sub>IL(MAX)</sub> levels.

- Note 9: Applies to SDA, SCL, AD0 and AD1.

- Note 10: The input/output pins of the DS2482-100 do not obstruct the SDA and SCL lines if V<sub>CC</sub> is switched off.

- Note 11: The DS2482-100 provides a hold time of at least 300ns for the SDA signal (referred to the V<sub>IH(MIN)</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 12: The maximum t<sub>HD:DAT</sub> need only be met if the device does not stretch the low period (t<sub>LOW</sub>) of the SCL signal.

- Note 13: A fast-mode I<sup>2</sup>C bus device can be used in a standard-mode I<sup>2</sup>C bus system, but the requirement t<sub>SU:DAT</sub> ≥ 250ns must then be met. This is automatically the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line t<sub>R(MAX)</sub> + t<sub>SU:DAT</sub> = 1000 + 250 = 1250ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

- Note 14: C<sub>B</sub>—Total capacitance of one bus line in pF. If mixed with high-speed-mode devices, faster fall times according to *I*<sup>2</sup>*C*-*Bus Specification Version 2.1* are allowed.

- Note 15: 12C communication should not take place for the max to scwup time following a power-on reset.

引脚说明

| 引  | 引脚名称     |                 | 功能                                                                                   |  |  |  |  |  |

|----|----------|-----------------|--------------------------------------------------------------------------------------|--|--|--|--|--|

| so | WLP      | 1 台外            | 切能                                                                                   |  |  |  |  |  |

| 1  | В3       | V <sub>CC</sub> | 电源电压输入端。                                                                             |  |  |  |  |  |

| 2  | C3       | Ю               | 1-Wire输入/输出驱动。                                                                       |  |  |  |  |  |

| 3  | C2       | GND             | 参考地。                                                                                 |  |  |  |  |  |

| 4  | B1       | SCL             | I <sup>2</sup> C串行时钟输入。必须通过上拉电阻连接至V <sub>CC</sub> 。                                  |  |  |  |  |  |

| 5  | B2       | SDA             | I <sup>2</sup> C串行数据输入/输出。必须通过上拉电阻连接至V <sub>CC</sub> 。                               |  |  |  |  |  |

| 6  | A1       | PCTLZ           | 低电平有效控制输出,用于控制外部p沟道MOSFET,为1-Wire总线提供额外的电源,例如:为1-Wire 器件临时提供更大的电流。                   |  |  |  |  |  |

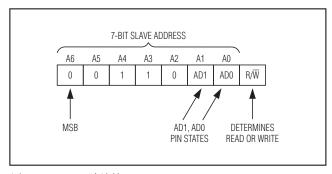

| 7  | A2       | AD1             | I <sup>2</sup> C地址输入端。必须连接至V <sub>CC</sub> 或GND。这些输入确定该器件的I <sup>2</sup> C从地址(参见图8)。 |  |  |  |  |  |

| 8  | 8 A3 AD0 |                 | 了「C地址個八洞。光水定读主 (C以UND。 A 三個八明是以做什的[C)(地址(多光图0)。                                      |  |  |  |  |  |

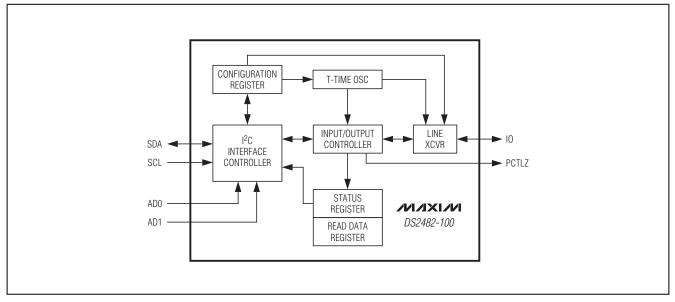

图1. 方框图

## 详细说明

DS2482-100是自定时1-Wire主机控制器,支持高级的1-Wire波形特性,包括标准和高速的速率、有源上拉和电源供电的强上拉。有源上拉影响1-Wire上的上升沿。强上拉功能与有源上拉采用同一上拉晶体管,但控制算法不同。此外,强上拉激活PCTLZ引脚,用于控制可选的外部电路,以便提供比片内上拉晶体管能力高的额外功率。一旦提供了命令和数据,DS2482-100的输入/输出控制器可实现严格定时的1-Wire通信功能,诸如复位/应答脉冲

检测周期、读字节、写字节、单个R/W位和三位一组的ROM搜索,而无需主机处理器参与。主机通过状态寄存器获得反馈(1-Wire功能完成状态、应答脉冲、1-Wire短路、选择的搜索路径),或通过读数据寄存器读取数据。DS2482-100可以通过I<sup>2</sup>C总线接口实现在标准模式或高速模式下与主机处理器的通信。两个地址引脚的逻辑状态确定DS2482-100的I<sup>2</sup>C从地址,允许最多4个器件工作在同一总线上,而无需网络集线器。图1所示为结构框图。

## 器件寄存器

DS2482-100有三个I<sup>2</sup>C主机读取的寄存器:配置寄存器、状态寄存器和读数据寄存器。通过读指针对这三个寄存器进行寻址。读指针的位置,也就是主机在随后的读访问中读取的寄存器是通过最后对DS2482-100执行的指令来定义的。主机通过读、写配置寄存器使能1-Wire总线功能。

#### 配置寄存器

DS2482-100可以通过配置寄存器使能或选择三个1-Wire功能,这些功能为:

- 有源上拉(APU)

- 强上拉(SPU)

- 1-Wire速率(1WS)

能以任何组合选择这些功能。APU和1WS能够保持其设定 状态,而SPU会在强上拉结束后返回至无效状态。

器件复位(重新上电或由Device Reset命令初始化)后,配置寄存器为00h。当对配置寄存器进行写操作时,只有高四位(第7位至第4位)是低四位(第3位至第0位)的反码时,才接受新的配置数据。当对配置寄存器进行读操作时,高四位保持为0h。

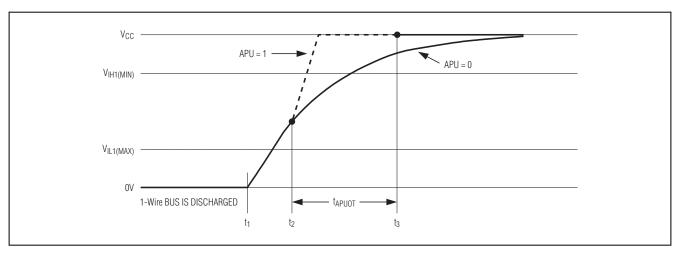

### 有源上拉(APU)

APU位控制由有源上拉(摆率受控的晶体管)还是由无源上拉(R<sub>WPU</sub>电阻)驱动1-Wire总线从低电平至高电平。当APU = 0时,禁止有源上拉(电阻模式)。除非1-Wire总线上仅连接了单个从机,否则应始终选择有源上拉。有源上拉并不作用于应答脉冲的上升沿或在1-Wire总线上出现短路后的恢复。

控制上升沿的电路(图2)工作过程如下:在 $t_1$ 时刻,下拉(从 DS2482-100或1-Wire从器件)结束。从这一时刻开始,1-Wire 总线通过DS2482-100内部的电阻RWPU被拉高。上拉斜率由  $V_{CC}$ 和1-Wire总线上的容性负载决定。如果有源上拉被禁止(APU = 0),电阻上拉继续工作,如实线所示。在有源上拉使能(APU = 1)条件下,当电压在 $t_2$ 时刻达到 $V_{IL1(MAX)}$ 和 $V_{IH1(MIN)}$ 之间时,DS2482-100采用受控的摆率有源拉高1-Wire总线,如虚线所示。继续有源上拉,直到在 $t_3$ 时刻达到 $t_{APUOT}$ 延时终止。在此之后,一直保持电阻上拉。保持上拉晶体管在超出 $t_3$ 时刻后导通的方法可参见强上拉(SPU)部分。

#### 配置寄存器位分配

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 1WS   | SPU   | 1     | ĀPŪ   | 1WS   | SPU   | 0     | APU   |

图2. 上升沿上拉

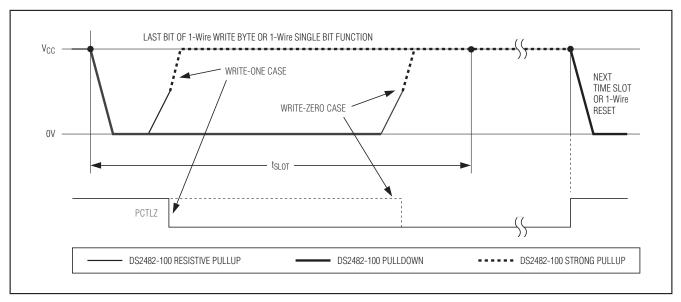

### 强上拉(SPU)

SPU位用于在1-Wire Write Byte命令或1-Wire Single Bit命令之前激活强上拉功能。在对1-Wire EEPROM器件执行复制暂存器数据到主存储器功能或进行SHA-1算法时,以及对寄生供电的温度传感器或A/D转换器操作时,通常需要强上拉特性。在对应的器件数据资料中规定了在通信协议中启用强上拉的位置。对于那些将1-Wire器件置于要求额外电源状态的命令,则必须在发出命令之前立即设置SPU位。强上拉与有源上拉采用相同的内部上拉晶体管。对于内部强上拉无法满足需求的情况,可用PCTLZ引脚控制外部p沟道MOSFET,以便为1-Wire总线提供超出DS2482-100驱动性能的额外电源。根据 Electrical Characteristics表中给出的 $\Delta V_{\rm STRPU}$ 参数,来判断内部强上拉是否足以驱动器件上的电路负载。

如果SPU为1, DS2482-100将在强上拉开始的那个时隙的上升沿施加有源上拉。然而,与有源上拉相比,强上拉(例如,内部上拉晶体管)保持导通,如图3所示,直到发生下来三种情况的任意一种:DS2482-100接收到产生1-Wire通信的命令(典型情况)、配置寄存器中的SPU位置

零或DS2482-100接收到Device Reset命令。只要强上拉保持有效,PCTLZ输出就为低电平。强上拉结束后,SPU位自动复位至0。采用强上拉功能不会改变配置寄存器中APU位的状态。

## 1-Wire速率(1WS)

1WS位决定DS2482-100产生的任意1-Wire通信的定时。所有的1-Wire从器件都支持标准速率(1WS = 0),其中在65μs内完成单个位(图3中的t<sub>SLOT</sub>)的传输。许多器件也能以较高的速率进行通信,称之为高速模式。为了从标准模式切换到高速模式,1-Wire器件则需要接受Overdrive-Skip ROM或Overdrive-Match ROM命令,如在1-Wire器件数据资料中说明的那样。1-Wire器件接受速率改变命令代码后,速率变换操作立即开始。DS2482-100必须参与这个速率变化以保持同步。在1-Wire字节命令之后立即将配置寄存器中1WS位写为1,来实现1-Wire器件速率的改变。将配置寄存器中的1WS位写为0,紧接着发送1-Wire Reset命令,则将改变DS2482-100和选通1-Wire总线上的任何1-Wire器件返回至标准速率。

图3. 低电阻上拉时序

#### 状态寄存器位分配

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DIR   | TSB   | SBR   | RST   | LL    | SD    | PPD   | 1WB   |

### 状态寄存器

只读状态寄存器用于DS2482-100向主处理器报告1-Wire总线的数据位类型、1-Wire忙状态和其自身复位状态等信息。所有的1-Wire通信命令和Device Reset命令都将读指针指向状态寄存器,以便主机处理器以最小的协议开销进行读取。仅在执行某些命令时,才更新状态寄存器中的内容。详细的内容请参见下面给出的各个状态位说明。

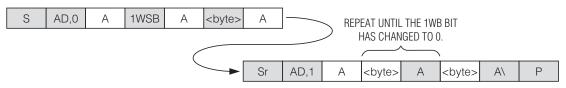

#### 1-Wire 作(1WB)

1WB位告知主处理器1-Wire总线是否处于忙状态。在1-Wire通信时,1WB为1;一旦命令执行完毕,1WB将返回其默认值0。1WB在何时改变状态以及保持为1状态的时间可详细参见功能命令部分。

#### 应答脉冲检测(PPD)

在每次1-Wire Reset命令之后将更新PPD位。如果在应答检测周期中,DS2482-100在 $t_{MSP}$ 时刻检测到1-Wire器件的应答脉冲,PPD位被设置为1。如果在随后的1-Wire Reset命令中,没有应答脉冲或1-Wire总线被短路,该位则返回为默认值0。

#### 短路检测(SD)

在每次1-Wire Reset命令之后将更新SD位。应答脉冲检测周期中,在t<sub>SI</sub>时刻,如果DS2482-100在1-Wire总线上检测为逻辑0,SD位则被设置为1。如果无短路存在,随后的1-Wire Reset命令可使该位返回至默认值0。如果SD为1时,那么PPD则为0。DS2482-100无法区分短路和DS1994或DS2404发送的1-Wire中断信号。由于这个原因,如果在这个应用中采用DS2404或DS1994,中断功能必须禁止。在相应的1-Wire器件数据资料中介绍了发送中断信号。

## 逻辑电平(LL)

LL位指示在没有进行任何1-Wire通信的情况下,选通1-Wire总线的逻辑状态。每次读取状态寄存器,1-Wire总线状态就被采样。当主机处理器以读模式寻址DS2482-100时(在应答周期内),将采样和更新LL位,前提是读指针指向状态寄存器。

### 器件复位(RST)

如果RST位为1,则DS2482-100执行了内部复位周期,可由上电复位引起也可从执行Device Reset命令开始。当DS2482-100执行Write Configuration命令,RST位自动清除,以保存所期望1-Wire特性的选择。

### 单个位结果(SBR)

SBR位告知1-Wire Single Bit命令在t<sub>MSR</sub>时刻采样有源1-Wire 总线的逻辑状态或1-Wire Triplet命令的第一位。SBR的上电默认值为0。如果1-Wire Single Bit命令发送0位,SBR则应该为0。在执行1-Wire Triplet命令时,SBR为0还是1,取决于所连接的1-Wire器件的响应。1-Wire Single Bit命令发送1位时,结果与此相同。

### 三位中的第二位(TSB)

TSB位表示1-Wire Triplet命令的第二位在t<sub>MSR</sub>时刻采样有源1-Wire总线的逻辑状态。TSB的上电默认值为0。仅在1-Wire Triplet命令时该位才更新,在其它命令时不起任何作用。

### 选择的搜索路径(DIR)

无论何时执行 1-Wire Triplet命令,该位将告知主机处理器 1-Wire Triplet命令中的第三位所选择的搜索路径。DIR的 上电默认值为0。仅在1-Wire Triplet命令时才更新该位,不受其它命令影响。更多信息请参见1-Wire Triplet命令和应用笔记187: 1-Wire搜索算法。

## 功能命令

DS2482-100接受8个功能命令,分为四个类型:器件控制、I<sup>2</sup>C通信、1-Wire设置和1-Wire通信。主机的反馈通道是由读指针控制,由每个功能命令自动设置,便于主机有效地访问相关的信息。主机处理器利用I<sup>2</sup>C接口以一个或两个字节的字符串发送这些命令和合适的参数。I<sup>2</sup>C协议要求每个字节都被接收单元应答,以确定接受,或者字节没有被确认则指示为错误状态(无效命令代码或参数),或结束通信。I<sup>2</sup>C协议细节,包括应答方式,请参见I<sup>2</sup>C接口部分。

### 功能命令如下所示:

- 1) 器件复位 (Device Reset)

- 5) 1-Wire单个位 (1-Wire Single Bit)

- 2) 设置读指针 (Set Read Pointer)

- 3) 写配置 (Write Configuration)

- 4) 1-Wire复位 (1-Wire Reset)

- 6) 1-Wire写字节 (1-Wire Write Byte)

- 7) 1-Wire读字节 (1-Wire Read Byte)

- 8) 1-Wire三重指令 (1-Wire Triplet)

## 表1. 有效的指针代码

| REGISTER SELECTION     | CODE |

|------------------------|------|

| Status Register        | F0h  |

| Read Data Register     | E1h  |

| Configuration Register | C3h  |

### 器件复位

| 命令代码      | F0h.                                |

|-----------|-------------------------------------|

| 命令参数      | 无。                                  |

| 说明        | 执行状态机逻辑的全局复位。终止任何正在进行的1-Wire通信。     |

| 典型应用      | 在上电后器件初始化,或按照所期望的重新初始化(复位)。         |

| 限制        | 无(可在任意时间内执行)。                       |

| 错误响应      | 无。                                  |

| 命令持续时间    | 最大时间为525ns,从命令代码应答位的SCL下降沿开始计时。     |

| 1-Wire有效性 | 最长需要262.5ns,在命令代码应答位的SCL下降沿后。       |

| 读指针位置     | 状态寄存器(适用于忙轮询)。                      |

| 受影响的状态位   | RST置为1; 1WB、PPD、SD、SBR、TSB、DIR设置为0。 |

| 受影响的配置位   | 1WS、APU、SPU置为0。                     |

## 设置读指针

| 命令代码      | E1h.                                 |

|-----------|--------------------------------------|

| 命令参数      | 指针代码(参见表1)。                          |

| 说明        | 设置读指针至指定寄存器。覆盖任何进程中1-Wire通信命令的读指针位置。 |

| 典型应用      | 准备读取1-Wire Read Byte命令的结果;寄存器的随机读取。  |

| 限制        | 无(可在任意时刻执行)。                         |

| 出错响应      | 如果指针代码无效,则指针代码不被应答,命令将忽略。            |

| 命令持续时间    | 无,在指针代码应答位的SCL上升沿,更新读指针。             |

| 1-Wire有效性 | 不受影响。                                |

| 读指针位置     | 如指针代码所指定。                            |

| 受影响的状态位   | 无。                                   |

| 受影响的配置位   | 无。                                   |

## 写配置

| 命令代码      | D2h.                                                                                             |

|-----------|--------------------------------------------------------------------------------------------------|

| 命令参数      | 配置字节。                                                                                            |

| 说明        | 写新配置字节。新的设置立即有效。 <b>注意</b> :在写人配置寄存器时,只有高四位(第7位至第4位)是低四位 (第3位至第0位)的反码时,才接受新数据。在读配置寄存器时,高四位一直为0h。 |

| 典型应用      | 定义下一个1-Wire通信特性。                                                                                 |

| 限制        | 在DS2482-100处理这个命令之前,1-Wire动作应该终止。                                                                |

| 出错响应      | 如果在接收命令代码时1WB=1,则命令代码和参数不被应答,该命令将被忽略。                                                            |

| 命令持续时间    | 无,在配置字节应答位的SCL上升沿,更新配置寄存器。                                                                       |

| 1-Wire有效性 | 无。                                                                                               |

| 读指针位置     | 配置寄存器(以校验写操作)。                                                                                   |

| 受影响的状态位   | RST设置为0。                                                                                         |

| 受影响的配置位   | 更新1WS、SPU、APU位。                                                                                  |

## 1-Wire复位

| 命令代码                                    | B4h.                                                                                                                                         |  |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 命令参数                                    | 无。                                                                                                                                           |  |  |

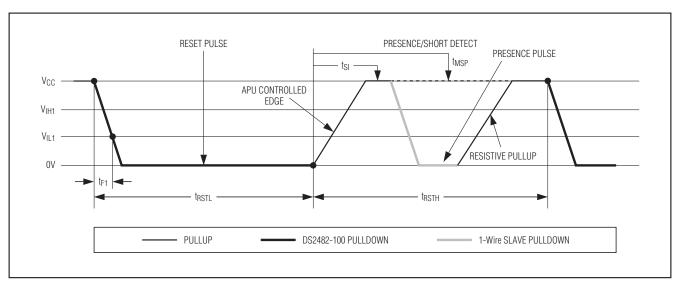

| 说明                                      | 在1-Wire总线上产生1-Wire复位/应答检测周期(图4)。在t <sub>SI</sub> 和t <sub>MSP</sub> 时刻采样1-Wire总线的状态,并通过状态寄存器PPD和SD位将结果告知主处理器。                                 |  |  |

| 典型应用                                    | 开始或结束任意1-Wire通信时序。                                                                                                                           |  |  |

| 限制                                      | 在DS2482-100处理这个命令之前,1-Wire动作应该终止。                                                                                                            |  |  |

| 出错响应 如果在接收命令代码时1WB=1,则命令代码不被应答,该命令将被忽略。 |                                                                                                                                              |  |  |

| 命令持续时间                                  |                                                                                                                                              |  |  |

| 1-Wire有效性                               | 在命令代码的应答位的SCL下降沿之后,最长需要262.5ns。                                                                                                              |  |  |

| 读指针位置                                   | 状态寄存器(用于轮询忙操作)。                                                                                                                              |  |  |

| 受影响的状态位                                 | 1WB (t <sub>RSTL</sub> + t <sub>RSTH</sub> 时设置为1); t <sub>RSTL</sub> + t <sub>MSP</sub> 时,更新PPD;在t <sub>RSTL</sub> + t <sub>SI</sub> 时,更新SD。 |  |  |

| 受影响的配置位                                 | 更新1WS、APU位。                                                                                                                                  |  |  |

1-Wire单个位

| 命令代码                                          | 87h.                                                                                                                                                                               |  |  |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 命令参数                                          | 位字节。                                                                                                                                                                               |  |  |

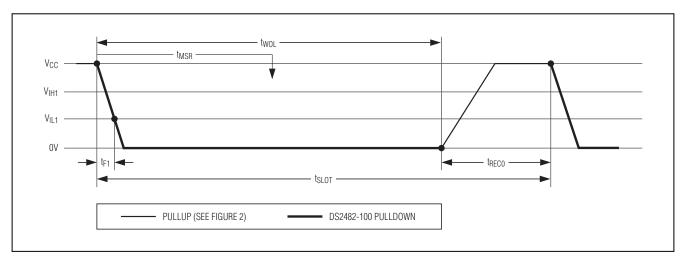

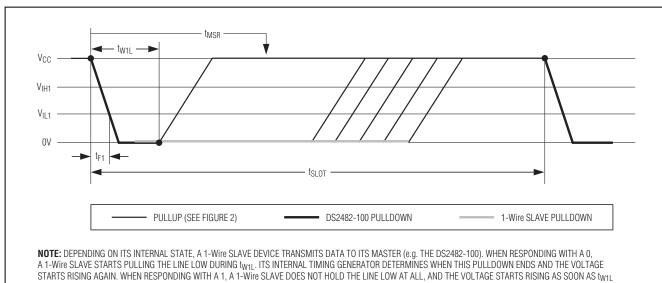

| 说明                                            | 产生单个1-Wire时隙, $1$ 位数值为"V",与 $1$ -Wire线上的位字节规定相同(参见表 $2$ )。V值为 $0$ b时产生一个写 $0$ 时隙(图 $5$ );V值为 $1$ b时产生一个写 $1$ 时隙,也可作为读数据时隙(图 $6$ )。在任意两种状态中,在 $1$ MSR时刻采样 $1$ -Wire总线上的逻辑电平,并更新SBR。 |  |  |

| 典型应用 当必须进行单个位通信时(有例外),以便在1-Wire线上执行单个位的写或读操作。 |                                                                                                                                                                                    |  |  |

| 限制                                            | 在DS2482-100处理这个命令之前,1-Wire动作应该终止。                                                                                                                                                  |  |  |

| 出错响应                                          | 如果在接收命令代码时1WB = 1,则命令代码和位字节不被应答,该命令将被忽略。                                                                                                                                           |  |  |

| 命令持续时间                                        | t <sub>SLOT</sub> + 最大时间262.5ns,从位字节的第一位(MSB)的SCL下降沿开始计时。                                                                                                                          |  |  |

| 1-Wire有效性                                     | 在位字节的MSB位的SCL下降沿之后,最长需要262.5ns。                                                                                                                                                    |  |  |

| 读指针位置                                         | 状态寄存器(用于轮询忙和读数据操作)。                                                                                                                                                                |  |  |

| 受影响的状态位                                       | 1WB (t <sub>SLOT</sub> 期间设置为1);在t <sub>MSR</sub> 时,更新SBR;DIR (可以改变其状态)。                                                                                                            |  |  |

| 受影响的配置位                                       | 更新1WS、APU、SPU位。                                                                                                                                                                    |  |  |

## 表2. 位字节的位分配

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| V     | ×     | ×     | X     | ×     | X     | X     | Х     |

x = 无关。

图4. 1-Wire复位/应答检测周期

图5. 写0时隙

STARTS RISING AGAIN. WHEN RESPONDING WITH A 1, A 1-Wire SLAVE DOES NOT HOLD THE LINE LOW AT ALL, AND THE VOLTAGE STARTS RISING AS SOON AS twil IS OVER. 1-Wire DEVICE DATA SHEETS USE THE TERM t<sub>RL</sub> INSTEAD OF t<sub>W1L</sub> TO DESCRIBE A READ-DATA TIME SLOT. TECHNICALLY, t<sub>RL</sub> AND t<sub>W1L</sub> HAVE IDENTICAL SPECIFICATIONS AND CANNOT BE DISTINGUISHED FROM EACH OTHER.

图6. 写1和读数据时隙

## 1-Wire写字节

|           | , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                                                                                              |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 命令代码      | A5h.                                                                                                                                                                 |

| 命令参数      | 数据字节。                                                                                                                                                                |

| 说明        | 写单个数据字节至1-Wire线。                                                                                                                                                     |

| 典型应用      | 向1-Wire线写人命令或数据;相当于执行8个1-Wire Single Bit命令,但由于更少的I <sup>2</sup> C通信而速度更快。                                                                                            |

| 限制        | 在DS2482-100处理这个命令之前,1-Wire动作应该终止。                                                                                                                                    |

| 出错响应      | 如果在接收命令代码时1WB = 1,则命令代码和数据字节不被应答,该命令将被忽略。                                                                                                                            |

| 命令持续时间    | 8 x t <sub>SLOT</sub> + 最大时间262.5ns, 从数据字节的最后一位(LSB)的下降沿开始计时。                                                                                                        |

| 1-Wire有效性 | 数据字节LSB位的SCL下降沿后,最长需要262.5ns (例如,在数据字节应答之前)。 <b>注意</b> : 在 $I^2$ C总线和在 $I$ -Wire总线的位次序不同( $I$ -Wire:LSB在前; $I^2$ C:MSB在前),因此,在DS2482-100接收全部数据字节之前,不能开始 $I$ -Wire动作。 |

| 读指针位置     | 状态寄存器(用于轮询忙操作)。                                                                                                                                                      |

| 受影响的状态位   | 1WB (8 x t <sub>SLOT</sub> 期间设置为1)。                                                                                                                                  |

| 受影响的配置位   | 更新1WS、SPU、APU位。                                                                                                                                                      |

## 1-Wire读字节

| 命令代码      | 96h.                                                                                               |

|-----------|----------------------------------------------------------------------------------------------------|

| 命令参数      | 无。                                                                                                 |

| 说明        | 在1-Wire总线产生8个读数据时隙,并将结果保存在读数据寄存器中。                                                                 |

| 典型应用      | 读取 $1$ -Wire总线上数据。相当于执行带有 $V=1$ (写 $1$ 时隙)的 $8$ 个 $1$ -Wire Single Bit命令,但由于减少了 $I^2$ C 通信,速度更快。   |

| 限制        | 在DS2482-100处理这个命令之前,1-Wire动作应该终止。                                                                  |

| 出错响应      | 如果在接收命令代码时1WB = 1,则命令代码不被应答,该命令将被忽略。                                                               |

| 命令持续时间    | 8 x t <sub>SLOT</sub> + 最大时间262.5ns, 从命令代码的应答位的SCL下降沿开始计时。                                         |

| 1-Wire有效性 | 在命令代码应答位的SCL下降沿后,最长需要262.5ns。                                                                      |

| 读指针位置     | 状态寄存器(用于轮询忙操作)。 <b>注意</b> : 从1-Wire线读取接收到的数据字节,发送Set Read Pointer命令和选择读数据寄存器,然后在读模式下,访问DS2482-100。 |

| 受影响的状态位   | 1WB (8 x t <sub>SLOT</sub> 期间设置为1)。                                                                |

| 受影响的配置位   | 更新1WS、APU。                                                                                         |

1-Wire三重指令

|                                                         | 1-44116二至月~                                                                                                                                                                                                                         |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 命令代码                                                    | 78h.                                                                                                                                                                                                                                |

| 命令参数                                                    | 方向字节。                                                                                                                                                                                                                               |

| 说明                                                      | 在1-Wire线上产生3个时隙: 2个读时隙和1个写时隙。写时隙的类型取决于读时隙的结果和方向字节。如果两个读时隙都为0 (典型状态),方向字节确定写时隙的类型。在这种状态下,如果 $V=1$ , DS2482-100产生写1时隙; $V=0$ , 则产生写0时隙,参见表3。如果读时隙为0和1时,紧跟着开始写0时隙。如果读时隙为1和0时,紧跟着开始写1时隙。如果读时隙为1和0时,紧跟着开始写1时隙。如果读时隙均为1 (错误状态),接下来的为写1时隙。 |

| 典型应用 执行一次1-Wire Search ROM时序,整个时序需要执行64次这个命令来识别和寻址到一个器件 |                                                                                                                                                                                                                                     |

| 限制                                                      | 在DS2482-100处理这个命令之前,1-Wire动作应该终止。                                                                                                                                                                                                   |

| 出错响应                                                    | 如果在接收命令代码时1WB = 1,则命令代码和方向字节不被应答,该命令将被忽略。                                                                                                                                                                                           |

| 命令持续时间                                                  | 3 x t <sub>SLOT</sub> + 最大时间262.5ns,从方向字节的第一位(MSB)的SCL下降沿开始计时。                                                                                                                                                                      |

| 1-Wire有效性                                               | 在方向字节MSB的SCL下降沿之后,最长需要262.5ns。                                                                                                                                                                                                      |

| 读指针位置                                                   | 状态寄存器(用于轮询忙操作)。                                                                                                                                                                                                                     |

| <b>受影响的状态位</b>                                          |                                                                                                                                                                                                                                     |

| 受影响的配置位                                                 | 更新1WS、APU。                                                                                                                                                                                                                          |

## 表3. 方向字节的位分配

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| V     | ×     | X     | X     | ×     | ×     | ×     | Х     |

x = 无关。

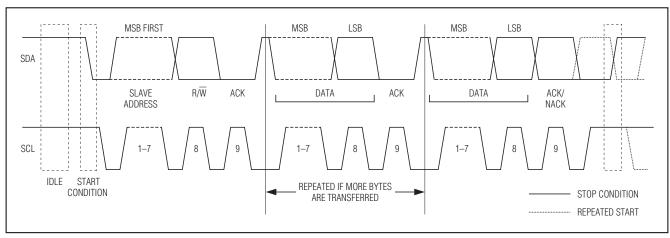

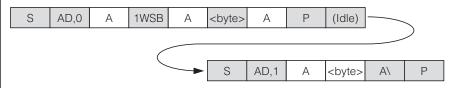

图7. I<sup>2</sup>C协议总结

## I<sup>2</sup>C接口

### 通用特性

I<sup>2</sup>C总线采用数据线(SDA)和时钟信号(SCL)进行通信。SDA和SCL都是双向线,通过上拉电阻连接到电源端正极。不进行通信时,这两条线为高电平。连接到总线的器件的输出级应该是漏极开路或集电极开路,来实现线与功能。I<sup>2</sup>C总线上的数据在标准模式下以高达100kbps的速率进行传输,而在快速模式下则以高达400kbps的速率进行传输。DS2482-100可在两种模式下工作。

总线上发送数据的器件作为发送器,而接收数据的器件 作为接收器。控制通信的器件称之为主机。主机控制的 器件为从机。为了能被主机独立的访问,每一个器件都 应该有从机地址,以便不会与总线的其他器件发生冲突。

总线只有在空闲时,才有可能传送数据。主机产生连续的时钟(SCL)信号,控制总线访问,产生START和STOP条件,并确定START和STOP(图7)之间所传送的数据字节的个数。数据以字节传送,最高有效位在前。在每个字节的后面紧跟一个应答位,使得主机与从机保持同步。

## 从地址

DS2482-100所响应的从机地址如图8所示。地址引脚AD0和AD1的逻辑状态确定了地址位A0和A1的值。地址引脚允许器件可以响应4个从器件地址中的一个地址。从器件地址是从器件寻址/控制字节的一部分。从器件寻址/控制字节的最后一位(R/W)被定义为数据方向。当设置为0时,接下来的数据从主机到从机传输(写访问)。当设置为1时,从从机到主机进行传输数据(读访问)。

图8. DS2482-100从地址

图9. I<sup>2</sup>C时序图

I<sup>2</sup>C定义

下面的术语通常是用来描述I<sup>2</sup>C数据传输。在图9中定义时序参考。

**总线空闲或不忙**: SDA和SCL均为无效状态和处于其逻辑高状态。

START条件: 为了启动与从器件的通信, 主机必须产生一个START条件。SCL保持高电平期间, SDA从高变化为低作为START条件。

STOP条件: 为了结束与从器件的通信, 主机必须产生 一个STOP条件。SCL保持高电平期间, SDA从低变化 至高作为STOP条件。

**重复START条件**: 重复START条件一般应用于读操作,选择指定的数据源或读取的地址。在数据传输结束时,主机使用重复START条件,紧跟在当前数据之后,立即开始新的数据传输。产生重复START条件与产生一般的START条件方式相同,只是在STOP条件后,无需保留总线为空闲状态而已。

数据有效:除START和STOP条件外,SDA变化仅可能在SCL为低电平时进行。在SCL的整个高电平脉冲和所需的启动与保持时间(SCL下降沿之后的t<sub>HD:DAT</sub>和SCL上升沿之前的t<sub>SU:DAT</sub>,如图9所示)期间,SDA上的数据必须保持有效不变。每一位数据要求一个时钟脉冲。在SCL的上升沿,数据移入到接收器中。

写操作结束时,主机必须释放SDA线,以便在下一个SCL的上升沿之前有足够的启动时间(最小值为: t<sub>SU:DAT</sub> + t<sub>R</sub>,参见图9)开始读取数据。在SDA线的前一个SCL脉冲的下降沿,从器件移出每个数据位。在当前SCL脉冲的上升沿,数据位有效。主机产生所有的SCL时钟信号,包括那些需要从从器件读取的脉冲。

应答信号:通常,当寻址某个接收器件时,在收到每一个字节后要求产生应答信号。主机必须产生一个与这个应答位相关的脉冲。在应答脉冲期间,应答器件必须以这种方式拉低SDA,即在相关的应答脉冲高电平时间加上所需的建立和保持时间(SCL的下降沿后的thD:DAT和SCL上升沿之前的tsU:DAT)期间,SDA 处于稳定的低电平。

从器件不应答:从器件可能不能接收或传输数据,例如,由于该器件忙于执行某些实时功能。在这种情况下,从器件不会应答其从地址,SDA线一直为高电平。做好通信准备的从器件将至少应答其从器件的地址。然而,有时从器件可能拒绝接受数据,例如无效的命令代码或参数。在这种状态下,从器件对所拒绝接收的任何字节不进行应答,并保持SDA线为高电平。在上述任意两种状态下,从器件应答失败后,主机首先需要产生一个重复START条件或在STOP条件之后产生一个START条件,以开始传输新的数据。

I<sup>2</sup>C通信实例

**主机不应答**:有时接收数据时,主机必须向从器件发送一个数据终止信号。为了获得这个信号,主机不应答所接收的由从器件发送的最后一个字节。作为响应,从器件释放SDA,允许主机产生STOP条件。

### 写入DS2482-100

为了对DS2482-100进行写操作,主机必须以写模式访问从器件,即发送从器件地址时必须将方向位设置为0。发送的下一个字节为命令代码,可能还紧跟一个命令参数,这取决于命令。DS2482-100将应答有效命令代码和所期望的/有效的命令参数,而额外的字节或无效命令参数不被应答。

### 读取DS2482-100

为了读取DS2482-100, 主机必须以读模式访问从器件。也就是说,发送从器件地址时必须将方向位设置为1。读指针确定了主机从哪个寄存器开始读取。主机可能重复的读取同一个寄存器,而无需重新设置地址,例如查看1WB从1至0的变化。读取不同的寄存器,主机必须发送Set Read Pointer命令,然后再以读模式访问DS2482-100。

I<sup>2</sup>C通信图表和数据方向标识可分别参见表4和表5。

## 表4. I2C通信—图表

| SYMBOL        | DESCRIPTION                        |

|---------------|------------------------------------|

| S             | START Condition                    |

| AD, 0         | Select DS2482-100 for Write Access |

| AD, 1         | Select DS2482-100 for Read Access  |

| Sr            | Repeated START Condition           |

| Р             | STOP Condition                     |

| А             | Acknowledged                       |

| Α\            | Not Acknowledged                   |

| (Idle)        | Bus Not Busy                       |

| <byte></byte> | Transfer of One Byte               |

| DRST          | Command "Device Reset", F0h        |

| SRP           | Command "Set Read Pointer", E1h    |

| WCFG          | Command "Write Configuration", D2h |

| 1WRS          | Command "1-Wire Reset", B4h        |

| 1WSB          | Command "1-Wire Single Bit", 87h   |

| 1WWB          | Command "1-Wire Write Byte", A5h   |

| 1WRB          | Command "1-Wire Read Byte", 96h    |

| 1WT           | Command "1-Wire Triplet", 78h      |

## 表5. 数据方向标识

| Master-to-Slave | Slave-to-Master |

|-----------------|-----------------|

|                 |                 |

Case C: 1-Wire Busy (1WB = 1)

1WRS

AD.0

I<sup>2</sup>C通信实例(续)

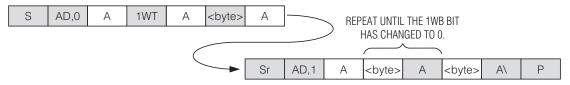

#### **Device Reset (After Power-Up)** S AD.0 DRST AD,1 Ρ Α <byte> A١ Activities that are underlined denote an optional read access to verify the success of the command. **Set Read Pointer (To Read from Another Register)** Case A: Valid Read Pointer Code SRP Р S AD,0 Α C3h Α C3h is the valid read pointer code for the Configuration Register. Case B: Invalid Read Pointer Code SRP Ρ AD,0 Α E5h A١ E5h is an invalid read pointer code. **Write Configuration (Before Starting 1-Wire Activity)** Case A: 1-Wire Idle (1WB = 0)AD.0 WCFG <byte> AD,1 <byte> Activities that are underlined denote an optional read access to verify the success of the command. Case B: 1-Wire Busy (1WB = 1) S AD,0 Α WCFG A١ The master should stop and restart as soon as the DS2482-100 does not acknowledge the command code. 1-Wire Reset (To Begin or End 1-Wire Communication) Case A: 1-Wire Idle (1WB = 0), No Busy Polling to Read the Result AD,0 1WRS (Idle) AD.1 <byte> In the first cycle, the master sends the command. Then the master waits (Idle) for the 1-Wire reset to complete. In the second cycle, the DS2482-100 is accessed to read the result of the 1-Wire reset from the Status Register. Case B: 1-Wire Idle (1WB = 0), Busy Polling Until the 1-Wire Command is Completed, then Read the Result 1WRS AD.0 AD.1 <bvte> <byte> REPEAT UNTIL THE 1WB BIT HAS CHANGED TO 0.

18 \_\_\_\_\_\_\_ **/I**/**X**|//I

The master should stop and restart as soon as the DS2482-100 does not acknowledge the command code.

I<sup>2</sup>C通信实例(续)

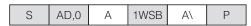

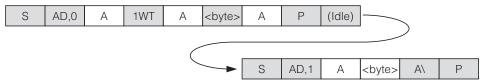

### 1-Wire Single Bit (To Generate a Single Time Slot on the 1-Wire Line)

Case A: 1-Wire Idle (1WB = 0), No Busy Polling

The idle time is needed for the 1-Wire function to complete. Then access the device in read mode to get the result from the 1-Wire Single Bit command.

Case B: 1-Wire Idle (1WB = 0), Busy Polling Until the 1-Wire Command is Completed

When 1WB has changed from 1 to 0, the Status Register holds the valid result of the 1-Wire Single Bit command.

Case C: 1-Wire Busy (1WB = 1)

The master should stop and restart as soon as the DS2482-100 does not acknowledge the command code.

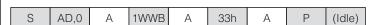

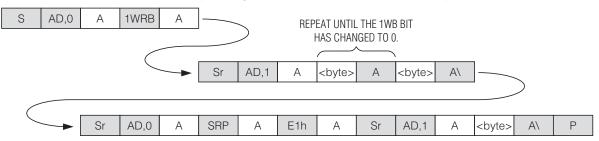

### 1-Wire Write Byte (To Send a Command Code to the 1-Wire Line)

Case A: 1-Wire Idle (1WB = 0), No Busy Polling

33h is the valid 1-Wire ROM function command for Read ROM. The idle time is needed for the 1-Wire function to complete. There is no data read back from the 1-Wire line with this command.

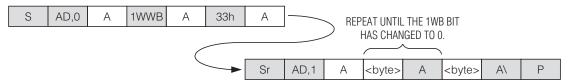

Case B: 1-Wire Idle (1WB = 0), Busy Polling Until the 1-Wire Command is Completed.

When 1WB has changed from 1 to 0, the 1-Wire Write Byte command is completed.

Case C: 1-Wire Busy (1WB = 1)

The master should stop and restart as soon as the DS2482-100 does not acknowledge the command code.

I<sup>2</sup>C通信实例(续)

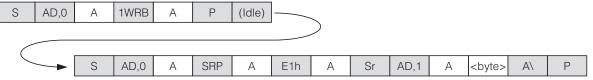

### 1-Wire Read Byte (To Read a Byte from the 1-Wire Line)

Case A: 1-Wire Idle (1WB = 0), No Busy Polling, Set Read Pointer After Idle Time

The idle time is needed for the 1-Wire function to complete. Then set the read pointer to the Read Data Register (code E1h) and access the device again to read the data byte that was obtained from the 1-Wire line.

Case B: 1-Wire Idle (1WB = 0), No Busy Polling, Set Read Pointer Before Idle Time

The read pointer is set to the Read Data Register (code E1h) while the 1-Wire Read Byte command is still in progress. Then, after the 1-Wire function is completed, the device is accessed to read the data byte that was obtained from the 1-Wire line.

Case C: 1-Wire Idle (1WB = 0), Busy Polling Until the 1-Wire Command is Completed

Poll the Status Register until the 1WB bit has changed from 1 to 0. Then set the read pointer to the Read Data Register (code E1h) and access the device again to read the data byte that was obtained from the 1-Wire line.

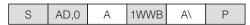

Case D: 1-Wire Busy (1WB = 1)

S AD,0 A 1WRB A\ P

The master should stop and restart as soon as the DS2482-100 does not acknowledge the command code.

I<sup>2</sup>C通信实例(续)

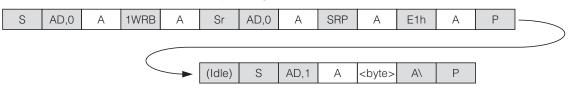

### 1-Wire Triplet (To Perform a Search ROM Function on the 1-Wire Line)

Case A: 1-Wire Idle (1WB = 0), No Busy Polling

The idle time is needed for the 1-Wire function to complete. Then access the device in read mode to get the result from the 1-Wire Triplet command.

Case B: 1-Wire Idle (1WB = 0), Busy Polling Until the 1-Wire Command is Completed

When 1WB has changed from 1 to 0, the Status Register holds the valid result of the 1-Wire Triplet command.

Case C: 1-Wire Busy (1WB = 1)

The master should stop and restart as soon as the DS2482-100 does not acknowledge the command code.

### 应用信息

### SDA和SCL上拉电阻

SDA是DS2482-100的漏极开路输出,需要一个上拉电阻来实现高逻辑电平。因为DS2482-100仅使用SCL作为输入(无时钟扩展),因此主机可以通过带有上拉电阻的漏极/集电极开路输出,或推挽式输出驱动SCL。

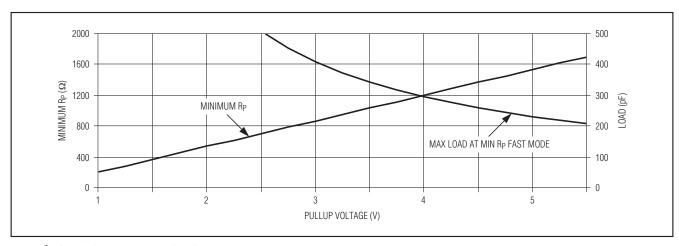

#### 上拉电阻RP的大小

根据 $I^2C$ 的指标,在 $V_{OL}$ 为0.4V时,从器件必须能够吸入至少3mA的电流。这个直流状态确定了上拉电阻的最小值:

$$R_{P(MIN)} = (V_{CC} - 0.4V)/3mA$$

采用5.5V的工作电压,上拉电阻的最小值为1.7k $\Omega$ 。如图 11所示的"MINIMUM  $R_P$ "曲线表示了最小上拉电阻与工作电压之间的变化关系。

对于 $I^2$ C系统,从上拉电压的30%到上拉电压的70%来测量上升时间和下降时间。最大容量的总线电容 $C_B$ 为400pF。

标准模式下,最大上升时间不能超过1000ns; 而在高速模式下,则不能超过300ns。假定以最大的上升时间计算,在所给定的电容 $C_R$ 下最大的电阻值计算为:

R<sub>PMAXS</sub> = 1000ns/[C<sub>B</sub> x ln(7/3)] (标准模式)

R<sub>PMAXF</sub> = 300ns/[C<sub>B</sub> x ln(7/3)] (高速模式)

对于400pF的总线电容而言,标准模式下,最大上拉电阻 为2.95kΩ,而在高速模式下,则为885Ω。1.7kΩ和2.95kΩ 之间的电阻值可以满足标准模式下的所有要求。

由于上拉电阻为885 $\Omega$ ,需要可以满足在高速和400pF总线电容下的上升时间的指标。885 $\Omega$ 上拉电阻比在5.5V下要求的 $R_{P(MIN)}$ 要低,因此必须找出另一种方法。首先计算在任何给定的工作电压("MINIMUM  $R_P$ "曲线)下的最小上拉电阻,接着再计算产生300ns的上升时间各自对应的总线电容,就可成生如图11所示的"MAX LOAD AT MIN  $R_P$  FAST MODE"线。

对于3V或更低的上拉电压而言,能够允许400pF的总线电容负载。而对于4V或更低的上拉电压来说,能接受300pF或更低的总线电容负载。对于高速模式下的任何上拉电

压,总线电容不能超过200pF。"MINIMUM  $R_P$ "曲线表示了各种电压下对应的上拉电阻值。

图10. 应用电路示意图

图11. I<sup>2</sup>C高速模式下的上拉电阻选择曲线

## 引脚配置

## 封装信息

如需最近的封装外形信息和焊盘布局,请查询 <u>china.maxim-ic.com/packages</u>。

| 封装类型          | 封装编码    | 文档编号           |

|---------------|---------|----------------|

| 8 SO (150mil) | S8+4    | <u>21-0041</u> |

| 9 WLP         | W92A1+1 | 21-0067        |

修订历史

| 修订次数 | 修订日期   | 修订日期 说明                                                               |                                  |

|------|--------|-----------------------------------------------------------------------|----------------------------------|

|      |        | 更新了特性部分。                                                              | 1                                |

|      |        | 更新了Electrical Characteristics表中V <sub>IL1</sub> 和R <sub>WPU</sub> 的值。 | 2                                |

| 5    | 061208 | 图1略有改动;更新了 <i>详细说明</i> 部分,以明确有关有源上拉和强上拉的信息。                           | 5                                |

|      |        | 更换了 <i>强上拉(SPU)</i> 部分的说明,并更换了图4。                                     | 7                                |

|      |        | 删除了图8中的时序错误。                                                          | 14                               |

| 6    | 7/08   | 采用新模板生成数据资料。                                                          | 所有                               |

| 6    |        | 更换图8。                                                                 | 16                               |

| 7    | 8/08   | 删除了典型工作电路和图11中的1-Wire端接电阻以及连接至该电阻的基准。                                 | 1, 23                            |

| 8    | 11/09  | ● 修正了有源上拉(APU)的推荐使用场合。<br>● 删除了应答脉冲屏蔽相关的内容。                           | 1–7, 9–12, 15, 16,<br>21, 22, 24 |

## Maxim北京办事处

北京 8328信箱 邮政编码 100083

免费电话: 800 810 0310 电话: 010-6211 5199 传真: 010-6211 5299

Maxim不对Maxim产品以外的任何电路使用负责,也不提供其专利许可。Maxim保留在任何时间、没有任何通报的前提下修改产品资料和规格的权利。

24 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600