低ドロップアウト・レギュレータ(LDO)は、広範な負荷電流と入力電圧で規定の出力電圧を維持し、入力電圧と出力電圧の差が非常に小さい電圧に対応します。入力電圧と出力電圧の差は、ドロップアウト電圧またはヘッドルーム条件といわれるものですが、2A時に80mVまで低くすることができます。出力を調整できる低ドロップアウト・レギュレータ(参考資料1)が注目されるようになったのは、1977年のことでした。現在は、20個もの低ドロップアウト・リニア・レギュレータを使用する携帯機器も珍しくありません。今日の携帯機器に搭載されているLDOの多くは、多機能のパワー・マネジメントIC(PMIC)に集積化されています。PMICは、オーディオ、バッテリ充電、ハウスキーピング、照明、通信、その他の機能のために20以上の電源からなる、高度に集積化されたシステムです。

しかし、携帯システムが急速に進化するにつれ、集積化PMICでは周辺機能の電源条件に対応できなくなってきました。カメラ・モジュール、Bluetooth、WiFi、その他のモジュールなどのオプション品目に電源を提供するためにシステム開発の後期の段階で専用のLDOを追加しなければなりません。LDOは、ノイズ低減のための応急処置として、あるいは電磁波妨害(EMI)やプリント回路基板(PCB)のパターン配線に起因する電圧レギュレーションの問題を解決するために、また不要な機能を切断してシステム効率を向上するためなどにも利用されます。

この記事では、基本的なLDOの構成について説明し、主要な仕様について解説するとともに、システムに低ドロップアウト・レギュレータを利用する方法を紹介します。アナログ・デバイセズのLDOファミリーの設計特性を例として使用します。

出力電圧を安定化します。

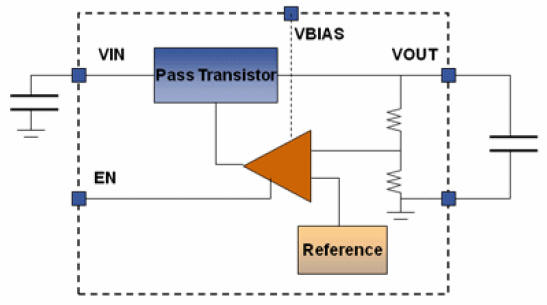

基本的なLDOアーキテクチャ。 LDOは図1に示すように、電圧リファレンス、誤差アンプ、帰還分圧器、パス・トランジスタで構成されています。出力電流は、パス・デバイスを経由して送られます。ゲート電圧は、誤差アンプが制御します。誤差アンプはリファレンス電圧と帰還電圧を比較し、その差を増幅して誤差電圧を小さくします。帰還電圧がリファレンス電圧よりも低ければ、パス・トランジスタのゲートが低くなり、オン抵抗が小さくなり、出力電圧が増加します。帰還電圧がリファレンス電圧よりも高い場合は、パス・トランジスタのゲートを高くし、オン抵抗を大きくして、出力電圧を小さくします。

このクローズド・ループ・システムの力学は、誤差アンプ/パス・トランジスタによって形成される内部の極と誤差アンプの出力インピーダンスと出力コンデンサの等価直列抵抗値(ESR)によって形成される外部の極という2つの極をベースとしています。出力容量とそのESRは、ループ安定性と、負荷電流のトランジェント変化に対する応答性に影響します。安定性を得るには、1Ω以下のESRを推奨します。さらに、ノイズをフィルタ処理し、負荷トランジェントを制御するために、LDOには入力コンデンサと出力コンデンサも必要です。コンデンサの容量を大きくすると、LDOのトランジェント応答性が改善されますが、スタートアップ時間が長くなります。アナログ・デバイセズのLDOは、指定されたコンデンサを使用する場合に規定の動作条件で安定性が得られるように設計されています。

LDOの効率。 設計エンジニアは、つねに効率の向上を追求しています。無負荷時電源電流(Iq)と順方向電圧降下を低減することによって、効率が向上します。

Iqが分母にあるため、Iqが増加するほど、効率が低下することが明らかです。今日のLDOはIqが十分低くなっているため、IqがILOADよりもはるかに小さい値であれば、Iqを無視することによって効率の計算を簡単にすることができます。この場合、LDOの効率は単純に(Vo/Vin)*100%になります。LDOには未使用エネルギーを保存しておく手段(スイッチング・レギュレータのインダクタなど)がないため、負荷に送られなかった電力はLDO内部で熱として消費されます。

負荷とラインの変動、周囲温度の変化、時間の経過に関わらず、安定した電源電圧を供給するLDOは、電源電圧と負荷電圧の差が小さいときに特に最も力を発揮します。たとえば、リチウムイオン・バッテリが4.2V(完全充電)から3.0V(放電)に降下しても、このバッテリに2.8VのLDOが接続されていれば、負荷が一定の2.8V(ドロップアウト電圧は200mV未満)に維持されます。その効率は、電池の満充電時は67%ですが、電池放電時(電池の電圧=3.0V時)には93%になります。

効率を改善するために、高効率のスイッチング・レギュレータによって生成される中間電圧レールにLDOを接続できます。たとえば、リチウム・バッテリから3.3Vを出力するスイッチング・レギュレータの場合は、スイッチング・レギュレータの効率を95%と仮定すると、LDOの効率は85%の一定値に維持され、システム全体の効率は81%になります。

LDOの性能を高める回路機能。 イネーブル入力によりLDOのターンオンとターンオフを外部から制御できるため、マルチレール・システムで正しい電源シーケンスを実行できます。ソフト・スタートで突入電流を制限し、パワーアップ時の出力電圧の立上がり時間を制御します。スリープ状態は、消費電力が最小限になり、同時に高速のターンオンが可能であるため、特にバッテリを使用するシステムで役に立ちます。サーマル・シャットダウンは、LDOの温度が規定値を超えるとLDOをターンオフします。過電流保護によってLDOの出力電流と消費電力が制限され、低電圧ロックアウト(UVLO)によって電源電圧が規定の値よりも低くなると出力がディセーブルになります。図2に、携帯型設計向けの代表的な電源システムの簡略図を示します。

リニア・レギュレータに必要な条件

デジタル負荷用のLDO: ADP170や ADP1706, ADP175xなどのデジタル負荷向けリニア・レギュレータは、一般にマイクロプロセッサ・コアとシステムの入出力回路などのシステムに必要な主要なデジタル条件に対応するように設計されています。DSPとマイクロコントローラ用のLDOは高い効率の動作が求められ、急速に変化する高い電流を処理しなければなりません。さらに最新のアプリケーションで要求される条件は、LDOに大きな負担となってきています。これは、省エネルギーのためにプロセッサ・コアがクロック速度を変化させていることが原因の一つです。ソフトウェアに導かれた負荷に応じてクロック速度が変動するために、LDOには高度な負荷レギュレーション能力が求められています。

デジタル負荷の重要な特性は、ラインと負荷のレギュレーション、ならびにトランジェントのアンダーシュートとオーバーシュートです。低電圧のマイクロプロセッサ・コアに電源を供給するには、高精度の出力コントロールがつねに非常に重要です。レギュレーションが不十分だと、コアがラッチアップする可能性があります。上記のパラメータは必ずしもデータシートに規定されているとは限らず、またトランジェント応答性のグラフのトランジェント信号に対応する立上がり速度と立下がり速度は甘い値が示されていることがあります。ラインと負荷のレギュレーションは、規定された負荷電流時における負荷の変動に対する出力電圧の偏差(%)か、実際の電圧/電流値、またはその両方で表されています。

エネルギーを節約するために、デジタルLDOはバッテリ寿命を延長する低いIqで設計されており、携帯システムはソフトウェアのアイドル時に長時間、低消費電力動作を行います。非アクティブ状態の間、システムはスリープ状態に入りますが、このときにLDOはシャットダウンし、消費電流を1μA以下に低減しなければなりません。LDOがスリープ・モードになっている間、バンドギャップ・リファレンスを含む回路のすべてがオフに切り替わります。システムがアクティブ・モードに復帰するときは、高速のターンオン時間が求められます。この間にデジタル電源電圧が過度にオーバーシュートすることがあってはなりません。過度のオーバーシュートはシステムのラッチアップを引き起こす可能性があり、場合によってはバッテリの取外しやマスター・リセット・ボタンの起動によって、問題を修正し、システムを再起動しなければならないことがあります。

アナログおよびRF負荷用のLDO: アナログ・デバイスはデジタル・デバイスよりもノイズの影響を受けやすいため、アナログ環境で使用するLDOには、 ADP121や ADP130, ADP150が提供する低ノイズと高い電源電圧変動除去(PSR)性能が重要になります。アナログLDOの必要条件の中心となるのは、ワイヤレス・インターフェース条件であり、「レシーバやトランスミッタに悪影響を及ぼさず、オーディオ・システムでポップ音やノイズを発生させない」ということになります。ワイヤレス接続はノイズの影響を非常に受けやすく、ノイズが信号に干渉すると、レシーバの効果が低下するおそれがあります。アナログIC向けリニア・レギュレータを検討する場合、前段の信号源と後段の負荷から発生するノイズをデバイスで抑制し、同時にそのことによってノイズを増やさないようにすることが大切です。

アナログ・レギュレータのノイズは、V rms、および上流のノイズを抑制する能力であるPSRによって測定します。外部フィルタやバイパス・コンデンサを追加することでノイズを低減できますが、コストやサイズが増加します。LDOの内部設計で細心の注意を払い、工夫することによって、ノイズの低減や電源ノイズの除去が可能です。LDOを選択する際には、各システムに必要な全体の性能に関連して製品の細部を見直すことが重要です。

主要なLDO仕様とその定義

注: メーカのデータシートの最初のページに記載されている仕様は、簡単な概要にすぎず、しかも多くの場合、デバイスの魅力的な特長を強調する目的で記述されています。主要なパラメータでは特に代表的な性能特性が紹介されていますが、これらの代表的な性能特性はデータシートの本文に記載されている仕様全体とその他のデータを参考にしなければよく理解できないことがあります。また、仕様の記述についてもメーカの間で標準化された方法がほとんどないため、電源設計者は電気的仕様の表に記載されている主要なパラメータを取得するために使用された定義と方法を理解する必要があります。システム設計者は、周囲温度やジャンクション温度の範囲、グラフ情報におけるX軸とY軸のスケール、負荷、トランジェント信号の立上がり時間と立下がり時間、帯域幅などの主要パラメータに十分注意しなければなりません。以下では、アナログ・デバイセズのLDOの特性評価とアプリケーションに関する重要なパラメータについて説明します。

入力電圧範囲: LDOの入力電圧範囲によって、使用可能な最低の入力電源電圧が決まります。仕様には広い入力電圧範囲が記載されている場合がありますが、最低の入力電圧はドロップアウト電圧と所望の出力電圧の合計値を上回らなければなりません。たとえば、150mVのドロップアウトは、安定化された2.8V出力を供給するために入力電圧が2.95Vよりも高くなければならないことを意味します。入力電圧が2.95Vよりも低くなると、出力電圧は2.8Vよりも低くなります。

グラウンド(無負荷時電源)電流: 無負荷時電源電流Iqは、規定された負荷電流で測定された入力電流IINと負荷電流IOUTの差です。固定電圧レギュレータの場合、Iqはグラウンド電流Igと同じです。ADP171などの可変電圧レギュレータの場合、無負荷時電源電流は外部の抵抗分圧ネットワークの電流をグラウンド電流から差し引いた値になります。

シャットダウン電流: デバイスがディセーブル状態のときに消費される入力電流。携帯機器用のLDOでは通常1.0μA以下ですが、この仕様は携帯機器がターンオフしている長いスタンバイ時間中にバッテリの充電寿命を維持するために重要です。

出力電圧精度: アナログ・デバイセズのLDOは、高い出力電圧精度が得られるように設計されており、工場出荷時に25℃時に±1%以内で調整されています。出力電圧精度は動作温度範囲、入力電圧範囲、負荷電流範囲で規定され、誤差は最悪時の±x%と規定されます。

ライン・レギュレーション: ライン・レギュレーションは、入力電圧の変化に対応する出力電圧の変化です。チップ温度の変化による誤差を防止するために、低消費電力の条件下またはパルス技法によって測定します。

ダイナミック負荷レギュレーション: 負荷電流が低速で変化する限り、大部分のLDOは出力電圧をほぼ一定に保持することができます。しかし、負荷電流が急速に変化すると、出力電圧が変化します。負荷電流の変化に伴って出力電圧がどの程度変化するかによって、負荷トランジェント性能が決まります。

ドロップアウト電圧: ドロップアウトは、レギュレーションを維持するために必要な入力電圧と出力電圧との最小差です。つまり、入力がある程度まで減少してもLDOは出力負荷電圧を一定に保持することができますが、入力が出力電圧とドロップアウト電圧の合計電圧まで達すると、出力はレギュレーションから「ドロップアウト」してしまいます。消費電力を最小にし、効率を最大限に高めるためにドロップアウト電圧をできる限り低くする必要があります。一般には、出力電圧がその公称値よりも100mV低い電圧に降下するとドロップアウトすると考えられています。負荷電流とジャンクション温度がドロップアウト電圧に影響を与えることがあります。そのため、最大ドロップアウト電圧は全動作温度範囲、全負荷電流範囲で規定されています。

スタートアップ時間: スタートアップ時間は、イネーブル信号の立上がりエッジからVOUTが公称値の90%に達するまでの時間と定義されています。このテストは通常、VINを印加し、イネーブル・ピンをオフからオンにトグルして実施します。ただし、イネーブル・ピンをVINに接続する場合は、バンドギャップ・リファレンスが安定するまでに時間がかかるため、スタートアップ時間が大幅に長くなることがあります。携帯システムで電力節約のためにレギュレータを頻繁にターンオフ/ターンオンするアプリケーションでは、レギュレータのスタートアップ時間を十分に考慮しなければなりません。

電流制限スレッショールド: 電流制限スレッショールドは、出力電圧が規定された代表値の90%に降下するときの負荷電流と定義されています。たとえば、3.0Vの出力電圧の電流制限値は、出力電圧を3.0Vの90%、つまり2.7Vに降下させる電流になります。

動作温度範囲: 動作温度範囲は、周囲温度とジャンクション温度によって規定することができます。LDOは熱を放散するため、ICはつねに周囲温度よりも高い温度で動作します。周囲温度をどの程度超えるかは、動作条件とPCボードの熱設計に応じて異なります。長期間にわたり最大ジャンクション温度を超える動作(平均故障時間MTTFとして統計的に規定)はデバイスの信頼性に悪影響を及ぼすと考えられるため、最大ジャンクション温度(TJ)が規定されています。

サーマル・シャットダウン(TSD): 大部分のLDOには、熱の放散からICを保護するためにシリコン・サーモスタットが備わっています。規定されたサーマル・シャットダウン・スレッショールドをジャンクション温度が超えると、これらのサーモスタットによってLDOがパワーダウンします。LDOを再起動するまでに冷却できるようにヒステリシスが必要です。TSDは、LDO以外の保護も行うために重要です。過剰な熱はレギュレータだけでなく他のものにも害を与えます。LDOからPCボード(またはボード上の高温素子からLDO)に伝導する熱は、時間の経過に伴ってPCボードの材料とハンダ接合部を損傷し、さらに周辺の部品を損傷するおそれもあり、これによって携帯機器の寿命が短くなります。また、サーマル・シャットダウンはシステムの信頼性にも影響します。したがって、ボード温度を制御するための熱設計(ヒート・シンクや冷却など)は、システムで考慮しなければならない重要な問題です。

イネーブル入力: 正と負のロジックで設定されるLDOイネーブルによって、デバイスがターンオン/オフします。アクティブ・ハイレベルのロジックでは、イネーブル電圧がロジック・ハイレベル・スレッショールドを超えるとデバイスがイネーブルになります。アクティブ・ローレベルのロジックでは、イネーブル電圧がロジック・ローレベル・スレッショールドを下回るとデバイスがイネーブルになります。イネーブル入力を用いて、LDOのターンオンとターンオフを外部から制御することができます。これは、マルチレール・システムにおける電源のシーケンシングで重要です。LDOによっては、LDOがディセーブルの間にバンドギャップ・リファレンスがオンになるため、スタートアップ時間を大幅に短くし、LDOの高速なターンオンが可能になるものもあります。

低電圧ロックアウト: 低電圧ロックアウト(UVLO)は、システムの入力電圧が規定のスレッショールドを超えた場合のみ電圧を負荷に供給するものです。UVLOは、デバイスの安定した動作のために必要な電圧に入力電圧が達していないと、デバイスがパワーオンしないようにするという点で重要です。

出力ノイズ: LDOの内部バンドギャップ電圧リファレンスはノイズ発生源であり、一般に特定の帯域幅範囲でμV rmsの単位で規定されています。たとえば、ADP150の出力ノイズはVOUTが1.2Vのときに10~100kHzの範囲で10μV rmsです。データシートの仕様を比較する際には、規定された帯域幅と動作条件が重要になります。

電源電圧変動除去: デシベル単位で表されるPSRは、広い周波数範囲(1~100kHz)で入力電源からのリップルをLDOがどの程度除去できるかを評価するときの目安になるものです。LDOでは、PSRを2つの周波数バンドで評価することができます。バンド1はDCから制御ループのユニティ・ゲイン周波数までの帯域であり、PSRはレギュレータのオープン・ループ・ゲインによって設定されます。バンド2はユニティ・ゲイン周波数を超える帯域であり、PSRは帰還ループによる影響を受けません。この場合、PSRは出力、および入力から出力ピンまでのリーク電流経路によって設定されます。適切な高い値の出力容量を選択すると、一般にバンド2のPSRが改善されます。バンド1では、アナログ・デバイセズが独自に開発した回路設計を使用すれば、入力電圧と負荷の変動によるPSRの変動が低減します。電源電圧変動除去を最適化するには、入力と出力間のリーク電流が低くなるようにPCボードのレイアウトを配慮し、グラウンド接続を耐久性が高いものにする必要があります。

最小入力/出力コンデンサ: 最小入力/出力コンデンサは、動作条件のすべて、特に動作電圧と温度の全範囲で規定値より大きくする必要があります。最小容量の仕様を確実に満たすには、デバイスを選ぶときにアプリケーションの動作条件の全範囲を検討しなければなりません。X7RとX5Rタイプのコンデンサを推奨します。Y5VおよびZ5Uのコンデンサは、LDOとの併用には推奨できません。

逆電流保護機能: PMOSパス・デバイスを備えた標準のLDOには、VINとVOUTの間に固有のボディ・ダイオードがあります。VINがVOUTよりも高くなると、このダイオードが逆バイアスされます。VOUTがVINよりも高くなると、固有ダイオードが順方向にバイアスし、VOUTからVINに電流が流れるため、破壊的な消費電力が生じる可能性があります。ADP1740/ADP1741などの一部のLDOには、VOUTからVINに流れる逆電流に対して保護するための回路が備わっています。逆電流保護回路はVOUTがVINよりも高くなると、これを検出し、固有ダイオードの接続方向を反転して、ダイオードを逆バイアスします。

ソフト・スタート: ソフト・スタートは、スタートアップ時の突入電流を低減したり、電圧シーケンシングを行う場合に役に立ちます。スタートアップ時の突入電流の制御が必要なアプリケーションでは、ADP1740/ADP1741などのLDOがプログラマブル・ソフト・スタート(SS)機能を提供します。ソフト・スタートを実行するには、小さいセラミック・コンデンサをSSとGND間に接続します。

結論

LDOは重要な機能を担います。コンセプトは単純ですが、LDOを使用するには考慮すしなければならない点がたくさんあります。この記事では、基本的なLDOの構成について考察し、主要な仕様について解説するとともに、システムに低ドロップアウト・レギュレータを使用する方法を紹介しました。データシートには、数多くの役に立つ情報が記載されています。詳細な情報(セレクション・ガイド、データシート、アプリケーション・ノート)のほか、問い合わせ先などについても、パワー・マネジメントウェブサイトをご覧ください。最高速、最高精度のDC/DC パワー・マネジメント設計ツール、ADIsimPowerTMも利用できます。

参考資料

1 R. Dobkin著「Break Loose from Fixed IC Regulators」Electronic Design、1977年4月12日号

2 http://www.analog.com/jp/power-management/multifunction-power-ics/products/index.html

3 http://www.analog.com/jp/power-management/linear-regulators/products/index.html

4 J. Patoux著「Low-Dropout Regulators」(アプリケーション・エンジニアへの質問 – 37)、アナログ・ダイアログ41-2(2007年)、8~10ページ

5 アナログ・デバイセズの全製品に関する情報は、 http://www.analog.com/jpをご覧ください。

6 http://www.analog.com/jp/power-management/products/index.html